Detailed Report on ARM Processor Architecture and its Usage

VerifiedAdded on 2023/06/11

|15

|1358

|343

Report

AI Summary

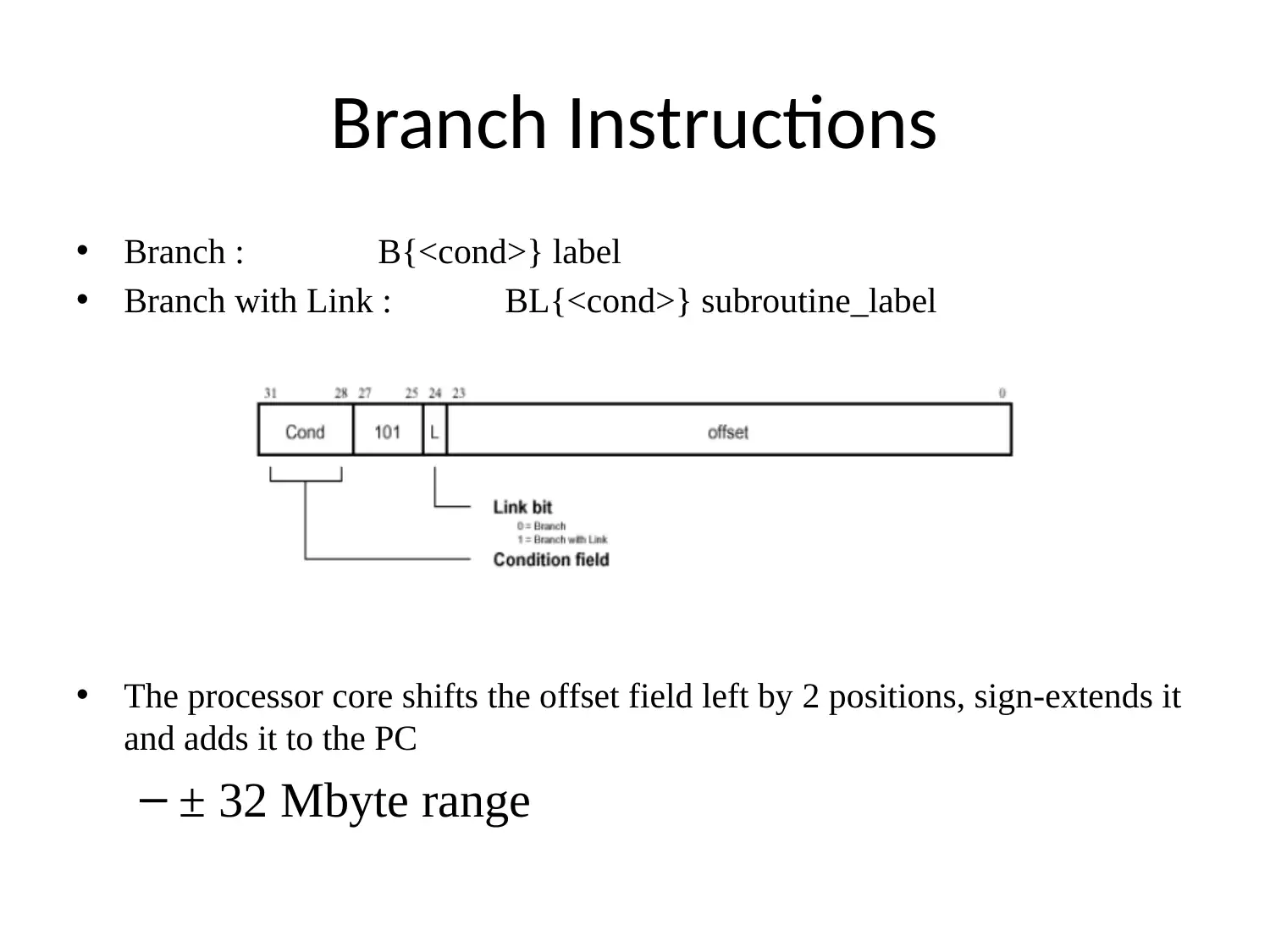

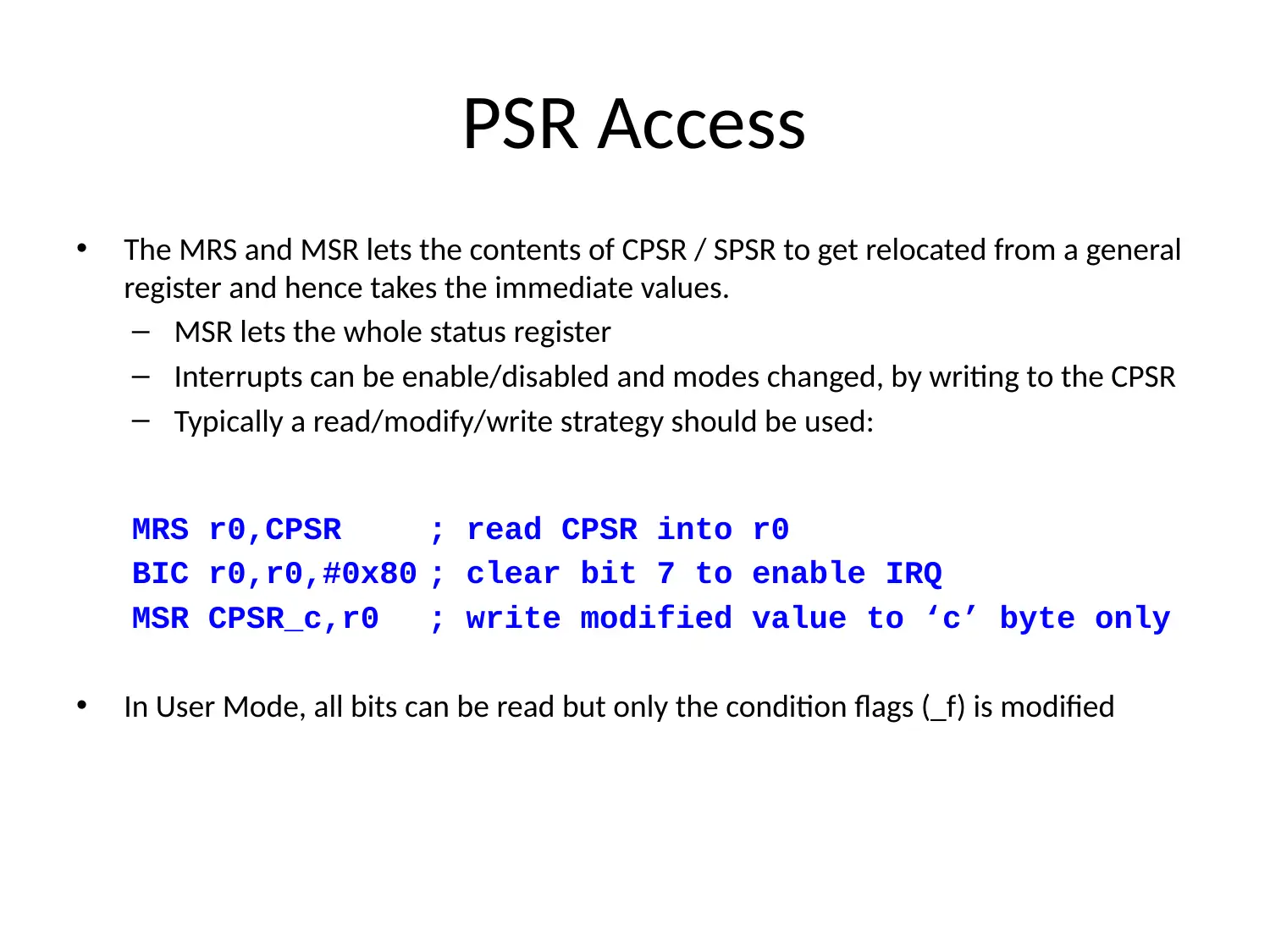

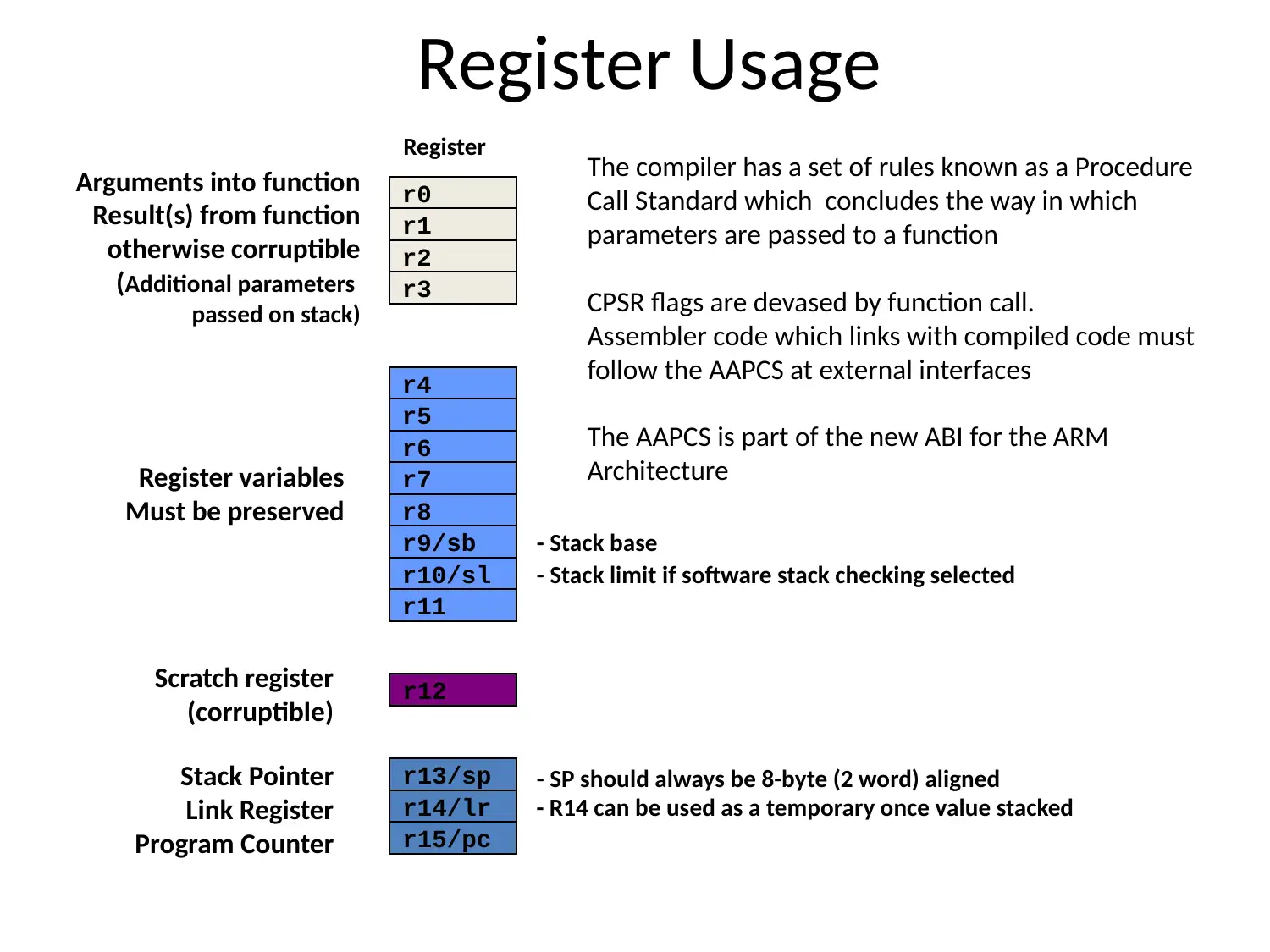

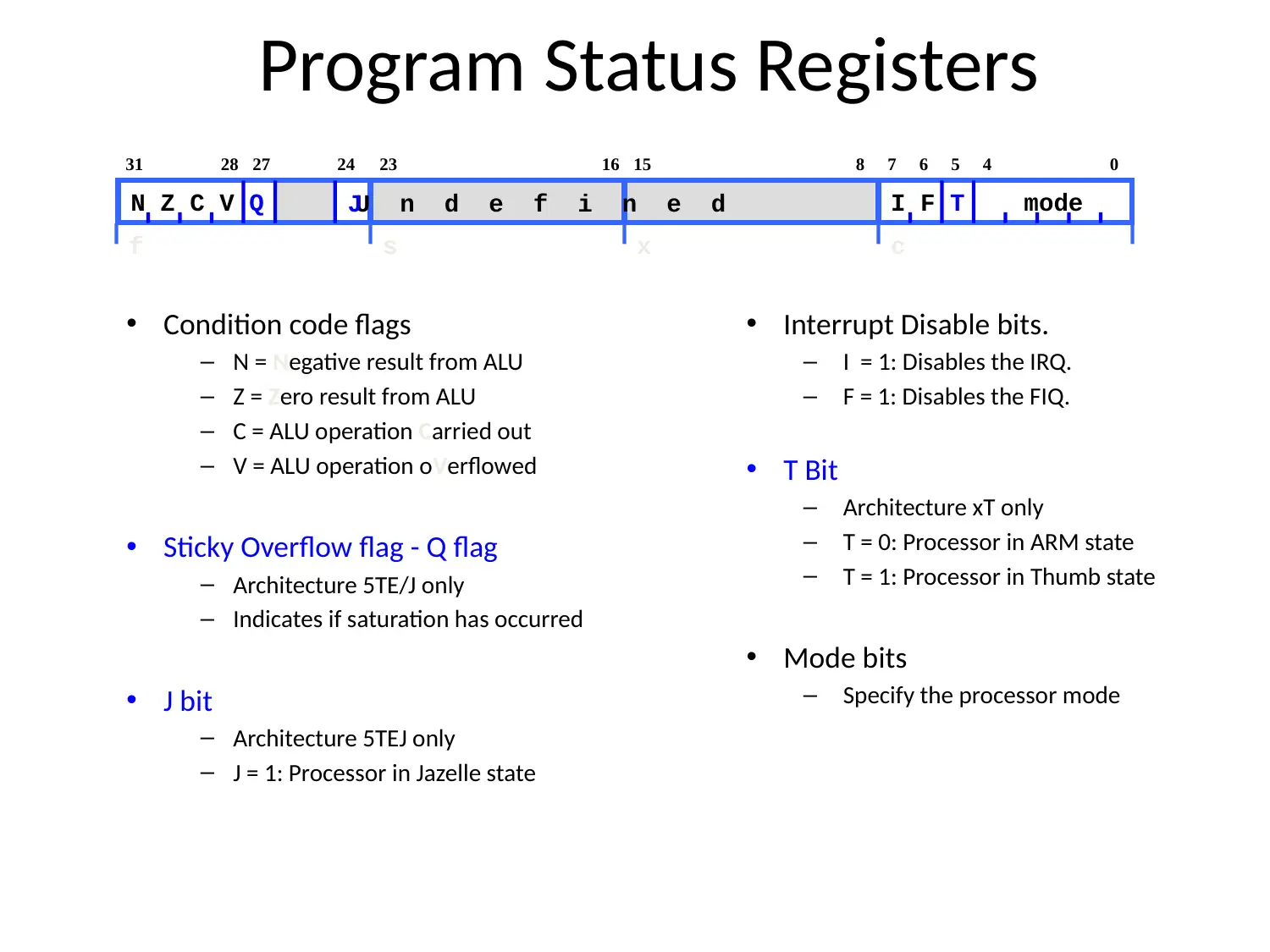

This report provides a comprehensive overview of the ARM processor architecture, beginning with its 32-bit structure and memory organization, defining byte, halfword, and word. It elucidates the two primary instruction sets: 32-bit ARM and 16-bit Thumb, highlighting their suitability for low-power devices and consumer electronics. The document details the seven basic operating modes: System, Abort, User, IRQ, Undef, FIQ, and Supervisor, explaining their roles in exception and interrupt handling. Furthermore, it describes the exception handling process, data processing instructions including arithmetic, logical, comparison, and data movement operations, and methods for loading 32-bit constants. The report also covers multiply and divide operations, branch instructions, PSR access, and register usage conventions as per the Procedure Call Standard. It concludes with a depiction of an example ARM-based system and provides a list of references for further reading. Desklib offers a wide array of solved assignments and study resources for students.

1 out of 15

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)