Memory Design and Instruction Set Architecture

VerifiedAdded on 2020/04/07

|6

|487

|87

AI Summary

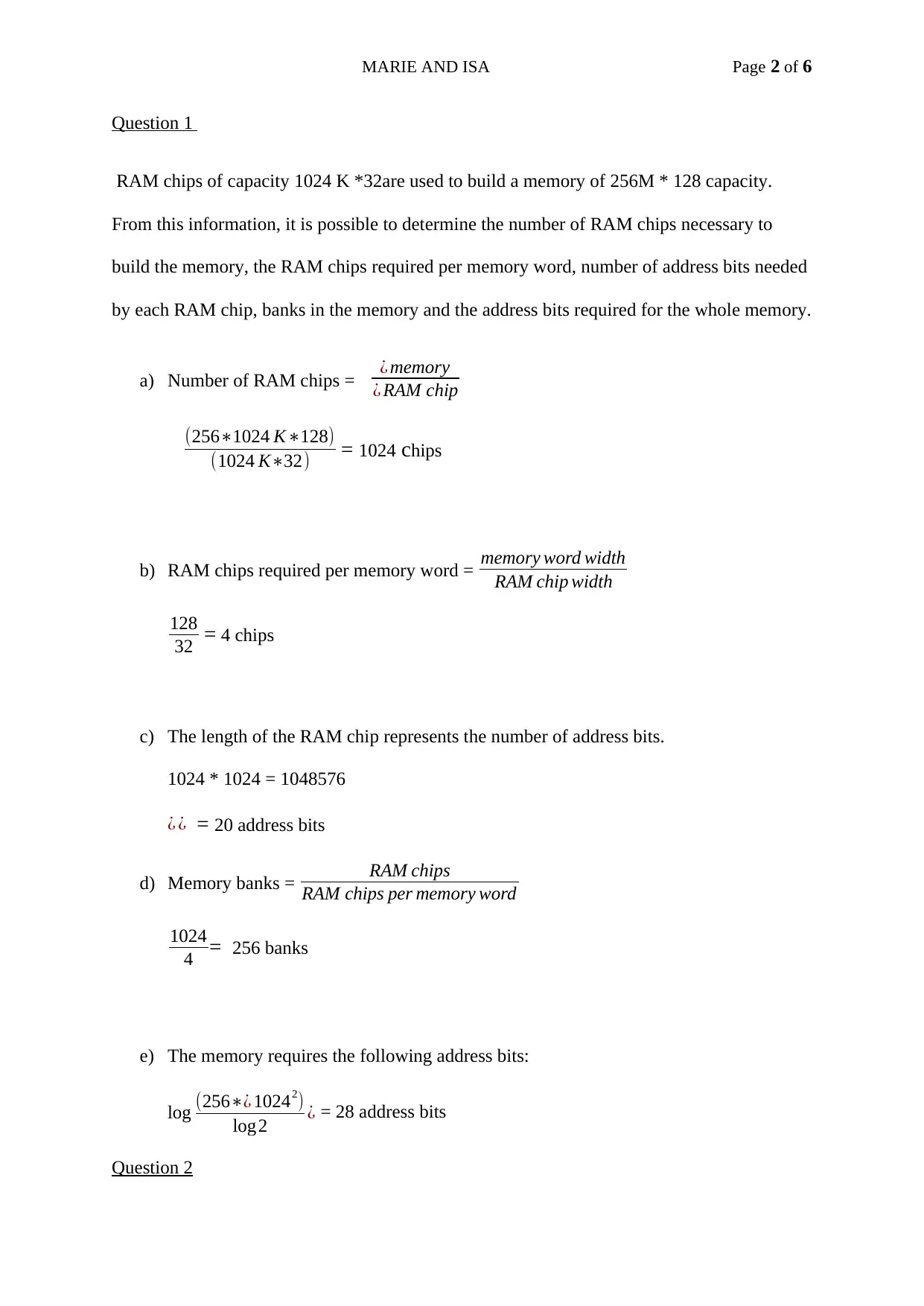

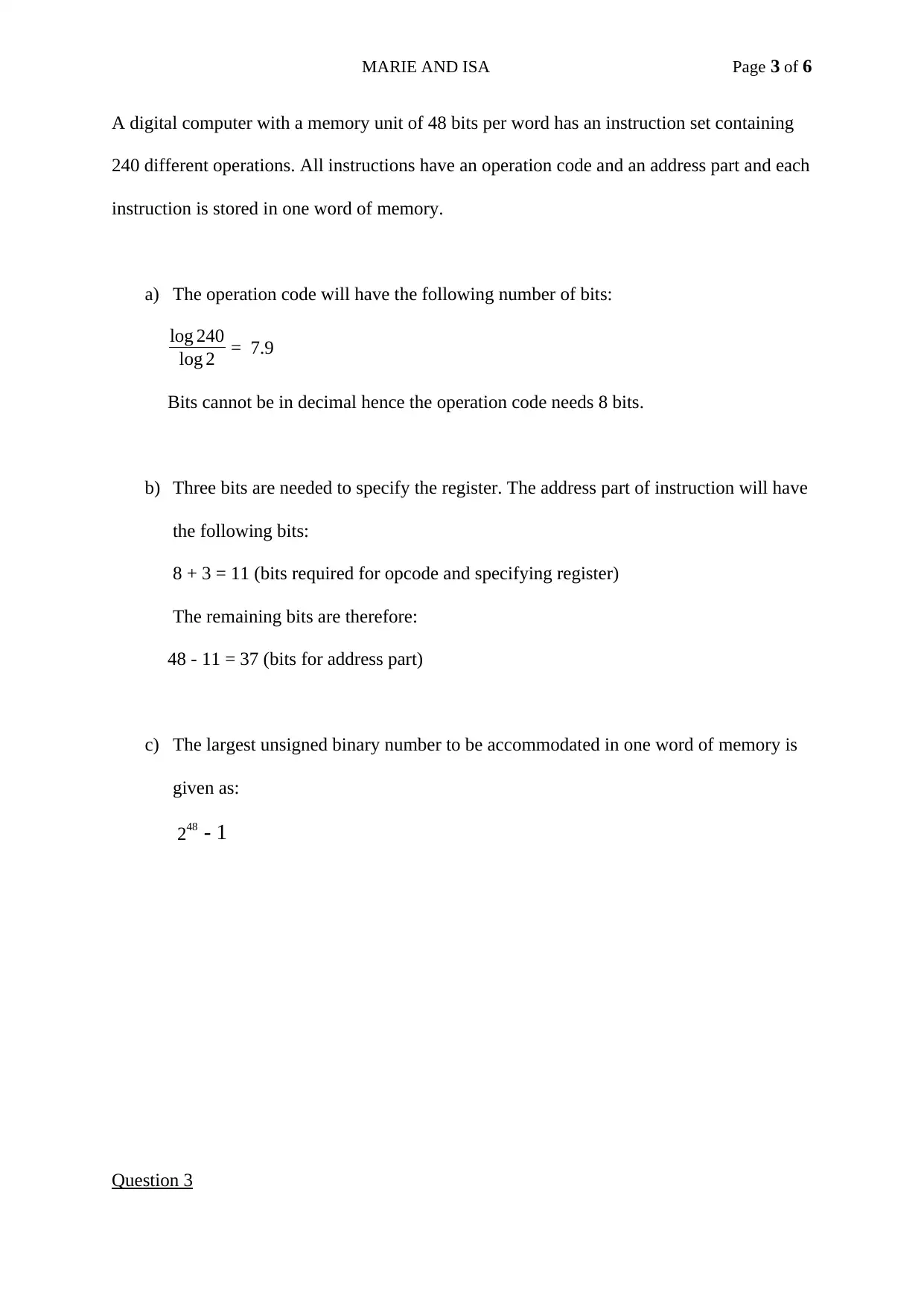

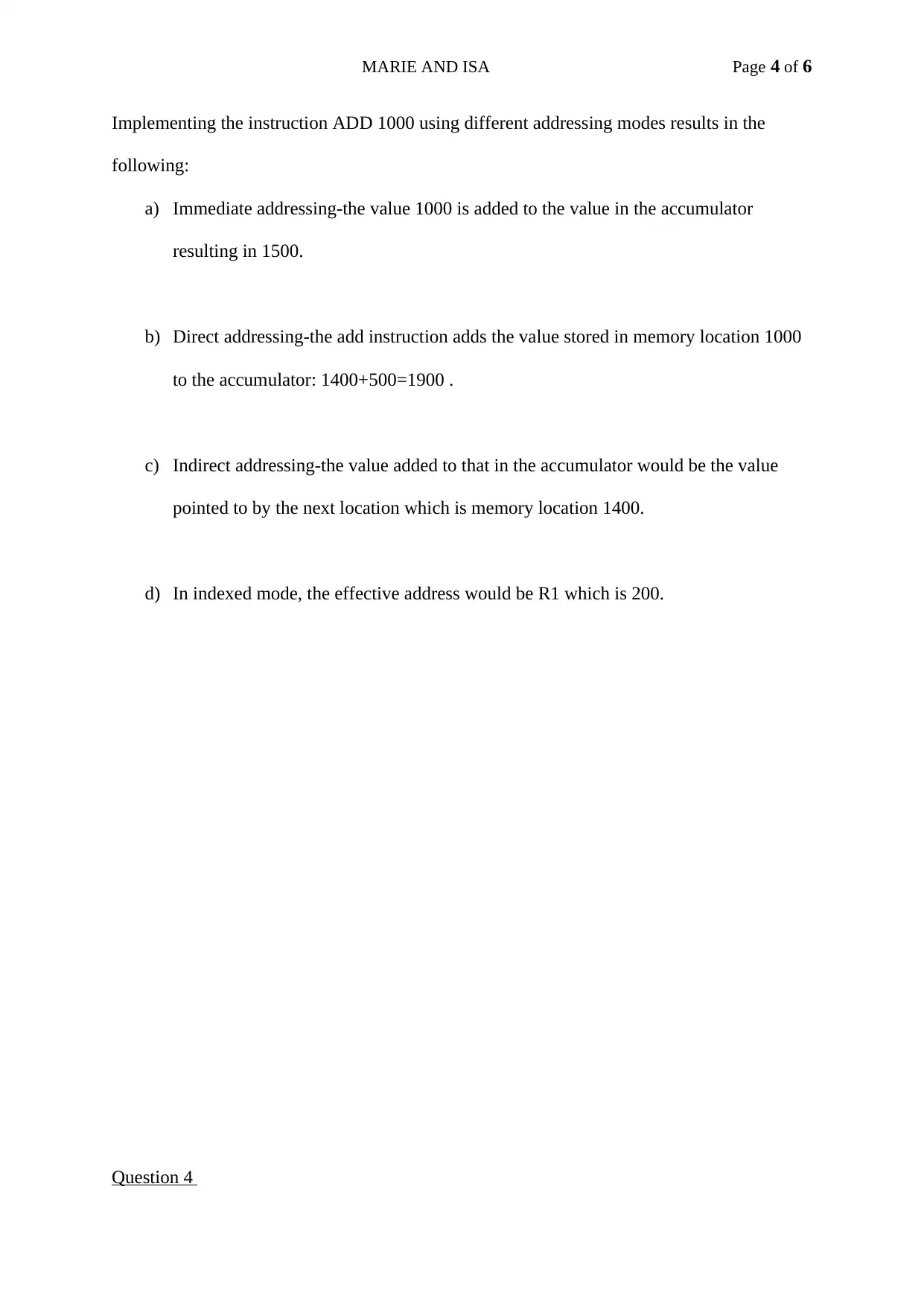

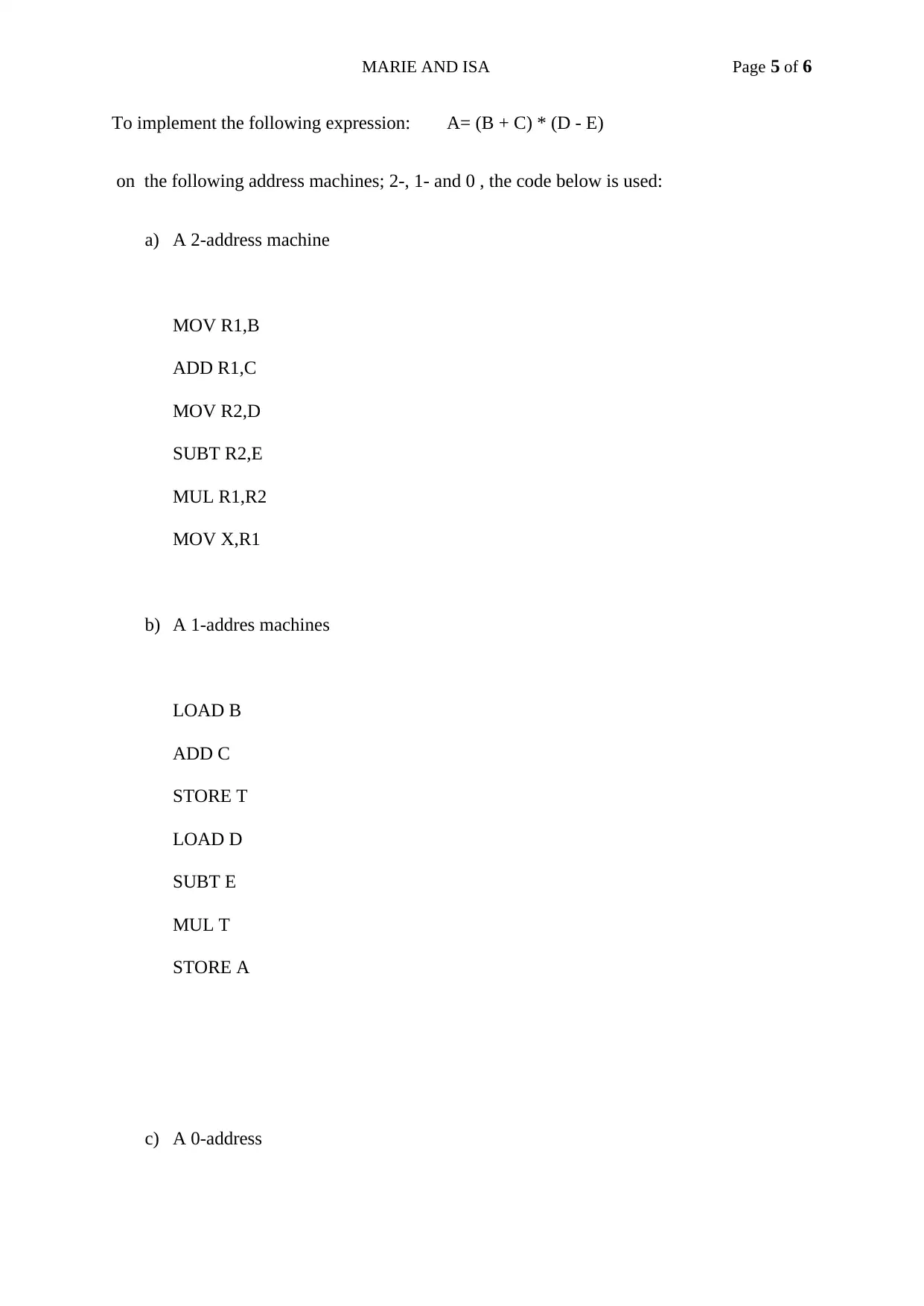

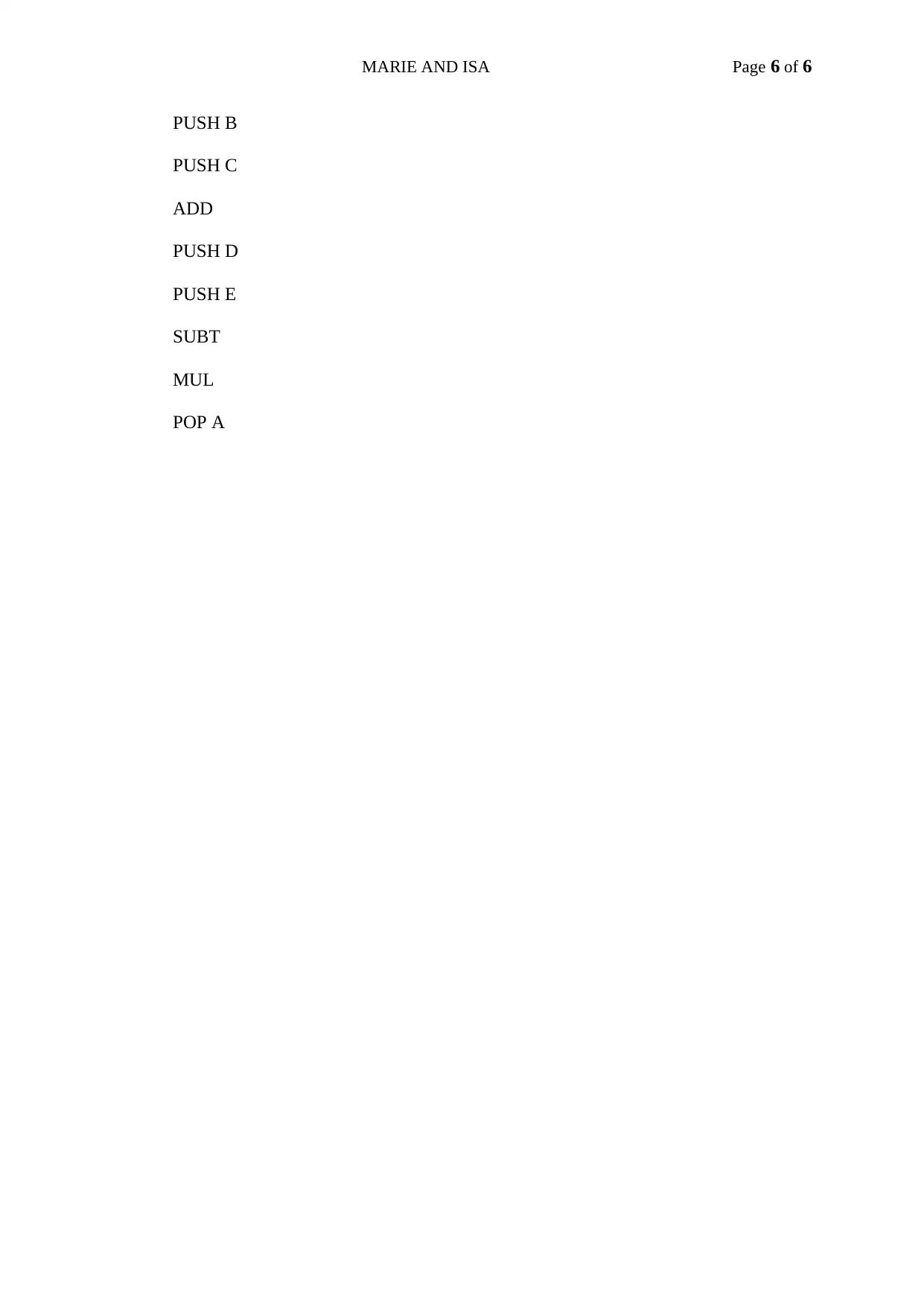

This assignment delves into the concepts of memory design and instruction set architecture. It involves calculating the number of RAM chips required for a specific memory capacity, determining address bits, and analyzing different addressing modes. The assignment also explores how to implement instructions using various addressing modes and illustrates the code for a given arithmetic expression in 2-, 1-, and 0-address machines.

Contribute Materials

Your contribution can guide someone’s learning journey. Share your

documents today.

1 out of 6

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)