EE4363 Computer Architecture Homework: Caches, ISA, and Pipelining

VerifiedAdded on 2022/08/29

|4

|660

|26

Homework Assignment

AI Summary

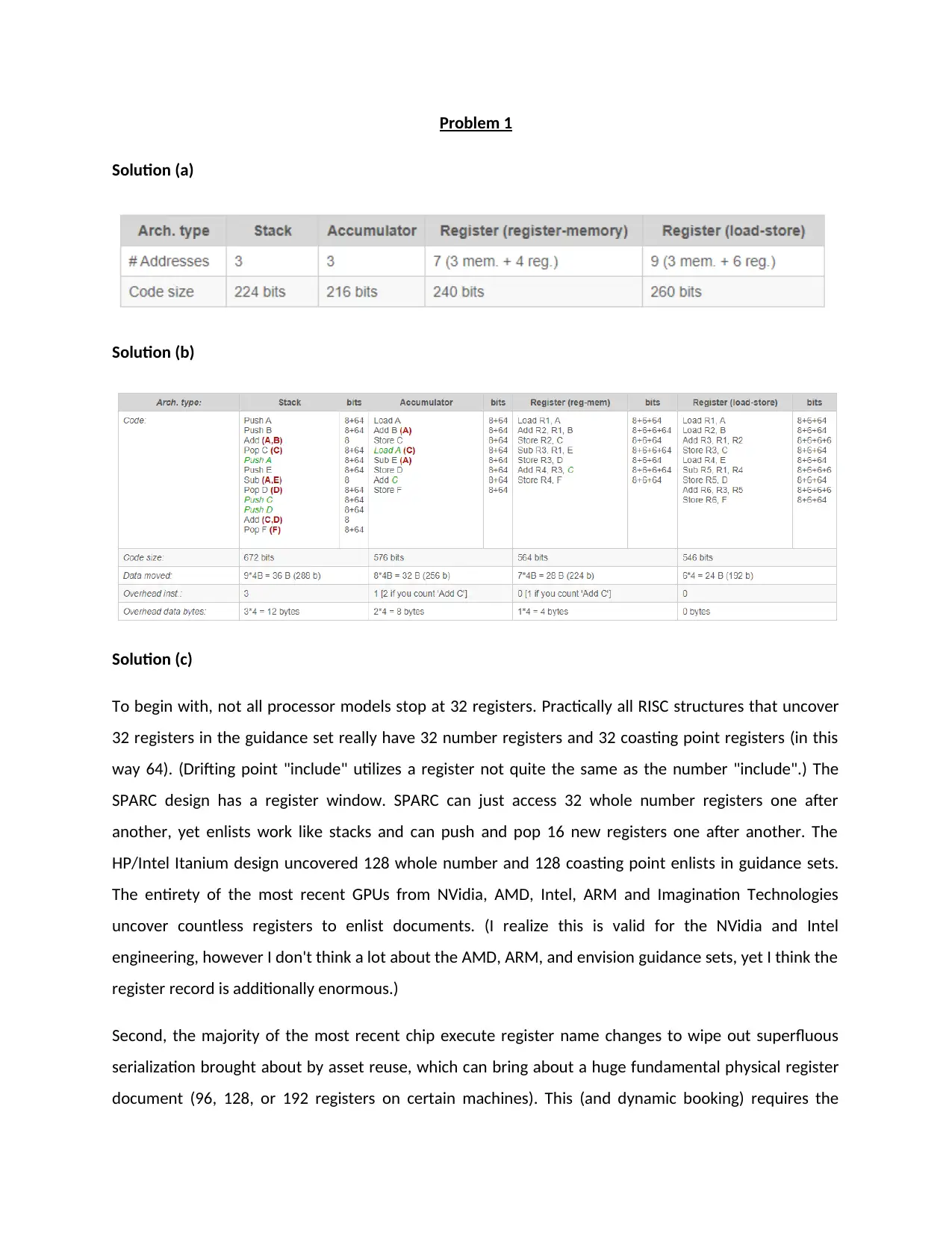

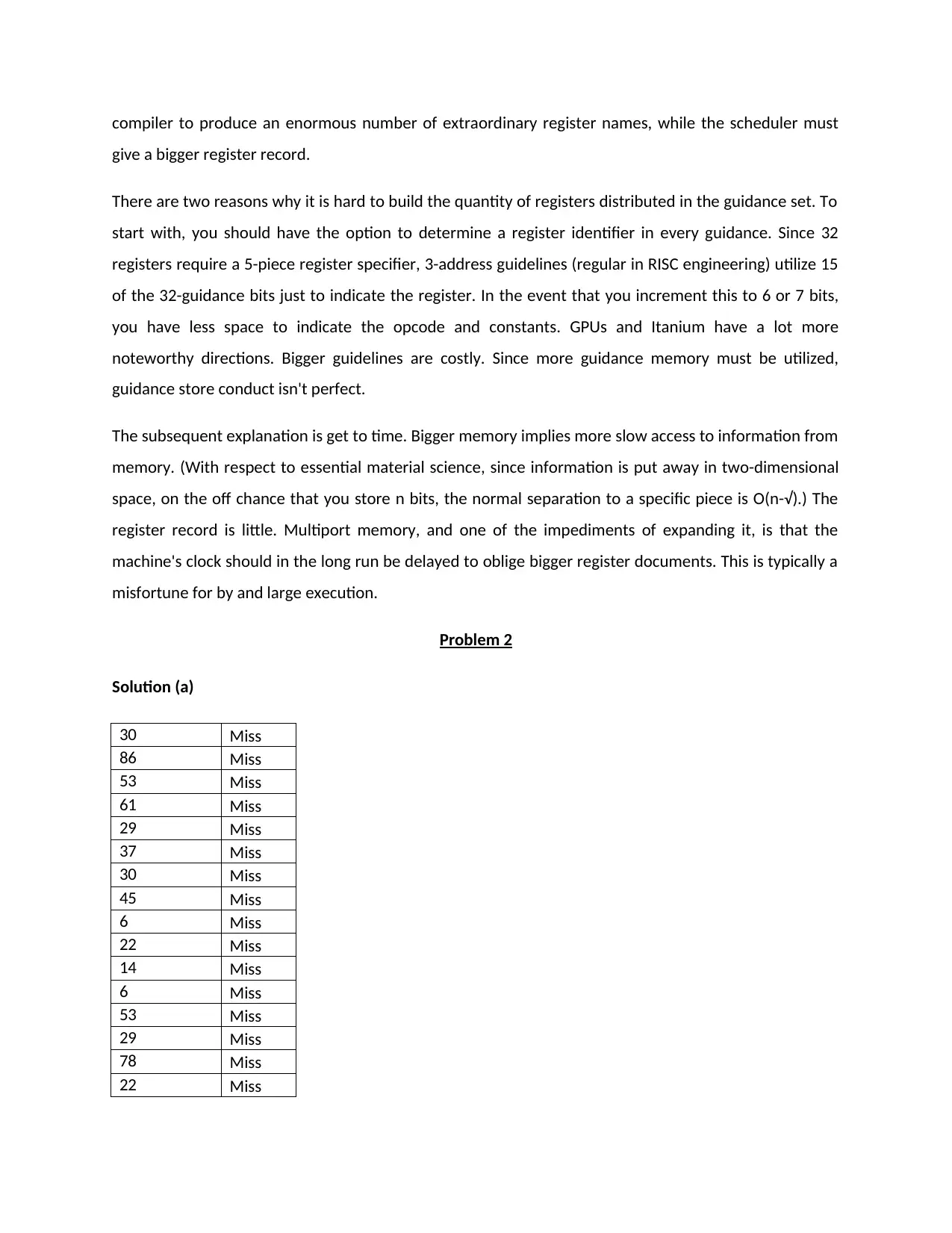

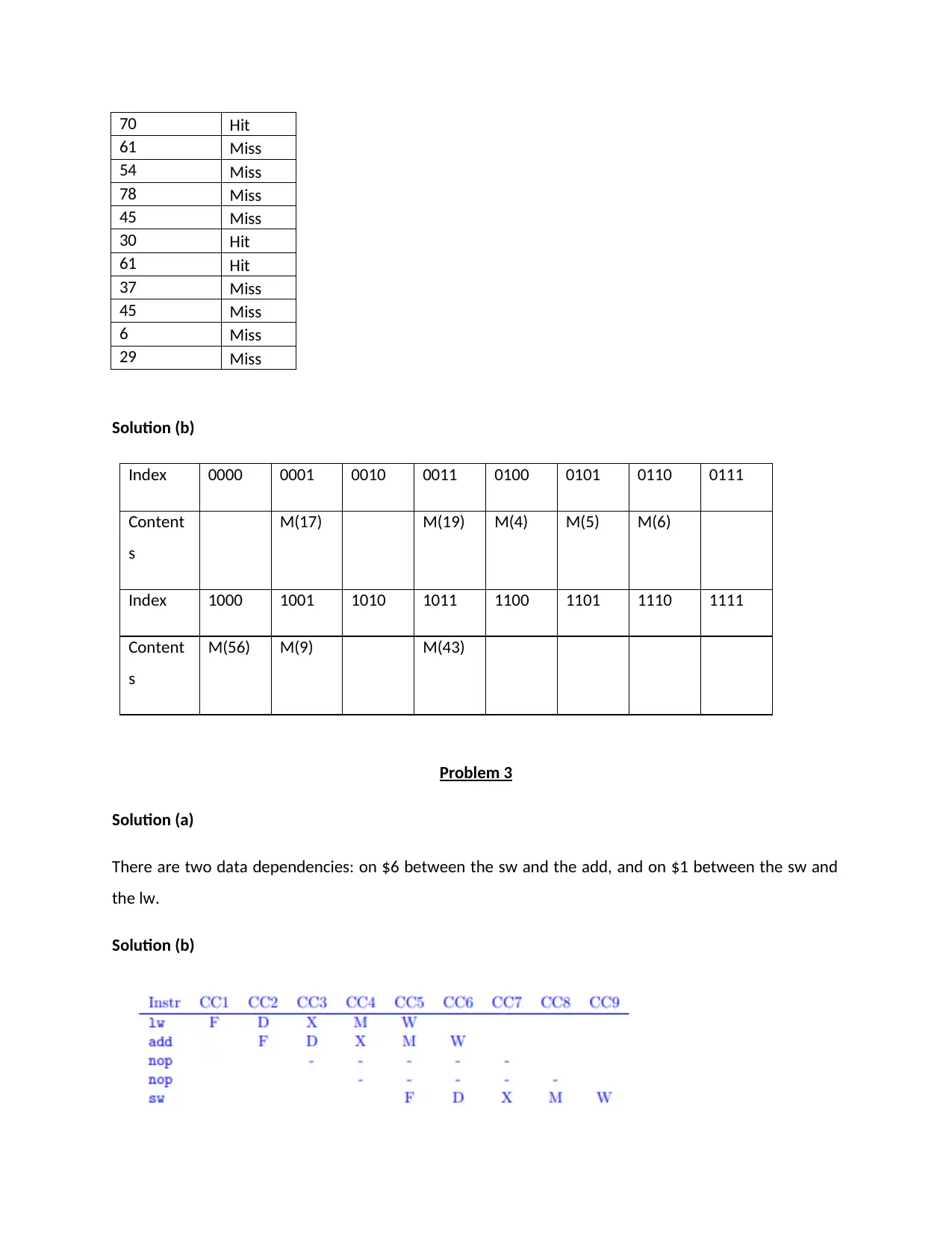

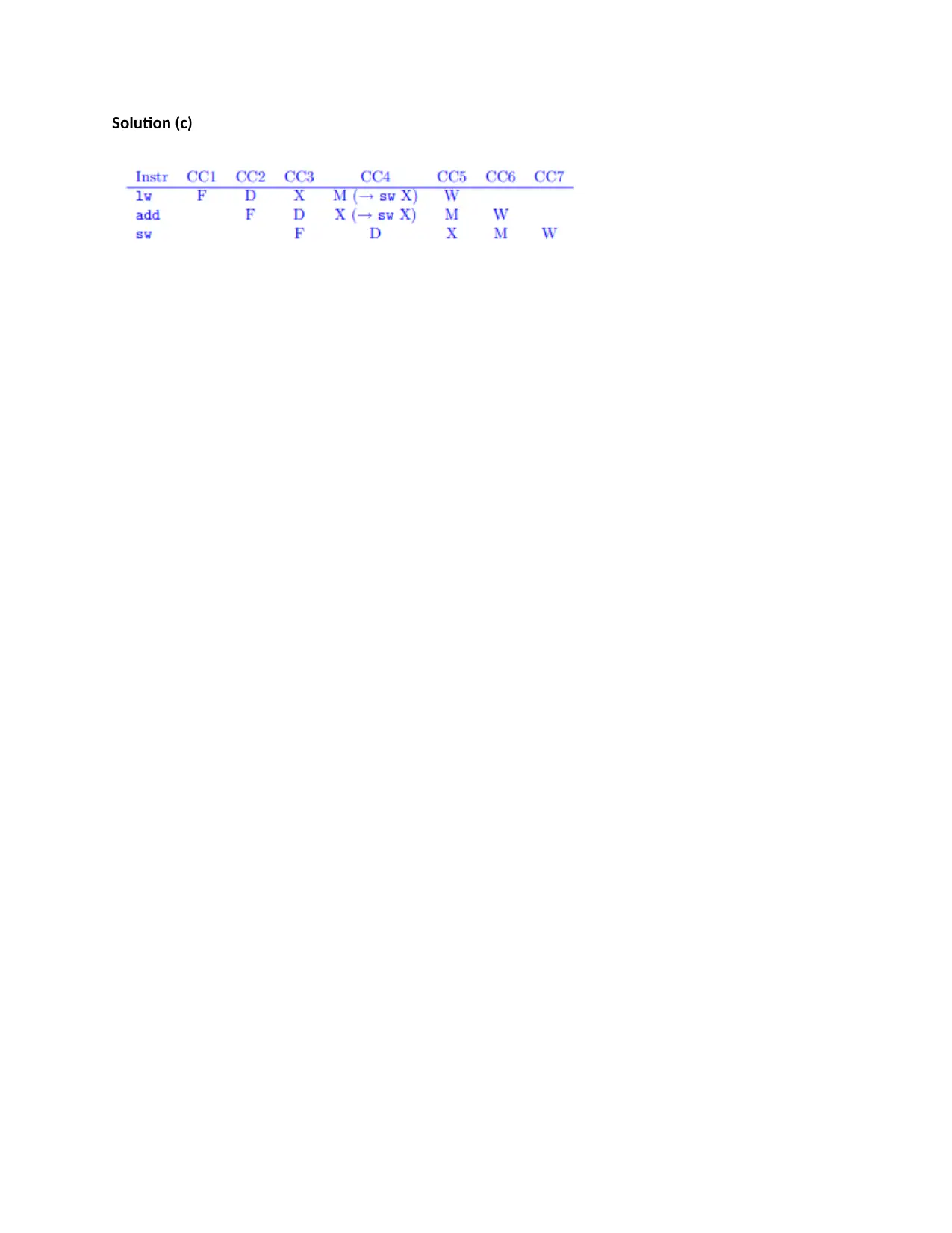

This document contains solutions to a computer architecture homework assignment for the EE4363/CSci 4203 course. The assignment covers key concepts including Instruction Set Architecture (ISA), cache memory, and pipelining. Problem 1 delves into the intricacies of ISA, exploring register files, and the challenges in expanding the number of registers, with a focus on stack, accumulator, register-memory, and register-register architectures. Problem 2 examines cache performance through a series of memory access patterns, requiring analysis of cache hits and misses, and the contents of a cache. Problem 3 explores data dependencies in code, specifically identifying dependencies between instructions involving memory loads and stores. The solutions provide detailed explanations and answers to each problem, offering a comprehensive understanding of computer architecture principles. The document is a valuable resource for students studying computer organization and architecture.

1 out of 4

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)