Computer Architectures and Principles Report: Analysis and Comparison

VerifiedAdded on 2022/11/24

|27

|4815

|90

Report

AI Summary

This report provides a comprehensive analysis and comparison of two contemporary commercial computer systems: the Intel Core i7-4960X processor and the AMD Phenom II X6 1100T processor. The report begins by mapping the components of these systems to the Von Neumann architecture, explaining the functionality of each component. A detailed comparison of the two processors is then presented, focusing on performance metrics such as throughput, execution time, energy consumption, and bandwidth. The report also examines the features of the MARIE computer model, including its architecture and basic instructions. Furthermore, the report discusses the concept of parallelism, including instruction-level, thread-level, and data-level parallelism. The report concludes with a discussion of future trends in processor design based on peer-reviewed research findings.

Computer Architectures and Principles

PROGRAMMING

Computer Architectures and Principles

Name of the Student

Name of the University

Author note

PROGRAMMING

Computer Architectures and Principles

Name of the Student

Name of the University

Author note

Paraphrase This Document

Need a fresh take? Get an instant paraphrase of this document with our AI Paraphraser

2

Computer Architectures and Principles

Table of Content

Introduction:...............................................................................................................................3

Methodology:.............................................................................................................................4

Von Neumann Architecture.......................................................................................................6

Intel core i7 - 4960X Processor..................................................................................................8

AMD PHENOM II X6 1100T....................................................................................................8

COMPARISION OF PARAMETERS and FEATURES...........................................................9

MARIE.....................................................................................................................................11

An Introduction....................................................................................................................11

Architecture..........................................................................................................................11

BASIC INSTRUCTIONS - MARIE...................................................................................13

Programming........................................................................................................................13

Algorithm.................................................................................................................................18

Conclusion:..............................................................................................................................23

References................................................................................................................................25

Computer Architectures and Principles

Table of Content

Introduction:...............................................................................................................................3

Methodology:.............................................................................................................................4

Von Neumann Architecture.......................................................................................................6

Intel core i7 - 4960X Processor..................................................................................................8

AMD PHENOM II X6 1100T....................................................................................................8

COMPARISION OF PARAMETERS and FEATURES...........................................................9

MARIE.....................................................................................................................................11

An Introduction....................................................................................................................11

Architecture..........................................................................................................................11

BASIC INSTRUCTIONS - MARIE...................................................................................13

Programming........................................................................................................................13

Algorithm.................................................................................................................................18

Conclusion:..............................................................................................................................23

References................................................................................................................................25

3

Computer Architectures and Principles

Introduction:

In this task, we are required to choose 2 contemporary commercial computer systems and

study them in detail.

In case of multi - core processors, there is a problem of power dissipation. This is due to the

use of more than 1 core. Another problem is to make a choice between the core type -

homogeneous core or heterogeneous core. We have considered 2 processors which are multi-

core processor machines for comparison. They are the Intel core i7 - 4960X processor and the

AMD Phenom II X6 processor. These have certain similarities to the von Neumann

Architecture. We have analysed and compared the design of these 2 computer systems. Our

main focus is on the performance metrics, costing, security, usability as well as energy

consumed of the 2 given processors ( as per Prinslow G. (2011)). We have also made a

prediction about the future trends in the designing of the processors based on the peer –

reviewed research findings.

Computer Architectures and Principles

Introduction:

In this task, we are required to choose 2 contemporary commercial computer systems and

study them in detail.

In case of multi - core processors, there is a problem of power dissipation. This is due to the

use of more than 1 core. Another problem is to make a choice between the core type -

homogeneous core or heterogeneous core. We have considered 2 processors which are multi-

core processor machines for comparison. They are the Intel core i7 - 4960X processor and the

AMD Phenom II X6 processor. These have certain similarities to the von Neumann

Architecture. We have analysed and compared the design of these 2 computer systems. Our

main focus is on the performance metrics, costing, security, usability as well as energy

consumed of the 2 given processors ( as per Prinslow G. (2011)). We have also made a

prediction about the future trends in the designing of the processors based on the peer –

reviewed research findings.

⊘ This is a preview!⊘

Do you want full access?

Subscribe today to unlock all pages.

Trusted by 1+ million students worldwide

4

Computer Architectures and Principles

Methodology:

If we have to measure the performance metrics of any processor, we can use various

parameters. They are : the throughput ( the average rate of the number of processes executed

successfully ), the response time, execution time, energy consumed and the bandwidth of the

memory ( the rate at which data is available from the core of the CPU to the RAM ). We

consider a system better, if it has a higher throughput, smaller execution time and moderate

power consumption.

If we have to make use of a multi - core processor fully, then we have to make use of

parallelism. We must have a feature to execute the programs parallely. There are various

types of parallelism. The 3 types are : Instruction level parallelism, thread level parallelism

and data level parallelism.

In instruction level parallelism, we can execute the instructions in a parallel manner or we can

execute them in a sequential manner. In thread level parallelism, we can present multiple

threads of a task to the processor which can be executed at the same time. In data level

parallelism, we use the concept of memory coherence to share any common data between the

processes being executed.

Computer Architectures and Principles

Methodology:

If we have to measure the performance metrics of any processor, we can use various

parameters. They are : the throughput ( the average rate of the number of processes executed

successfully ), the response time, execution time, energy consumed and the bandwidth of the

memory ( the rate at which data is available from the core of the CPU to the RAM ). We

consider a system better, if it has a higher throughput, smaller execution time and moderate

power consumption.

If we have to make use of a multi - core processor fully, then we have to make use of

parallelism. We must have a feature to execute the programs parallely. There are various

types of parallelism. The 3 types are : Instruction level parallelism, thread level parallelism

and data level parallelism.

In instruction level parallelism, we can execute the instructions in a parallel manner or we can

execute them in a sequential manner. In thread level parallelism, we can present multiple

threads of a task to the processor which can be executed at the same time. In data level

parallelism, we use the concept of memory coherence to share any common data between the

processes being executed.

Paraphrase This Document

Need a fresh take? Get an instant paraphrase of this document with our AI Paraphraser

5

Computer Architectures and Principles

As per Jeffers J, Reinders J, Sodani A (2016), the study which includes the real world code

examples which showcase the use of the particular features of the new largely parallel and

good performance computation product has been conducted.

If we use the concept of single threading, the execution time is the sum of time taken to

complete each task individually. If we use the concept of thread level parallelism, the

execution time is maximum value of all the individual task’s time taken.

As per Herdrich, A., Verplanke, E., Autee, P., Illikkal, R., Gianos, C., Singhal, R., & Iyer, R.

(2016), during the last 10 years, addressing the quality of service (QoS) in multi-core server

platforms is a fastly growing research topic.

As per Sodani, A., Gramunt, R., Corbal, J., Kim, H.-S., Vinod, K., Chinthamani, S., Liu, Y.-

C. (2016), the Knights Landing Processor is targeting the good performance of computing

and the parallel workload. It gives a far better performance as well as bandwidth of memory

as compared to the earlier generations.

Computer Architectures and Principles

As per Jeffers J, Reinders J, Sodani A (2016), the study which includes the real world code

examples which showcase the use of the particular features of the new largely parallel and

good performance computation product has been conducted.

If we use the concept of single threading, the execution time is the sum of time taken to

complete each task individually. If we use the concept of thread level parallelism, the

execution time is maximum value of all the individual task’s time taken.

As per Herdrich, A., Verplanke, E., Autee, P., Illikkal, R., Gianos, C., Singhal, R., & Iyer, R.

(2016), during the last 10 years, addressing the quality of service (QoS) in multi-core server

platforms is a fastly growing research topic.

As per Sodani, A., Gramunt, R., Corbal, J., Kim, H.-S., Vinod, K., Chinthamani, S., Liu, Y.-

C. (2016), the Knights Landing Processor is targeting the good performance of computing

and the parallel workload. It gives a far better performance as well as bandwidth of memory

as compared to the earlier generations.

6

Computer Architectures and Principles

Von Neumann Architecture

The model is also called as the Princeton architecture. The various components present in the

architecture are : the processing unit which contains the ALU (Arithmetie Logic Unit) and the

processor registers, the control unit which contains an instruction register and a program

counter, the memory to store data and instructions, there is external mass storage and the

input and output of procedures. In this type of model, the instruction fetch and any data

operation does not occur at the same time as they share the common bus. This leads to an

effect on the performance of the system. The program instructions as well as the data are kept

in RAM (Random Access Memory).

The Von Neumann architecture has a shared bus for the program memory and data memory.

This leads to slower data transfer rate between the memory and the CPU (Central processing

unit). It is because we have only 1 bus and we cannot access two classes of the memory at a

single time. This lowers the throughput. It does not allow the CPU to reach its maximum rate.

The speed of processing the data becomes slower due to this. The performance of Von

Neumann architecture can be enhanced by some methods. They are: provision of a cache

between the CPU and the main memory, to provide separate caches as well as separate access

paths for data and instruction, by the use of branch predictor algorithm and the logic, to

provide limited CPU stack and scratch pad memory to decrease the access of memory, to

implement the CPU and memory hierarchy which helps in decreasing the latency and

enhancing the throughput between the processor registers and main memory. We solve this

by using the concept of parallel computing. The researches show that an increase in the

Computer Architectures and Principles

Von Neumann Architecture

The model is also called as the Princeton architecture. The various components present in the

architecture are : the processing unit which contains the ALU (Arithmetie Logic Unit) and the

processor registers, the control unit which contains an instruction register and a program

counter, the memory to store data and instructions, there is external mass storage and the

input and output of procedures. In this type of model, the instruction fetch and any data

operation does not occur at the same time as they share the common bus. This leads to an

effect on the performance of the system. The program instructions as well as the data are kept

in RAM (Random Access Memory).

The Von Neumann architecture has a shared bus for the program memory and data memory.

This leads to slower data transfer rate between the memory and the CPU (Central processing

unit). It is because we have only 1 bus and we cannot access two classes of the memory at a

single time. This lowers the throughput. It does not allow the CPU to reach its maximum rate.

The speed of processing the data becomes slower due to this. The performance of Von

Neumann architecture can be enhanced by some methods. They are: provision of a cache

between the CPU and the main memory, to provide separate caches as well as separate access

paths for data and instruction, by the use of branch predictor algorithm and the logic, to

provide limited CPU stack and scratch pad memory to decrease the access of memory, to

implement the CPU and memory hierarchy which helps in decreasing the latency and

enhancing the throughput between the processor registers and main memory. We solve this

by using the concept of parallel computing. The researches show that an increase in the

⊘ This is a preview!⊘

Do you want full access?

Subscribe today to unlock all pages.

Trusted by 1+ million students worldwide

7

Computer Architectures and Principles

number of instruction streams which are simultaneous ( using multi threading or multi

processing of single chip) makes the problem worse. So, we need additional overhead for the

maintenance of cache coherence between the processors and threads.

Computer Architectures and Principles

number of instruction streams which are simultaneous ( using multi threading or multi

processing of single chip) makes the problem worse. So, we need additional overhead for the

maintenance of cache coherence between the processors and threads.

Paraphrase This Document

Need a fresh take? Get an instant paraphrase of this document with our AI Paraphraser

8

Computer Architectures and Principles

Intel core i7 - 4960X Processor

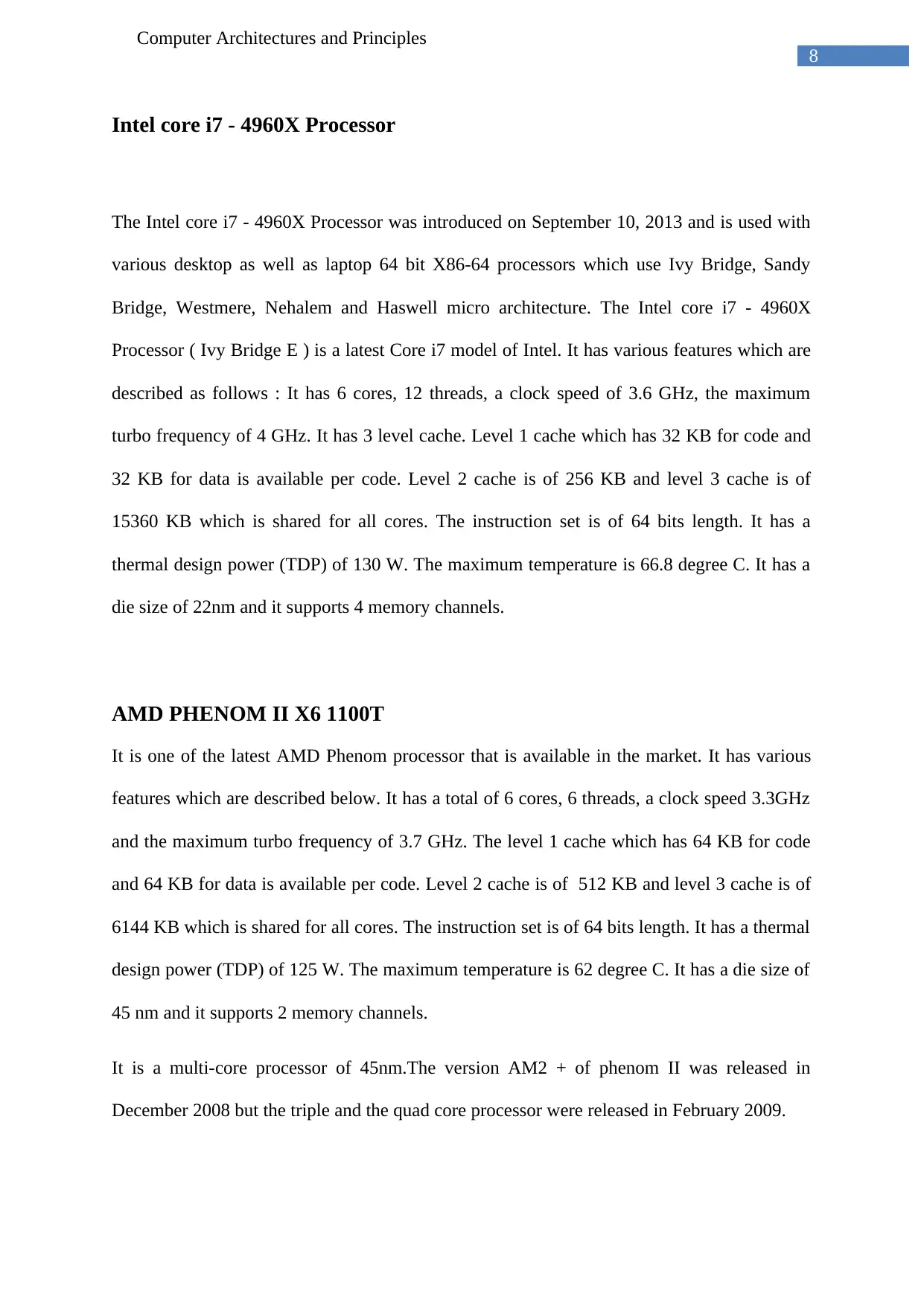

The Intel core i7 - 4960X Processor was introduced on September 10, 2013 and is used with

various desktop as well as laptop 64 bit X86-64 processors which use Ivy Bridge, Sandy

Bridge, Westmere, Nehalem and Haswell micro architecture. The Intel core i7 - 4960X

Processor ( Ivy Bridge E ) is a latest Core i7 model of Intel. It has various features which are

described as follows : It has 6 cores, 12 threads, a clock speed of 3.6 GHz, the maximum

turbo frequency of 4 GHz. It has 3 level cache. Level 1 cache which has 32 KB for code and

32 KB for data is available per code. Level 2 cache is of 256 KB and level 3 cache is of

15360 KB which is shared for all cores. The instruction set is of 64 bits length. It has a

thermal design power (TDP) of 130 W. The maximum temperature is 66.8 degree C. It has a

die size of 22nm and it supports 4 memory channels.

AMD PHENOM II X6 1100T

It is one of the latest AMD Phenom processor that is available in the market. It has various

features which are described below. It has a total of 6 cores, 6 threads, a clock speed 3.3GHz

and the maximum turbo frequency of 3.7 GHz. The level 1 cache which has 64 KB for code

and 64 KB for data is available per code. Level 2 cache is of 512 KB and level 3 cache is of

6144 KB which is shared for all cores. The instruction set is of 64 bits length. It has a thermal

design power (TDP) of 125 W. The maximum temperature is 62 degree C. It has a die size of

45 nm and it supports 2 memory channels.

It is a multi-core processor of 45nm.The version AM2 + of phenom II was released in

December 2008 but the triple and the quad core processor were released in February 2009.

Computer Architectures and Principles

Intel core i7 - 4960X Processor

The Intel core i7 - 4960X Processor was introduced on September 10, 2013 and is used with

various desktop as well as laptop 64 bit X86-64 processors which use Ivy Bridge, Sandy

Bridge, Westmere, Nehalem and Haswell micro architecture. The Intel core i7 - 4960X

Processor ( Ivy Bridge E ) is a latest Core i7 model of Intel. It has various features which are

described as follows : It has 6 cores, 12 threads, a clock speed of 3.6 GHz, the maximum

turbo frequency of 4 GHz. It has 3 level cache. Level 1 cache which has 32 KB for code and

32 KB for data is available per code. Level 2 cache is of 256 KB and level 3 cache is of

15360 KB which is shared for all cores. The instruction set is of 64 bits length. It has a

thermal design power (TDP) of 130 W. The maximum temperature is 66.8 degree C. It has a

die size of 22nm and it supports 4 memory channels.

AMD PHENOM II X6 1100T

It is one of the latest AMD Phenom processor that is available in the market. It has various

features which are described below. It has a total of 6 cores, 6 threads, a clock speed 3.3GHz

and the maximum turbo frequency of 3.7 GHz. The level 1 cache which has 64 KB for code

and 64 KB for data is available per code. Level 2 cache is of 512 KB and level 3 cache is of

6144 KB which is shared for all cores. The instruction set is of 64 bits length. It has a thermal

design power (TDP) of 125 W. The maximum temperature is 62 degree C. It has a die size of

45 nm and it supports 2 memory channels.

It is a multi-core processor of 45nm.The version AM2 + of phenom II was released in

December 2008 but the triple and the quad core processor were released in February 2009.

9

Computer Architectures and Principles

COMPARISION OF PARAMETERS and FEATURES

Firstly we see a comparison which is based on the power dissipation. In the AMD Phenom II

X6 processor, the thermal design power is 125 W and in the Intel core i7 - 4960X processor,

the thermal design power is 130 W. Hence , we see that the AMD Phenom II X6 processor

will save 4% energy as compared to the Intel core i7 - 4960X processor.

Another parameter used to compare the 2 processors is based on the concept of Hyper-

Threading . The Intel core i7 - 4960X processor support the Hyper-Threading technology and

the AMD Phenom II X6 processor does not support the Hyper-Threading technology. Hence,

we see that the Intel processor is able to execute double number of threads as compared to the

AMD Phenom II X6 processor.

Next parameter used for the comparison is the operating frequency. The Intel core i7 - 4960X

processor has a higher frequency than the AMD Phenom II X6 processor. Hence, it executes

more number of operations per minute.

The number of cores or threads in the AMD Phenom II X6 processor is 6 and that in the Intel

core i7 - 4960X processor is 12. Out of 12, 6 threads are provided by Hyper-Threading

technology which are the additional threads. The operating frequency in case of the AMD

Phenom II X6 processor is 3.7 GHz and for Intel processor it is 4GHz. Hence, Intel processor

is faster. Another parameter is on the basis of AES encryption and decryption. The Intel core

i7 - 4960X processor uses AES (Advanced Encryption Standard) technology. It is helpful in

running the programs and helps to protect the disk or the network data. If we compare the

cache memory size, the AMD Phenom II X6 processor has on chip L2 and L3 cache of 9 MB

and the Intel core i7 - 4960X processor has 16.5 MB. So, the Intel core i7 - 4960X processor

Computer Architectures and Principles

COMPARISION OF PARAMETERS and FEATURES

Firstly we see a comparison which is based on the power dissipation. In the AMD Phenom II

X6 processor, the thermal design power is 125 W and in the Intel core i7 - 4960X processor,

the thermal design power is 130 W. Hence , we see that the AMD Phenom II X6 processor

will save 4% energy as compared to the Intel core i7 - 4960X processor.

Another parameter used to compare the 2 processors is based on the concept of Hyper-

Threading . The Intel core i7 - 4960X processor support the Hyper-Threading technology and

the AMD Phenom II X6 processor does not support the Hyper-Threading technology. Hence,

we see that the Intel processor is able to execute double number of threads as compared to the

AMD Phenom II X6 processor.

Next parameter used for the comparison is the operating frequency. The Intel core i7 - 4960X

processor has a higher frequency than the AMD Phenom II X6 processor. Hence, it executes

more number of operations per minute.

The number of cores or threads in the AMD Phenom II X6 processor is 6 and that in the Intel

core i7 - 4960X processor is 12. Out of 12, 6 threads are provided by Hyper-Threading

technology which are the additional threads. The operating frequency in case of the AMD

Phenom II X6 processor is 3.7 GHz and for Intel processor it is 4GHz. Hence, Intel processor

is faster. Another parameter is on the basis of AES encryption and decryption. The Intel core

i7 - 4960X processor uses AES (Advanced Encryption Standard) technology. It is helpful in

running the programs and helps to protect the disk or the network data. If we compare the

cache memory size, the AMD Phenom II X6 processor has on chip L2 and L3 cache of 9 MB

and the Intel core i7 - 4960X processor has 16.5 MB. So, the Intel core i7 - 4960X processor

⊘ This is a preview!⊘

Do you want full access?

Subscribe today to unlock all pages.

Trusted by 1+ million students worldwide

10

Computer Architectures and Principles

is better in this manner. Another parameter which can be used for comparison is on the basis

of cache memory classification. The Intel core i7 - 4960X processor has an inclusive cache

whereas the AMD Phenom II X6 processor has an exclusive cache. In case of inclusive

cache, the data that is stored in the individual L1 and L2 cache exists as a duplicate data. This

will help to enhance the inter – core communication process.

The memory controller may also be used to compare any 2 processors. In Intel processor, we

use integrated memory’s controller. This enables us to fetch the main memory faster.

The applications which show positive results with a GPU always show good results with an

Intel processor. The Intel Processor has the features of vectorization and bandwidth. It shows

a support for the applications which can’t be run on the GPUs according to Chrysos, G

( 2012 ).

Computer Architectures and Principles

is better in this manner. Another parameter which can be used for comparison is on the basis

of cache memory classification. The Intel core i7 - 4960X processor has an inclusive cache

whereas the AMD Phenom II X6 processor has an exclusive cache. In case of inclusive

cache, the data that is stored in the individual L1 and L2 cache exists as a duplicate data. This

will help to enhance the inter – core communication process.

The memory controller may also be used to compare any 2 processors. In Intel processor, we

use integrated memory’s controller. This enables us to fetch the main memory faster.

The applications which show positive results with a GPU always show good results with an

Intel processor. The Intel Processor has the features of vectorization and bandwidth. It shows

a support for the applications which can’t be run on the GPUs according to Chrysos, G

( 2012 ).

Paraphrase This Document

Need a fresh take? Get an instant paraphrase of this document with our AI Paraphraser

11

Computer Architectures and Principles

MARIE

An Introduction

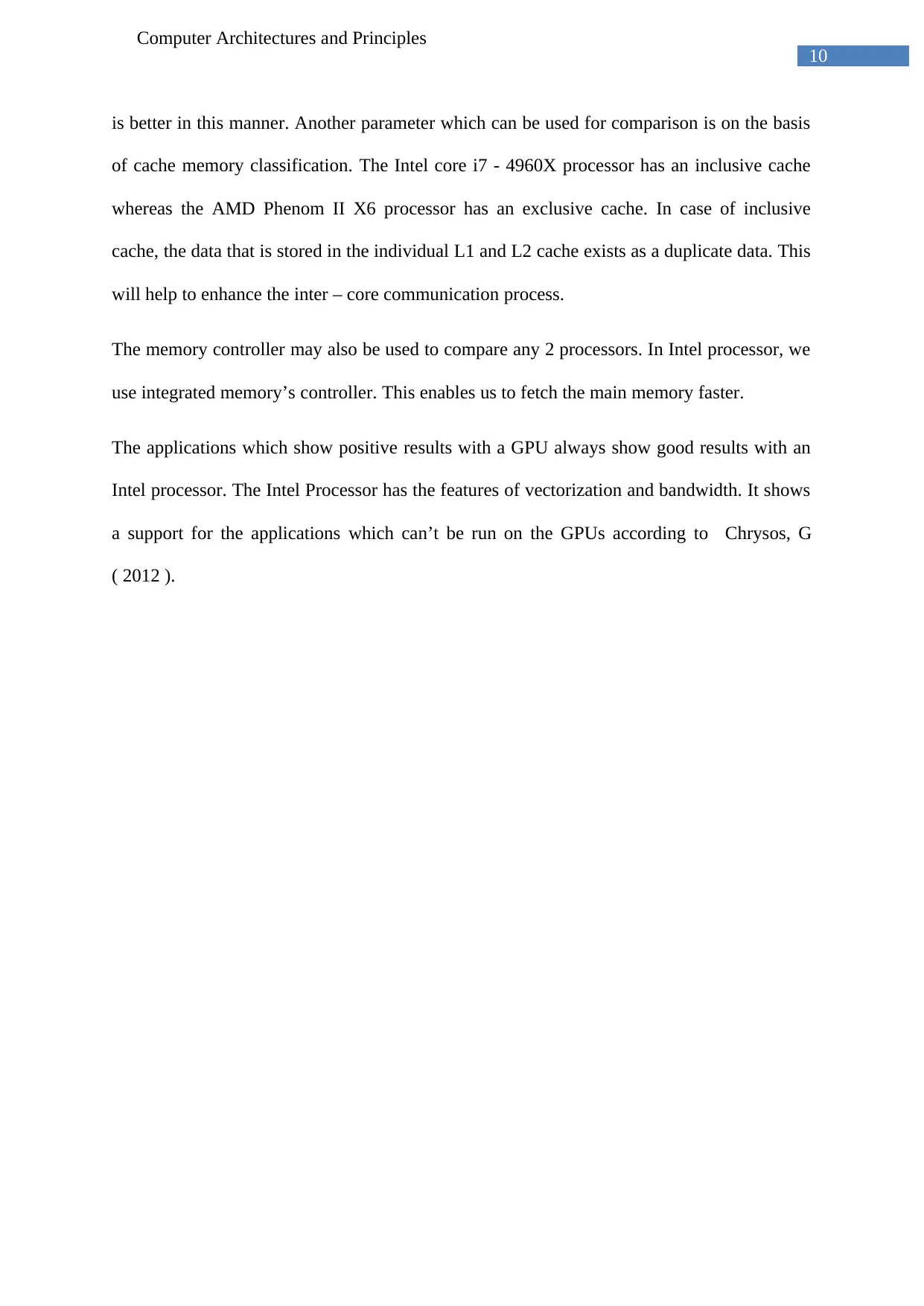

MARIE is a computer model that contains the memory which can store the data and also a

processor which contains an ALU and various registers. MARIE stands for Machine

Architecture that is Really Intuitive and Easy. The various features of MARIE’s model are : a

main memory of 4 kB ( we use 12 bits for every address), the data is of 16 bits, instructions

are of 16 bit ( with operation code of 4 bits and address of 12 bits), 16 bit AC, 16 bit

instruction register ( IR ), 16 bit memory buffer register ( MBR), 12 bit instruction counter

(PC), 12 bit memory address register ( MAR ), 8 bit input register ( InREG) and 8 bit output

register(OutREG).

Architecture

Courtesy : Null, L., Lobur, J. (2003)

Computer Architectures and Principles

MARIE

An Introduction

MARIE is a computer model that contains the memory which can store the data and also a

processor which contains an ALU and various registers. MARIE stands for Machine

Architecture that is Really Intuitive and Easy. The various features of MARIE’s model are : a

main memory of 4 kB ( we use 12 bits for every address), the data is of 16 bits, instructions

are of 16 bit ( with operation code of 4 bits and address of 12 bits), 16 bit AC, 16 bit

instruction register ( IR ), 16 bit memory buffer register ( MBR), 12 bit instruction counter

(PC), 12 bit memory address register ( MAR ), 8 bit input register ( InREG) and 8 bit output

register(OutREG).

Architecture

Courtesy : Null, L., Lobur, J. (2003)

12

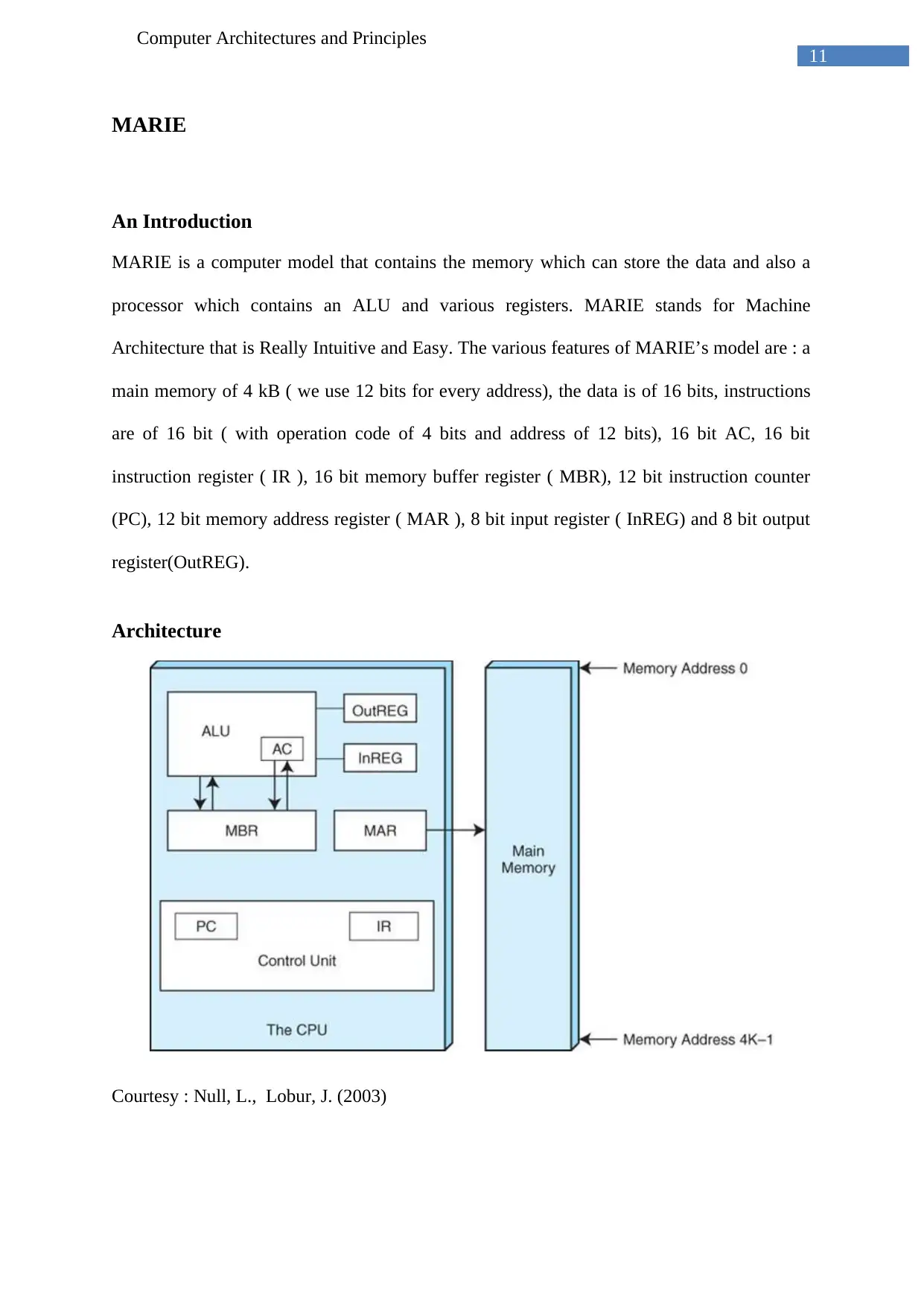

Computer Architectures and Principles

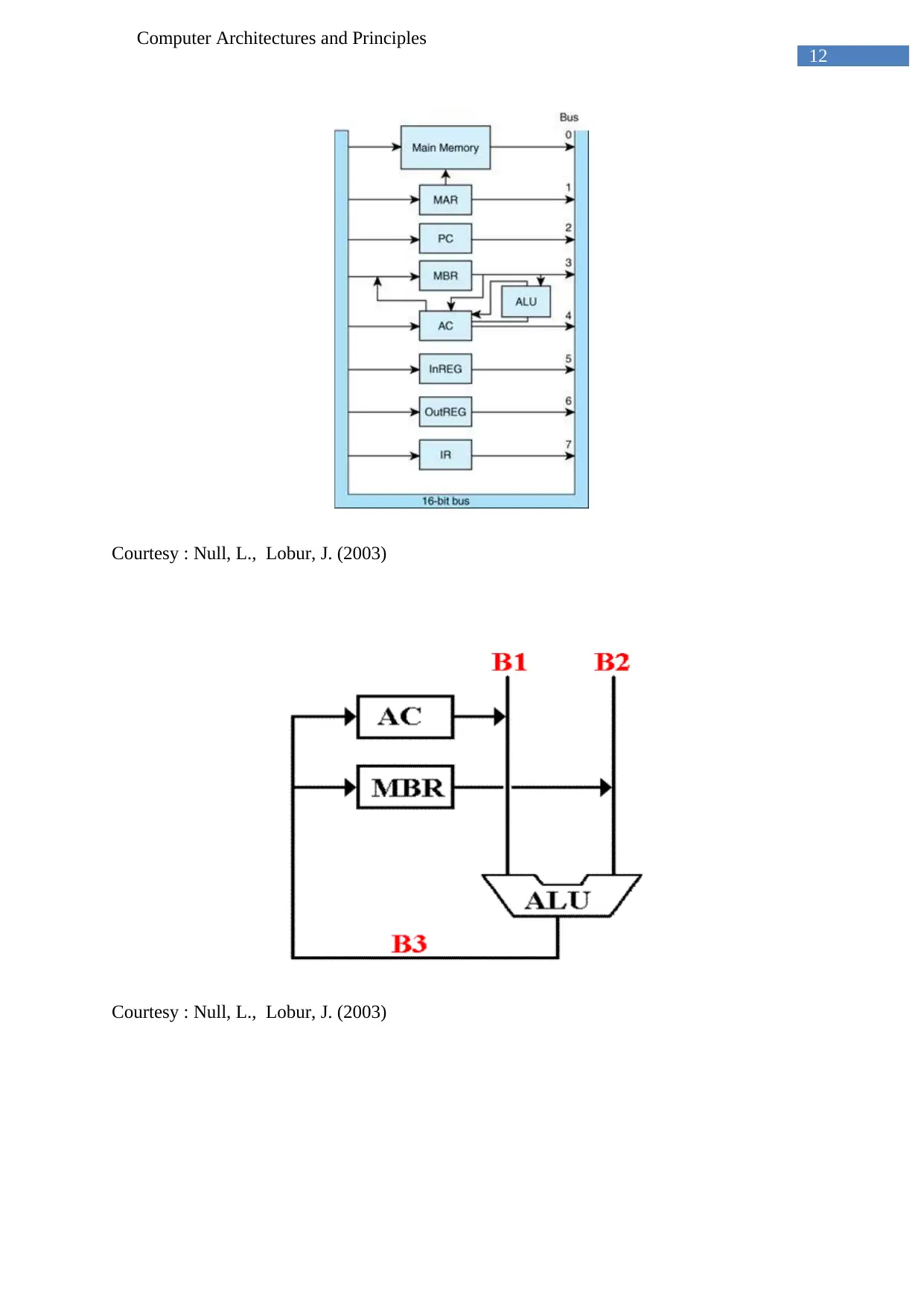

Courtesy : Null, L., Lobur, J. (2003)

Courtesy : Null, L., Lobur, J. (2003)

Computer Architectures and Principles

Courtesy : Null, L., Lobur, J. (2003)

Courtesy : Null, L., Lobur, J. (2003)

⊘ This is a preview!⊘

Do you want full access?

Subscribe today to unlock all pages.

Trusted by 1+ million students worldwide

1 out of 27

Related Documents

Your All-in-One AI-Powered Toolkit for Academic Success.

+13062052269

info@desklib.com

Available 24*7 on WhatsApp / Email

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)

Unlock your academic potential

Copyright © 2020–2026 A2Z Services. All Rights Reserved. Developed and managed by ZUCOL.