Computer Org. & Architecture Homework: Conversions & Circuit Design

VerifiedAdded on 2023/05/29

|5

|552

|237

Homework Assignment

AI Summary

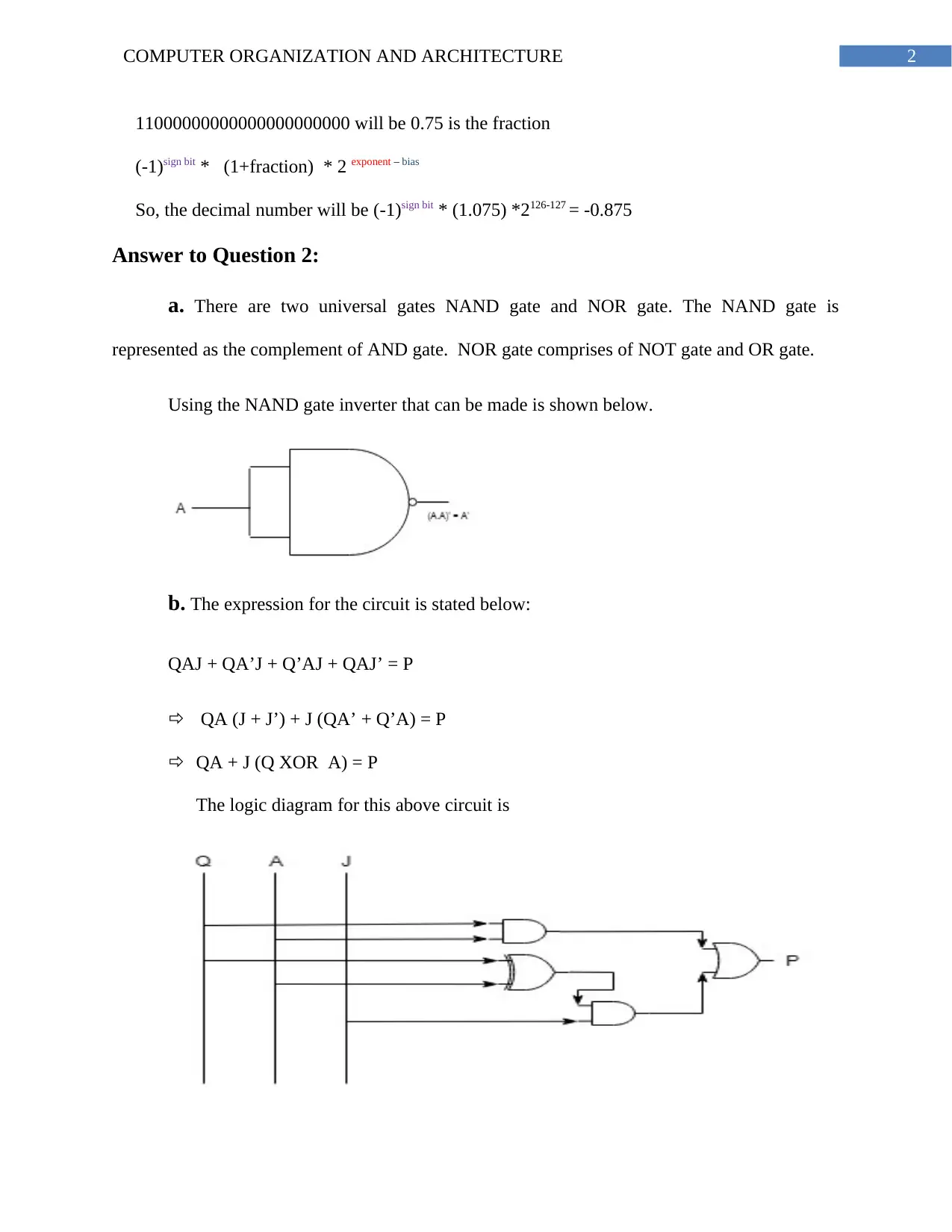

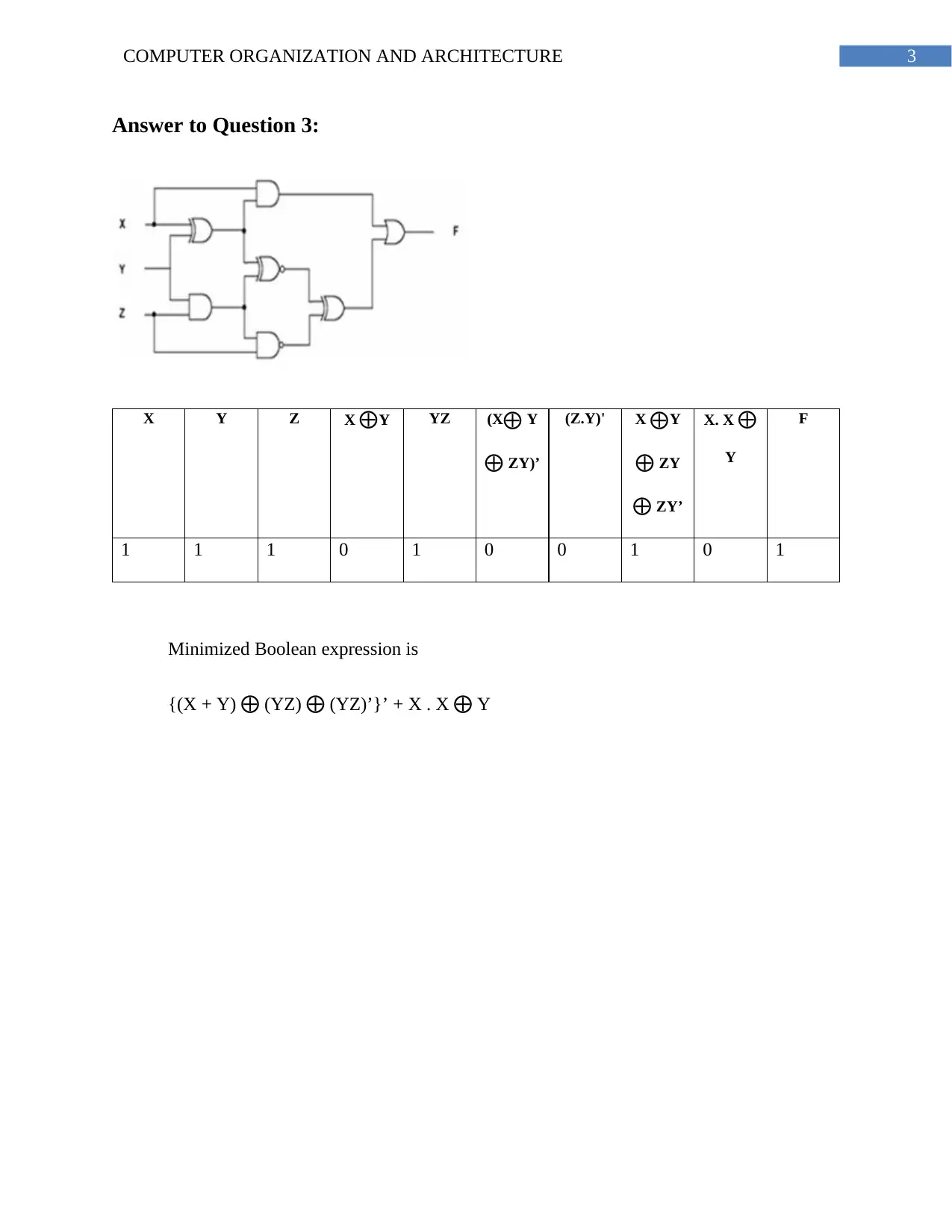

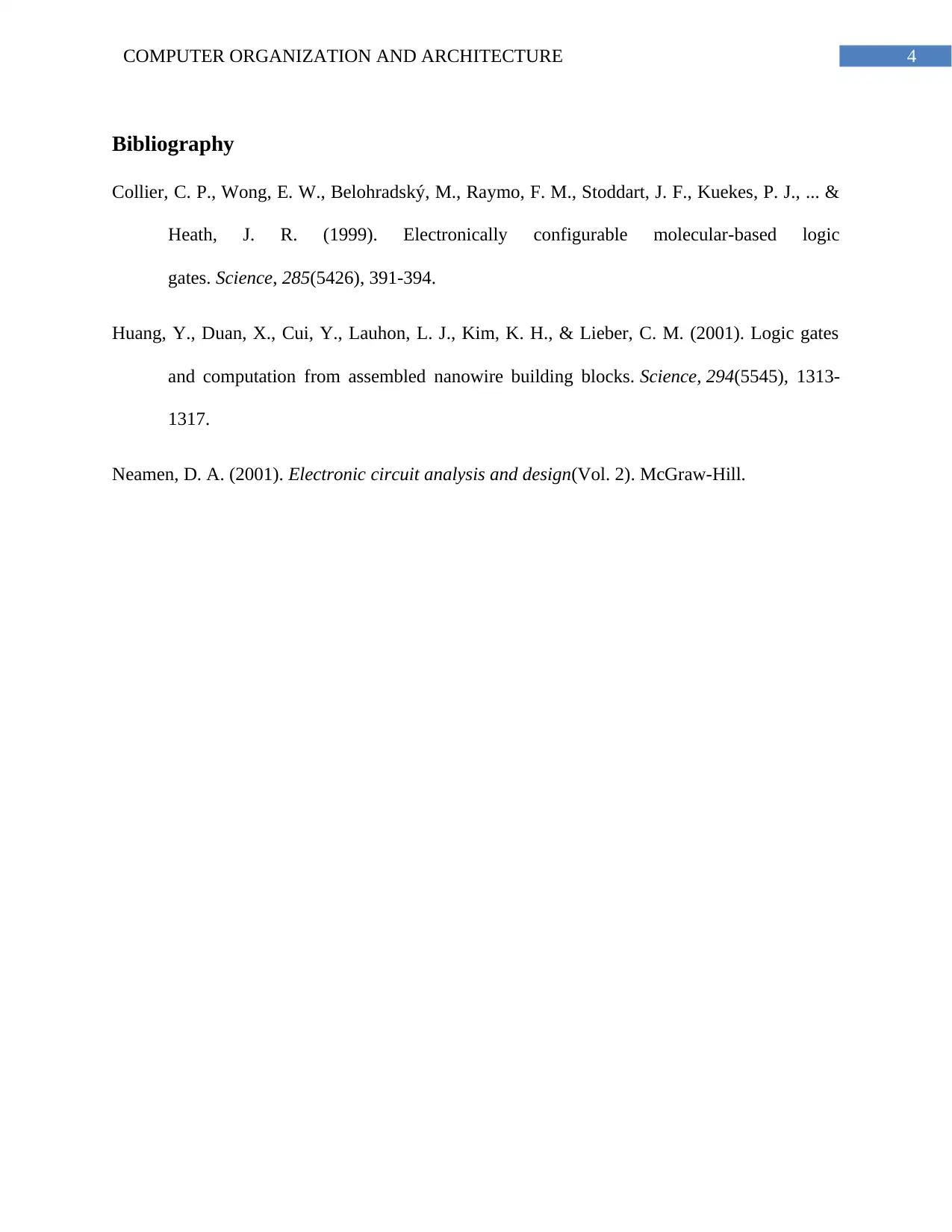

This document presents a detailed solution to a computer organization and architecture homework assignment. The solution covers various aspects of data conversion, including binary, hexadecimal, and decimal conversions, as well as two's complement representation and IEEE754 single-precision format. It also addresses the design and implementation of logic circuits using universal gates like NAND and NOR, along with the minimization of Boolean functions using truth tables and Karnaugh maps. The document includes a logic diagram and its corresponding minimized Boolean expression, demonstrating the application of Boolean algebra to simplify complex digital circuits. The solution is supplemented with a bibliography referencing relevant academic resources.

1 out of 5

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)