Computer Org & Design Homework: Number Representation & Addressing

VerifiedAdded on 2023/06/11

|14

|1990

|116

Homework Assignment

AI Summary

This assignment solution covers key concepts in computer organization and design, including signed integer representation (signed magnitude, one's complement, two's complement) and addressing modes (immediate, direct, indirect, register, register indirect, displacement with relative, base-register, and index addressing). It provides detailed explanations and calculations for converting decimal integers to hexadecimal representations using different methods and demonstrates how to determine the decimal integer represented by a given 32-bit two's complement representation. The solution also includes diagrams illustrating the various addressing modes and evaluates effective addresses based on different addressing schemes. Finally, it calculates the speedup ratio of a pipeline system compared to a non-pipeline system for processing a set of tasks.

Running head: COMPUTER ORGANIZATIONS AND DESIGN 1

Computer Organizations and Design

Student’s Name

Institutional Affiliation

Computer Organizations and Design

Student’s Name

Institutional Affiliation

Paraphrase This Document

Need a fresh take? Get an instant paraphrase of this document with our AI Paraphraser

COMPUTER ORGANIZATIONS AND DESIGN 2

You need to type in your solution except for diagrams (130 marks).

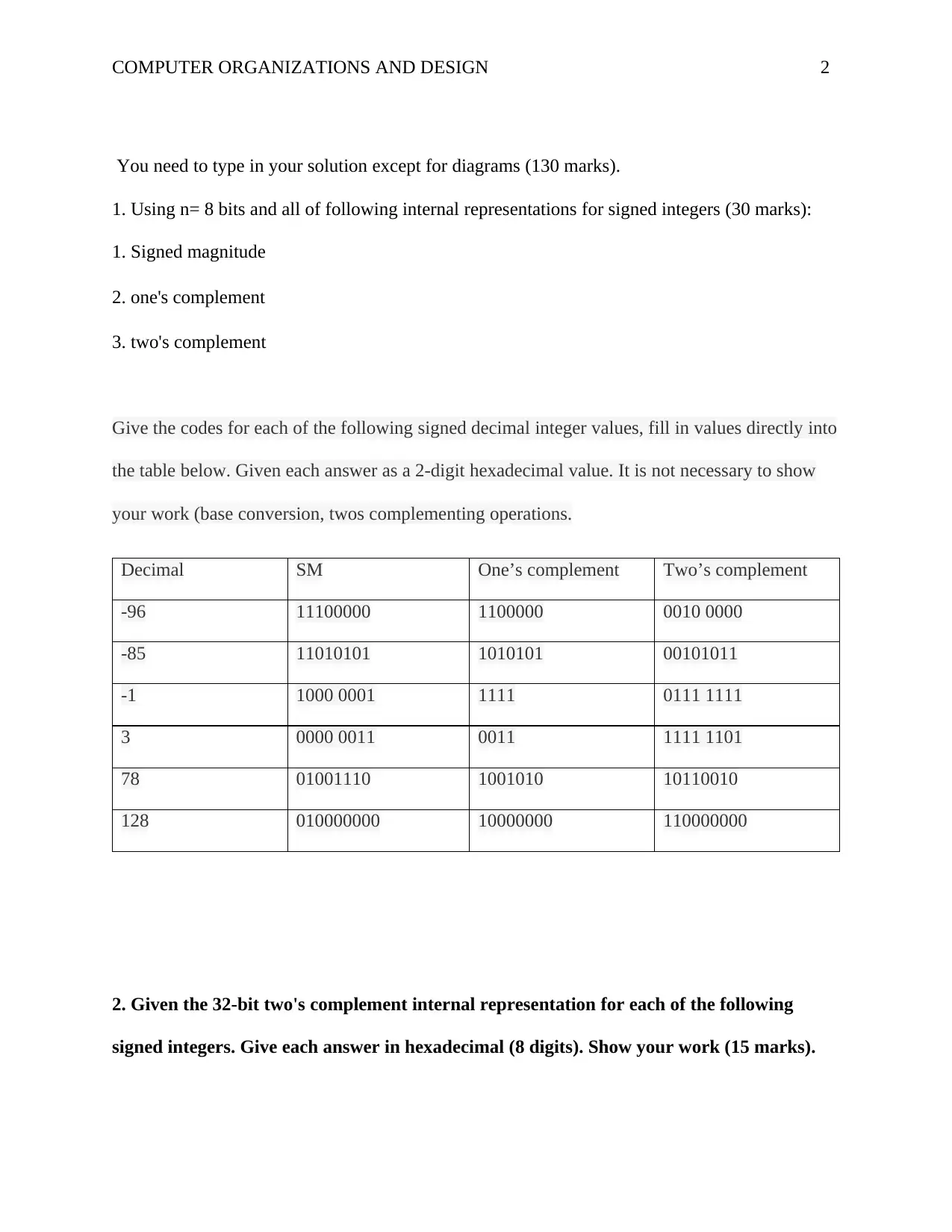

1. Using n= 8 bits and all of following internal representations for signed integers (30 marks):

1. Signed magnitude

2. one's complement

3. two's complement

Give the codes for each of the following signed decimal integer values, fill in values directly into

the table below. Given each answer as a 2-digit hexadecimal value. It is not necessary to show

your work (base conversion, twos complementing operations.

Decimal SM One’s complement Two’s complement

-96 11100000 1100000 0010 0000

-85 11010101 1010101 00101011

-1 1000 0001 1111 0111 1111

3 0000 0011 0011 1111 1101

78 01001110 1001010 10110010

128 010000000 10000000 110000000

2. Given the 32-bit two's complement internal representation for each of the following

signed integers. Give each answer in hexadecimal (8 digits). Show your work (15 marks).

You need to type in your solution except for diagrams (130 marks).

1. Using n= 8 bits and all of following internal representations for signed integers (30 marks):

1. Signed magnitude

2. one's complement

3. two's complement

Give the codes for each of the following signed decimal integer values, fill in values directly into

the table below. Given each answer as a 2-digit hexadecimal value. It is not necessary to show

your work (base conversion, twos complementing operations.

Decimal SM One’s complement Two’s complement

-96 11100000 1100000 0010 0000

-85 11010101 1010101 00101011

-1 1000 0001 1111 0111 1111

3 0000 0011 0011 1111 1101

78 01001110 1001010 10110010

128 010000000 10000000 110000000

2. Given the 32-bit two's complement internal representation for each of the following

signed integers. Give each answer in hexadecimal (8 digits). Show your work (15 marks).

COMPUTER ORGANIZATIONS AND DESIGN 3

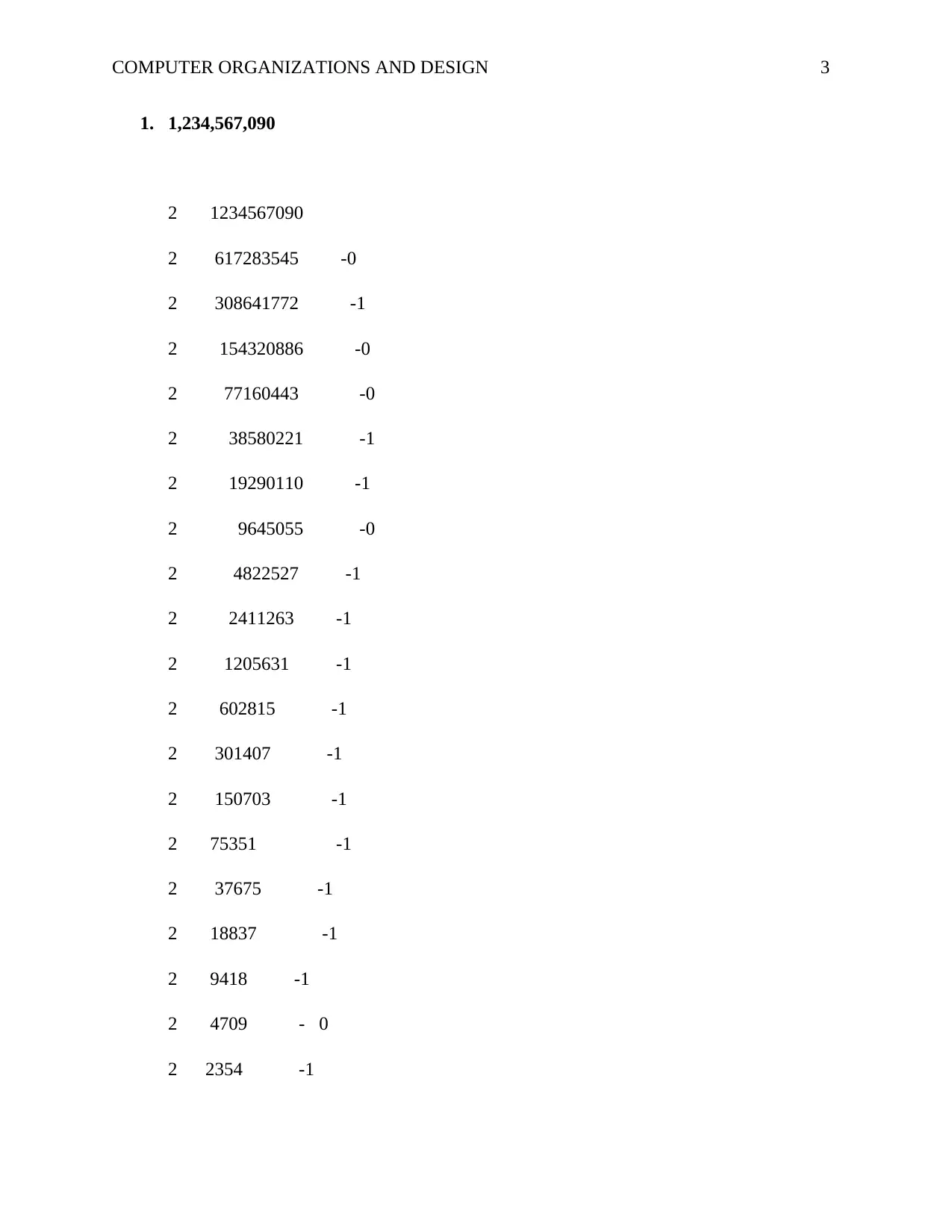

1. 1,234,567,090

2 1234567090

2 617283545 -0

2 308641772 -1

2 154320886 -0

2 77160443 -0

2 38580221 -1

2 19290110 -1

2 9645055 -0

2 4822527 -1

2 2411263 -1

2 1205631 -1

2 602815 -1

2 301407 -1

2 150703 -1

2 75351 -1

2 37675 -1

2 18837 -1

2 9418 -1

2 4709 - 0

2 2354 -1

1. 1,234,567,090

2 1234567090

2 617283545 -0

2 308641772 -1

2 154320886 -0

2 77160443 -0

2 38580221 -1

2 19290110 -1

2 9645055 -0

2 4822527 -1

2 2411263 -1

2 1205631 -1

2 602815 -1

2 301407 -1

2 150703 -1

2 75351 -1

2 37675 -1

2 18837 -1

2 9418 -1

2 4709 - 0

2 2354 -1

⊘ This is a preview!⊘

Do you want full access?

Subscribe today to unlock all pages.

Trusted by 1+ million students worldwide

COMPUTER ORGANIZATIONS AND DESIGN 4

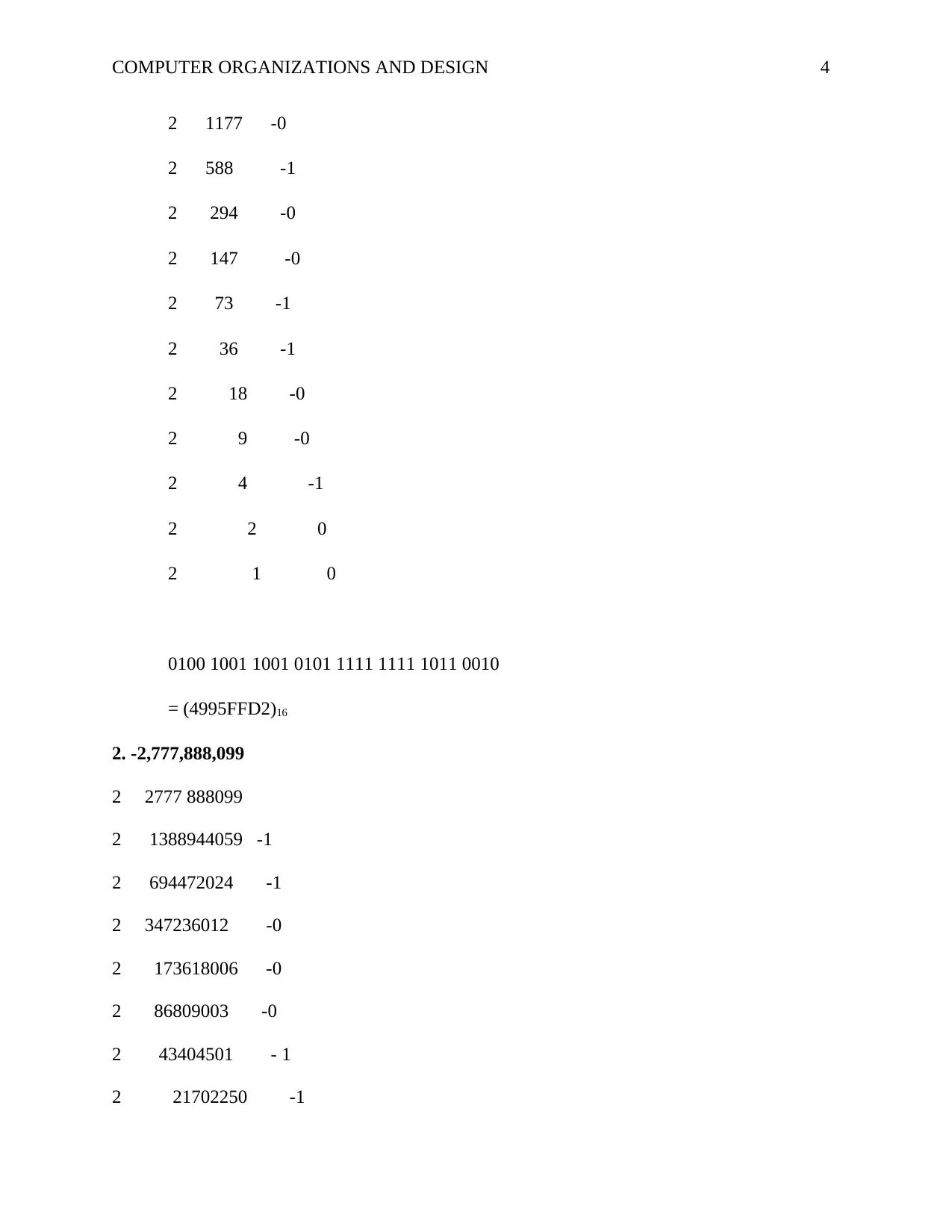

2 1177 -0

2 588 -1

2 294 -0

2 147 -0

2 73 -1

2 36 -1

2 18 -0

2 9 -0

2 4 -1

2 2 0

2 1 0

0100 1001 1001 0101 1111 1111 1011 0010

= (4995FFD2)16

2. -2,777,888,099

2 2777 888099

2 1388944059 -1

2 694472024 -1

2 347236012 -0

2 173618006 -0

2 86809003 -0

2 43404501 - 1

2 21702250 -1

2 1177 -0

2 588 -1

2 294 -0

2 147 -0

2 73 -1

2 36 -1

2 18 -0

2 9 -0

2 4 -1

2 2 0

2 1 0

0100 1001 1001 0101 1111 1111 1011 0010

= (4995FFD2)16

2. -2,777,888,099

2 2777 888099

2 1388944059 -1

2 694472024 -1

2 347236012 -0

2 173618006 -0

2 86809003 -0

2 43404501 - 1

2 21702250 -1

Paraphrase This Document

Need a fresh take? Get an instant paraphrase of this document with our AI Paraphraser

COMPUTER ORGANIZATIONS AND DESIGN 5

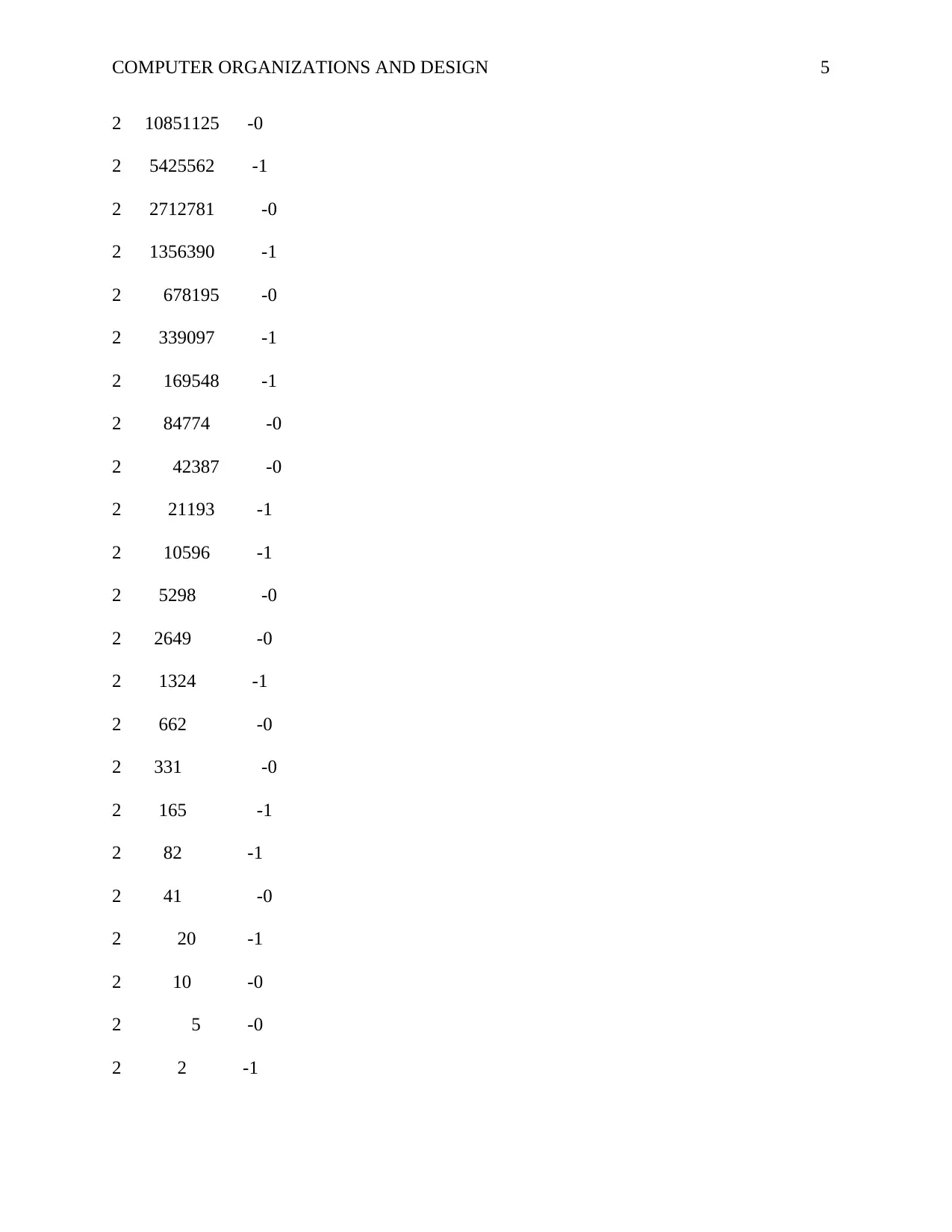

2 10851125 -0

2 5425562 -1

2 2712781 -0

2 1356390 -1

2 678195 -0

2 339097 -1

2 169548 -1

2 84774 -0

2 42387 -0

2 21193 -1

2 10596 -1

2 5298 -0

2 2649 -0

2 1324 -1

2 662 -0

2 331 -0

2 165 -1

2 82 -1

2 41 -0

2 20 -1

2 10 -0

2 5 -0

2 2 -1

2 10851125 -0

2 5425562 -1

2 2712781 -0

2 1356390 -1

2 678195 -0

2 339097 -1

2 169548 -1

2 84774 -0

2 42387 -0

2 21193 -1

2 10596 -1

2 5298 -0

2 2649 -0

2 1324 -1

2 662 -0

2 331 -0

2 165 -1

2 82 -1

2 41 -0

2 20 -1

2 10 -0

2 5 -0

2 2 -1

COMPUTER ORGANIZATIONS AND DESIGN 6

1 0

= (1101 0010 1100 1001 1001 1010 1011 0001)16

= (D2C99AB1)16

3. What signed decimal integer is represented by each of the following 32-bit two's

complement representation? Show your work (15 marks).

1. 7E45E012

(7E45E012)16 = (0111 1111 0100 0101 1110 0000 0001 0010)2

1*230 +1*229 +1*228 + 1*227 +1*226+1*225 +1*224 + 0*223 +1*222+0*221 +0*220

+ 0*219 +1*218+0*217 +1*216 + 1*215+1*214+1*213 +0*212 + 0*211 +0*210+0*29 +0*28

+ 0*27 +0*26+0*25 +1*24 + 0*23 +0*22+1*21 +0*20

= 2,135,285,778

2. (EA66110B)16

= (1111 1010 0110 0110 0001 0001 0000 1011)2

The first letter has a negative (-ve)

1*230 +1*229 +1*228 + 1*227 +0*226+1*225 +0*224 + 0*223 +0*222+1*221 +0*220

+ 0*219 +1*218+1*217 +0*216 + 0*215+0*214+0*213 +1*212 + 0*211 +0*210+0*29 +1*28

+ 0*27 +0*26+0*25 +0*24 + 1*23 +0*22+1*21 +1*20

= -2,053,509,387

4. Using figures to illustrate the following addressing modes (30 marks):

Immediate addressing

Direct addressing

Indirect addressing

1 0

= (1101 0010 1100 1001 1001 1010 1011 0001)16

= (D2C99AB1)16

3. What signed decimal integer is represented by each of the following 32-bit two's

complement representation? Show your work (15 marks).

1. 7E45E012

(7E45E012)16 = (0111 1111 0100 0101 1110 0000 0001 0010)2

1*230 +1*229 +1*228 + 1*227 +1*226+1*225 +1*224 + 0*223 +1*222+0*221 +0*220

+ 0*219 +1*218+0*217 +1*216 + 1*215+1*214+1*213 +0*212 + 0*211 +0*210+0*29 +0*28

+ 0*27 +0*26+0*25 +1*24 + 0*23 +0*22+1*21 +0*20

= 2,135,285,778

2. (EA66110B)16

= (1111 1010 0110 0110 0001 0001 0000 1011)2

The first letter has a negative (-ve)

1*230 +1*229 +1*228 + 1*227 +0*226+1*225 +0*224 + 0*223 +0*222+1*221 +0*220

+ 0*219 +1*218+1*217 +0*216 + 0*215+0*214+0*213 +1*212 + 0*211 +0*210+0*29 +1*28

+ 0*27 +0*26+0*25 +0*24 + 1*23 +0*22+1*21 +1*20

= -2,053,509,387

4. Using figures to illustrate the following addressing modes (30 marks):

Immediate addressing

Direct addressing

Indirect addressing

⊘ This is a preview!⊘

Do you want full access?

Subscribe today to unlock all pages.

Trusted by 1+ million students worldwide

COMPUTER ORGANIZATIONS AND DESIGN 7

Register addressing

Register indirect addressing

Displacement addressing

Relative addressing

Base-register addressing

index addressing

Solution

Immediate addressing mode involves data following instructions. As an illustration, the

data that has to be used is already in the instruction itself. For instance, MOV A, #25H (This

instruction moves data 25H to the accumulator. However, the # sign shows that the preceding

term is data not address)

Instruction

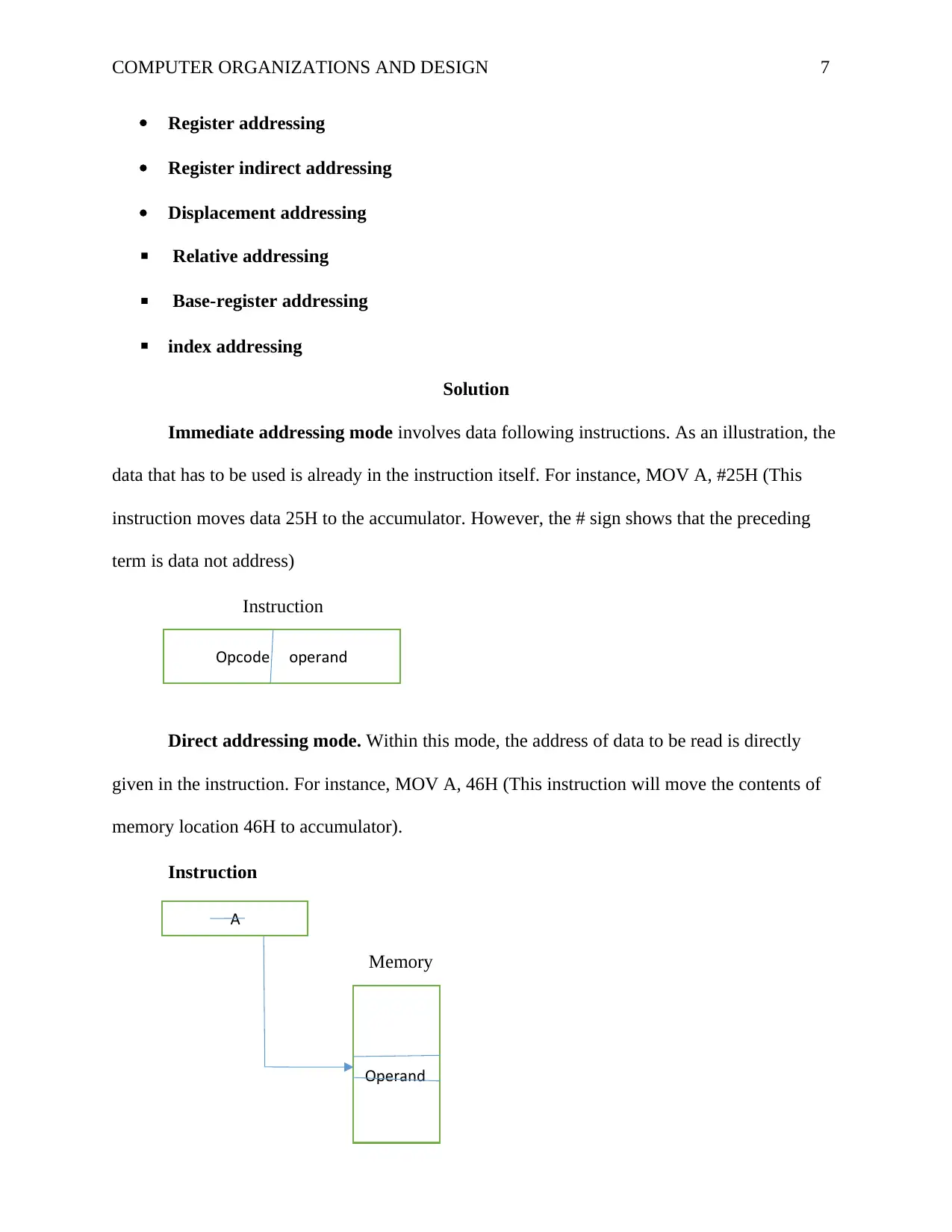

Direct addressing mode. Within this mode, the address of data to be read is directly

given in the instruction. For instance, MOV A, 46H (This instruction will move the contents of

memory location 46H to accumulator).

Instruction

Memory

A

Operand

Opcode operand

Register addressing

Register indirect addressing

Displacement addressing

Relative addressing

Base-register addressing

index addressing

Solution

Immediate addressing mode involves data following instructions. As an illustration, the

data that has to be used is already in the instruction itself. For instance, MOV A, #25H (This

instruction moves data 25H to the accumulator. However, the # sign shows that the preceding

term is data not address)

Instruction

Direct addressing mode. Within this mode, the address of data to be read is directly

given in the instruction. For instance, MOV A, 46H (This instruction will move the contents of

memory location 46H to accumulator).

Instruction

Memory

A

Operand

Opcode operand

Paraphrase This Document

Need a fresh take? Get an instant paraphrase of this document with our AI Paraphraser

COMPUTER ORGANIZATIONS AND DESIGN 8

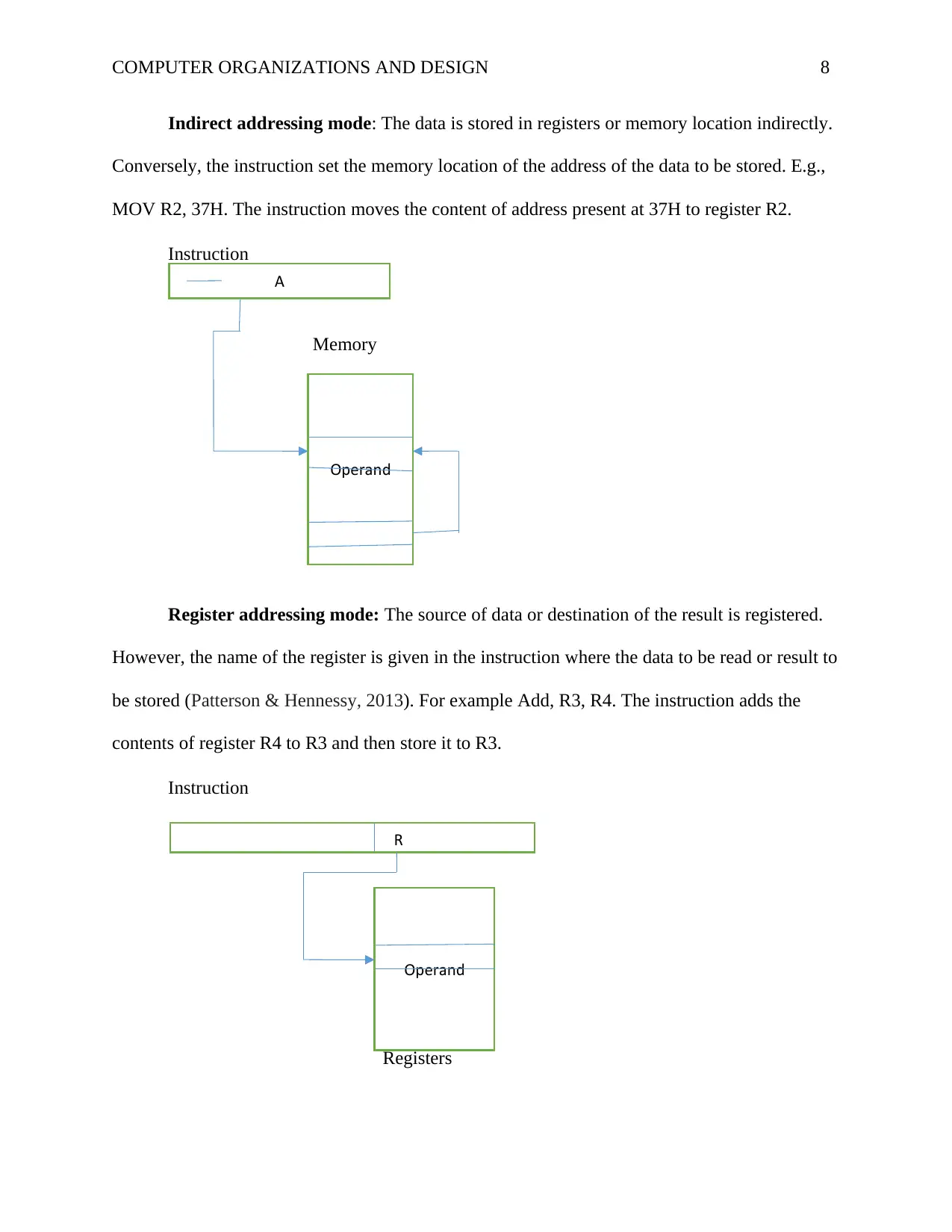

Indirect addressing mode: The data is stored in registers or memory location indirectly.

Conversely, the instruction set the memory location of the address of the data to be stored. E.g.,

MOV R2, 37H. The instruction moves the content of address present at 37H to register R2.

Instruction

Memory

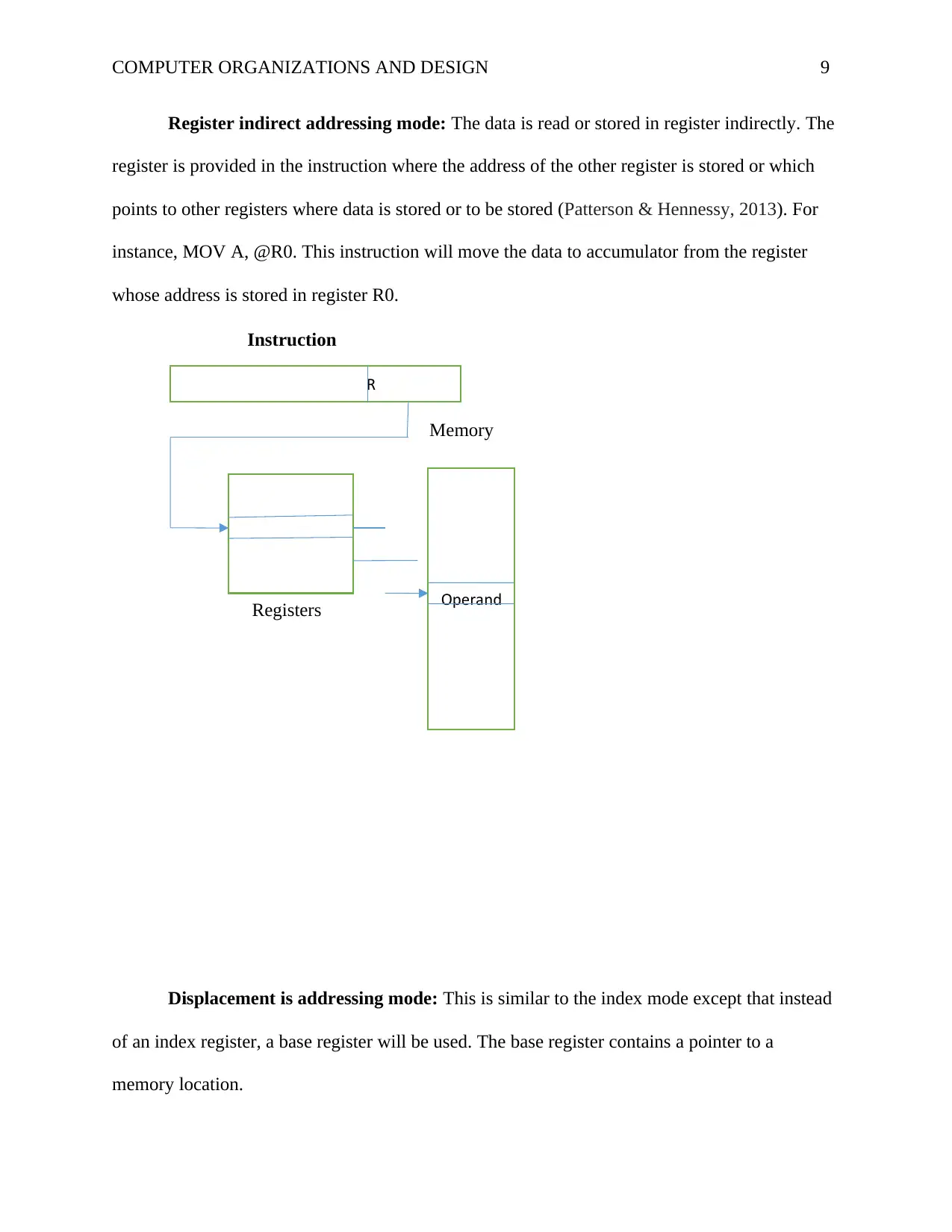

Register addressing mode: The source of data or destination of the result is registered.

However, the name of the register is given in the instruction where the data to be read or result to

be stored (Patterson & Hennessy, 2013). For example Add, R3, R4. The instruction adds the

contents of register R4 to R3 and then store it to R3.

Instruction

Registers

A

Operand

R

Operand

Indirect addressing mode: The data is stored in registers or memory location indirectly.

Conversely, the instruction set the memory location of the address of the data to be stored. E.g.,

MOV R2, 37H. The instruction moves the content of address present at 37H to register R2.

Instruction

Memory

Register addressing mode: The source of data or destination of the result is registered.

However, the name of the register is given in the instruction where the data to be read or result to

be stored (Patterson & Hennessy, 2013). For example Add, R3, R4. The instruction adds the

contents of register R4 to R3 and then store it to R3.

Instruction

Registers

A

Operand

R

Operand

COMPUTER ORGANIZATIONS AND DESIGN 9

Register indirect addressing mode: The data is read or stored in register indirectly. The

register is provided in the instruction where the address of the other register is stored or which

points to other registers where data is stored or to be stored (Patterson & Hennessy, 2013). For

instance, MOV A, @R0. This instruction will move the data to accumulator from the register

whose address is stored in register R0.

Instruction

Memory

Registers

Displacement is addressing mode: This is similar to the index mode except that instead

of an index register, a base register will be used. The base register contains a pointer to a

memory location.

R

Operand

Register indirect addressing mode: The data is read or stored in register indirectly. The

register is provided in the instruction where the address of the other register is stored or which

points to other registers where data is stored or to be stored (Patterson & Hennessy, 2013). For

instance, MOV A, @R0. This instruction will move the data to accumulator from the register

whose address is stored in register R0.

Instruction

Memory

Registers

Displacement is addressing mode: This is similar to the index mode except that instead

of an index register, a base register will be used. The base register contains a pointer to a

memory location.

R

Operand

⊘ This is a preview!⊘

Do you want full access?

Subscribe today to unlock all pages.

Trusted by 1+ million students worldwide

COMPUTER ORGANIZATIONS AND DESIGN 10

Instruction

RRRRRRRRRRRRFFF

Memory

Registers

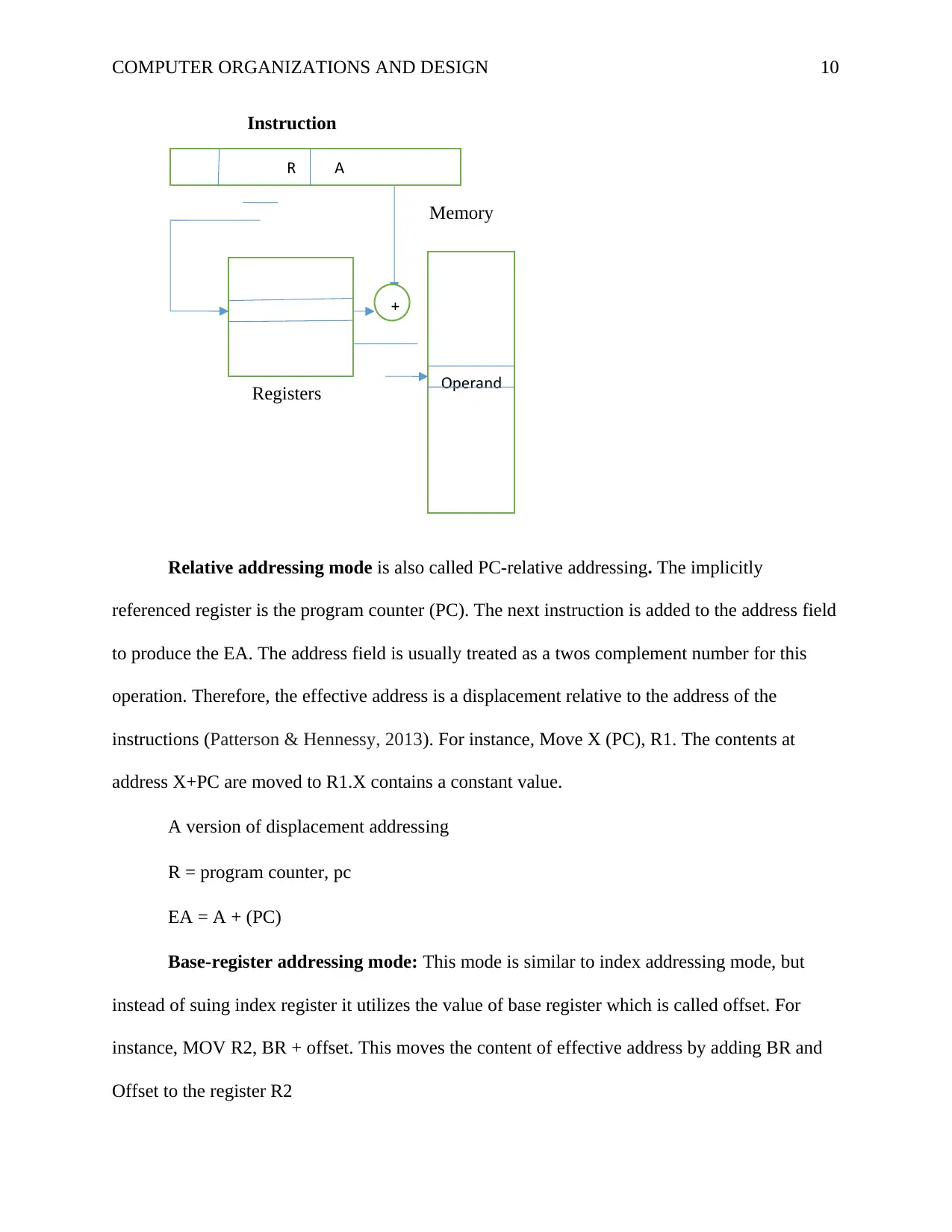

Relative addressing mode is also called PC-relative addressing. The implicitly

referenced register is the program counter (PC). The next instruction is added to the address field

to produce the EA. The address field is usually treated as a twos complement number for this

operation. Therefore, the effective address is a displacement relative to the address of the

instructions (Patterson & Hennessy, 2013). For instance, Move X (PC), R1. The contents at

address X+PC are moved to R1.X contains a constant value.

A version of displacement addressing

R = program counter, pc

EA = A + (PC)

Base-register addressing mode: This mode is similar to index addressing mode, but

instead of suing index register it utilizes the value of base register which is called offset. For

instance, MOV R2, BR + offset. This moves the content of effective address by adding BR and

Offset to the register R2

R A

Operand

+

Instruction

RRRRRRRRRRRRFFF

Memory

Registers

Relative addressing mode is also called PC-relative addressing. The implicitly

referenced register is the program counter (PC). The next instruction is added to the address field

to produce the EA. The address field is usually treated as a twos complement number for this

operation. Therefore, the effective address is a displacement relative to the address of the

instructions (Patterson & Hennessy, 2013). For instance, Move X (PC), R1. The contents at

address X+PC are moved to R1.X contains a constant value.

A version of displacement addressing

R = program counter, pc

EA = A + (PC)

Base-register addressing mode: This mode is similar to index addressing mode, but

instead of suing index register it utilizes the value of base register which is called offset. For

instance, MOV R2, BR + offset. This moves the content of effective address by adding BR and

Offset to the register R2

R A

Operand

+

Paraphrase This Document

Need a fresh take? Get an instant paraphrase of this document with our AI Paraphraser

COMPUTER ORGANIZATIONS AND DESIGN 11

A holds displacement

R holds pointer to base address

R may be explicit or implicit

Index addressing is the address of the operand which is obtained by adding to the

contents of the general register a constant value. However, the number of the index register along

with the constant value is included in the instruction code.

A = base

R = displacement

EA = A + R

This is therefore good for accessing arrays

5 An instruction is stored at location 200 with its address field at location 201. The address

field has the value 300. A processor register R1 contains the number 100. Evaluate the

effective address if the addressing mode of the instruction is a) direct; b) immediate; c)

relative; d) register indirect; e) index with R1 as the index register (25 marks)

The instruction is stored at location 200 with address field at 201. However, the address

field has the value 300. The processor register R1 has the number 100.

(a). Direct.

To evaluate our addressing mode as direct, we pull the number from the value of the address

field. In this case, the direct is 300.

(b). Immediate addressing mode

For the case of immediate addressing mode, we seek out the instruction stored location.

In our case is 200 which is the answer.

A holds displacement

R holds pointer to base address

R may be explicit or implicit

Index addressing is the address of the operand which is obtained by adding to the

contents of the general register a constant value. However, the number of the index register along

with the constant value is included in the instruction code.

A = base

R = displacement

EA = A + R

This is therefore good for accessing arrays

5 An instruction is stored at location 200 with its address field at location 201. The address

field has the value 300. A processor register R1 contains the number 100. Evaluate the

effective address if the addressing mode of the instruction is a) direct; b) immediate; c)

relative; d) register indirect; e) index with R1 as the index register (25 marks)

The instruction is stored at location 200 with address field at 201. However, the address

field has the value 300. The processor register R1 has the number 100.

(a). Direct.

To evaluate our addressing mode as direct, we pull the number from the value of the address

field. In this case, the direct is 300.

(b). Immediate addressing mode

For the case of immediate addressing mode, we seek out the instruction stored location.

In our case is 200 which is the answer.

COMPUTER ORGANIZATIONS AND DESIGN 12

(c) Relative

Concerning relative location, the formula for calculation is as follows:

Addressing Field Location + Processor Register = Relative Location

In this case, it is 201+ 100 = 301.

(d). Register indirect

The effective address for indirect register mode is 100.

(e). Index with R1 as the index register

The formula for getting this is;

Address Field Value + Processor Register = Indexed Location

300 + 100 = 400

6. A nonpipleline system takes 40ns to process a task. The same task can be processed in a

six-segment pipeline with a clock cycle of 10 ns. Determine the speedup ratio of the pipeline

for 80 tasks. What is the maximum speedup that can be achieved? (15 marks

Solution

The speedup ratio is defined as the speedup of a pipeline processing concerning the

equivalent non-pipeline processing. The below is the formula for getting speed up ratio

S = ten/ (K+n-1) tp

The number of tasks n = 80

For nonpipeline:

Time is taken by pipeline to process a task in = 40 ns

Total time is taken by pipeline to process 80 task = ten

= 80*40

= 3200 ns

(c) Relative

Concerning relative location, the formula for calculation is as follows:

Addressing Field Location + Processor Register = Relative Location

In this case, it is 201+ 100 = 301.

(d). Register indirect

The effective address for indirect register mode is 100.

(e). Index with R1 as the index register

The formula for getting this is;

Address Field Value + Processor Register = Indexed Location

300 + 100 = 400

6. A nonpipleline system takes 40ns to process a task. The same task can be processed in a

six-segment pipeline with a clock cycle of 10 ns. Determine the speedup ratio of the pipeline

for 80 tasks. What is the maximum speedup that can be achieved? (15 marks

Solution

The speedup ratio is defined as the speedup of a pipeline processing concerning the

equivalent non-pipeline processing. The below is the formula for getting speed up ratio

S = ten/ (K+n-1) tp

The number of tasks n = 80

For nonpipeline:

Time is taken by pipeline to process a task in = 40 ns

Total time is taken by pipeline to process 80 task = ten

= 80*40

= 3200 ns

⊘ This is a preview!⊘

Do you want full access?

Subscribe today to unlock all pages.

Trusted by 1+ million students worldwide

1 out of 14

Related Documents

Your All-in-One AI-Powered Toolkit for Academic Success.

+13062052269

info@desklib.com

Available 24*7 on WhatsApp / Email

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)

Unlock your academic potential

Copyright © 2020–2026 A2Z Services. All Rights Reserved. Developed and managed by ZUCOL.