Digital Electronics Laboratory Assignment - FEEE Module Solution

VerifiedAdded on 2022/08/25

|6

|816

|26

Homework Assignment

AI Summary

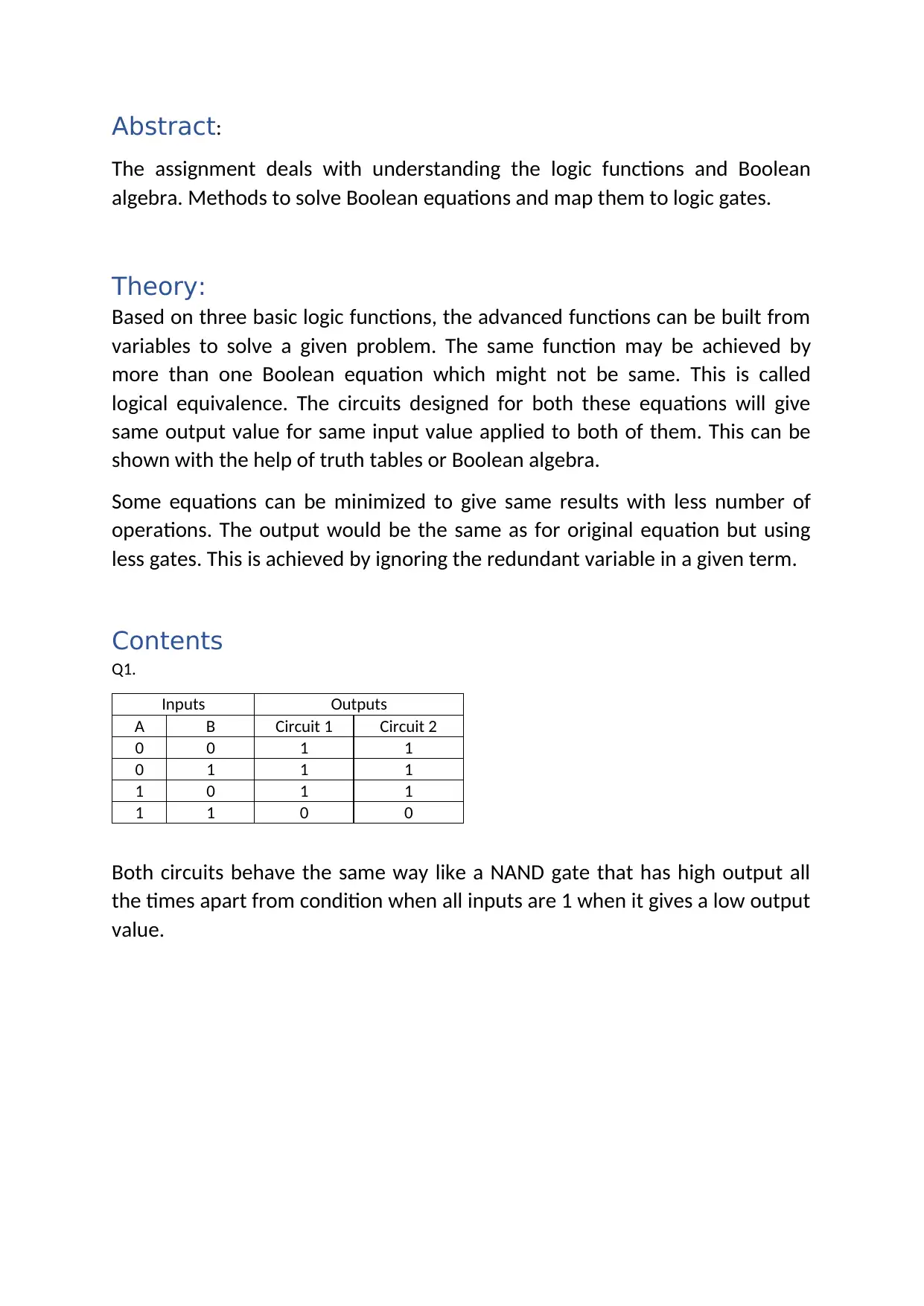

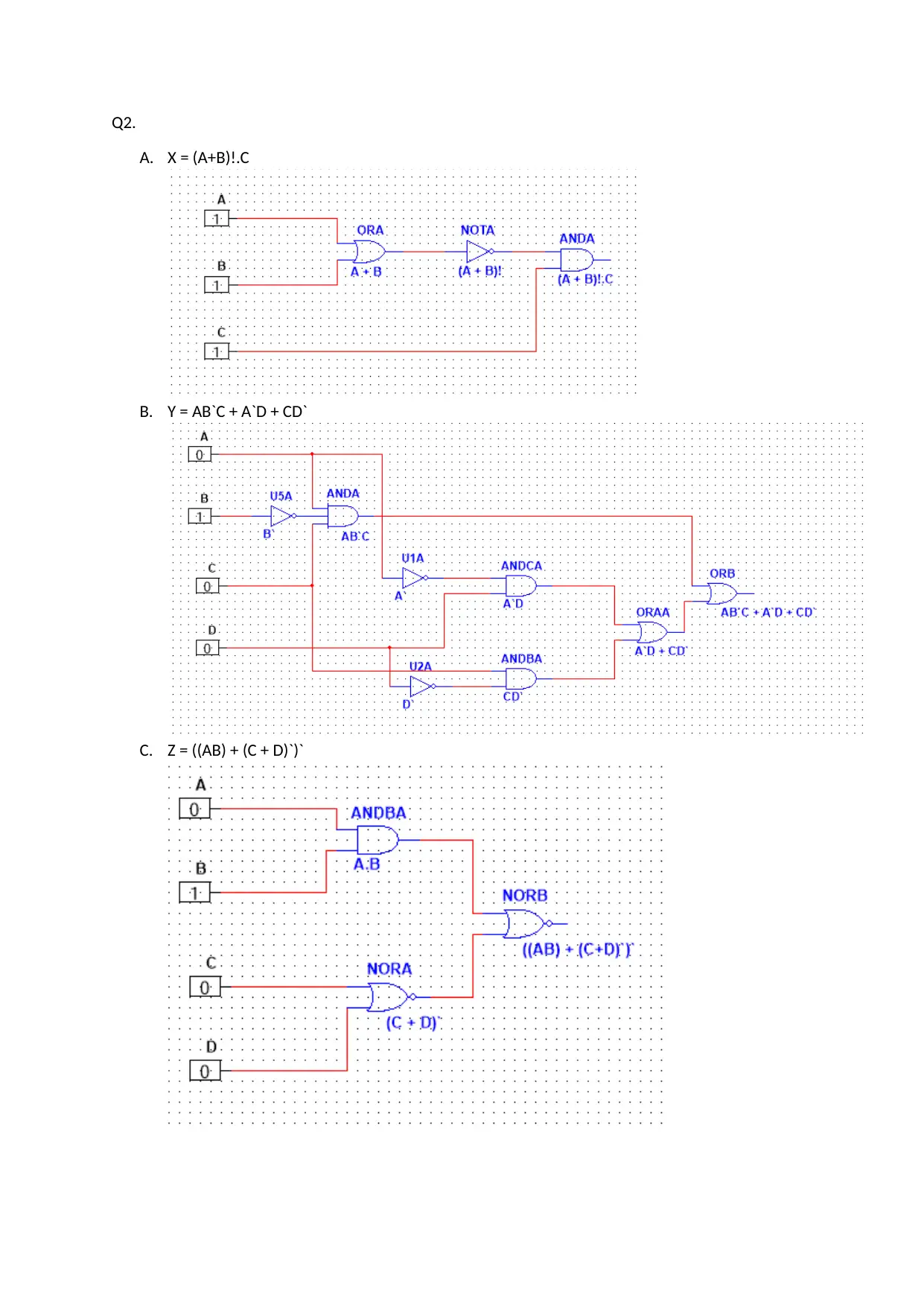

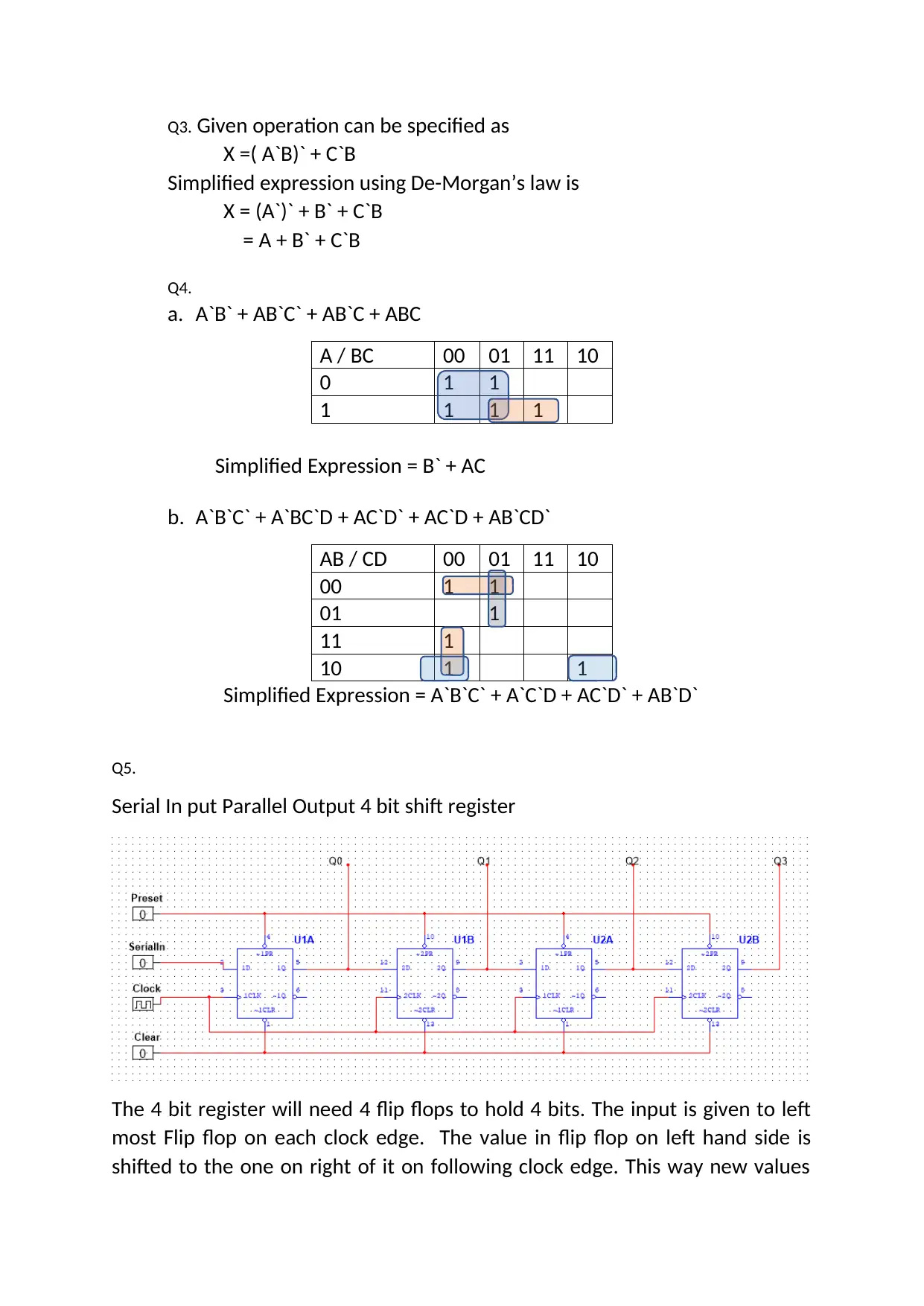

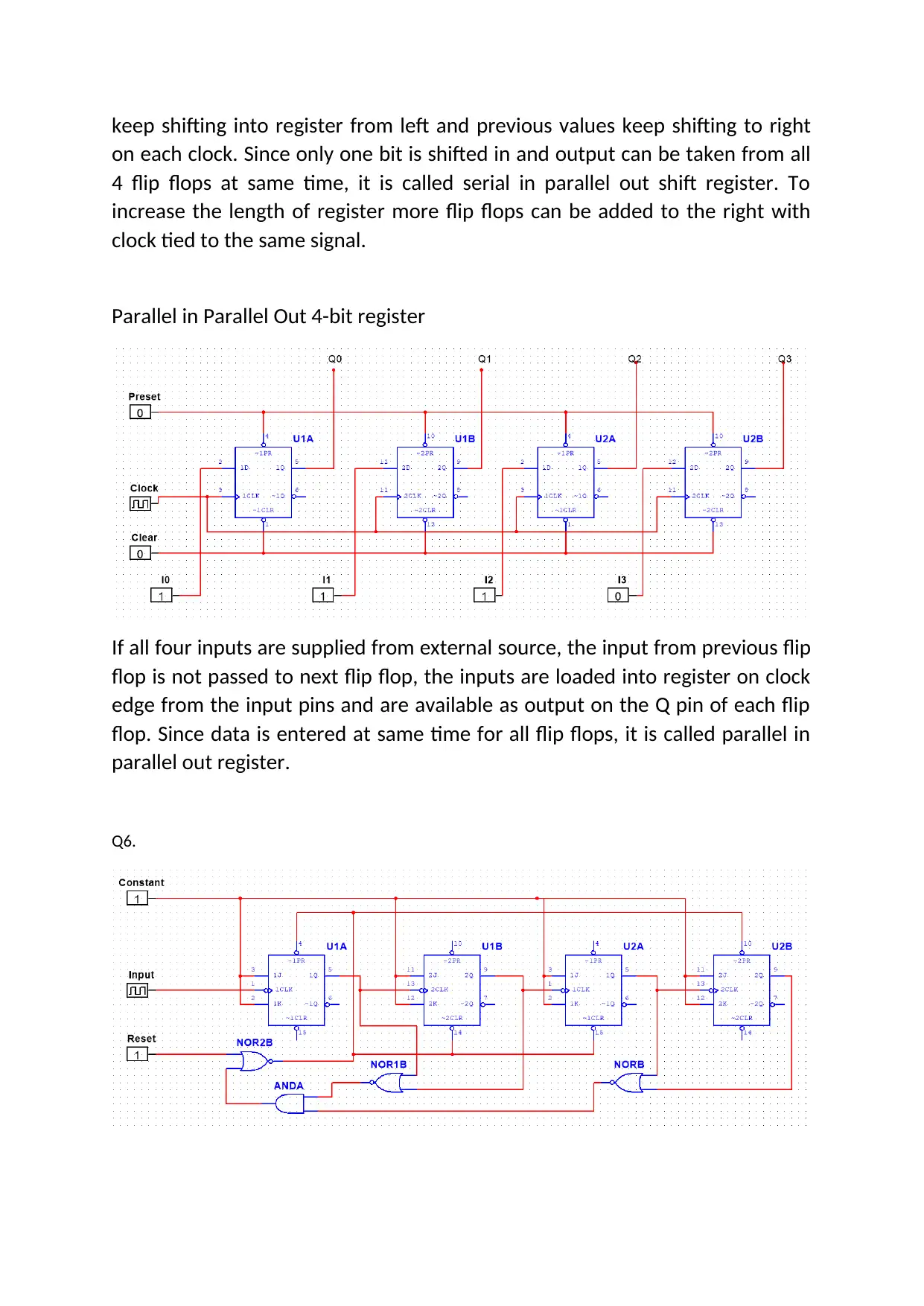

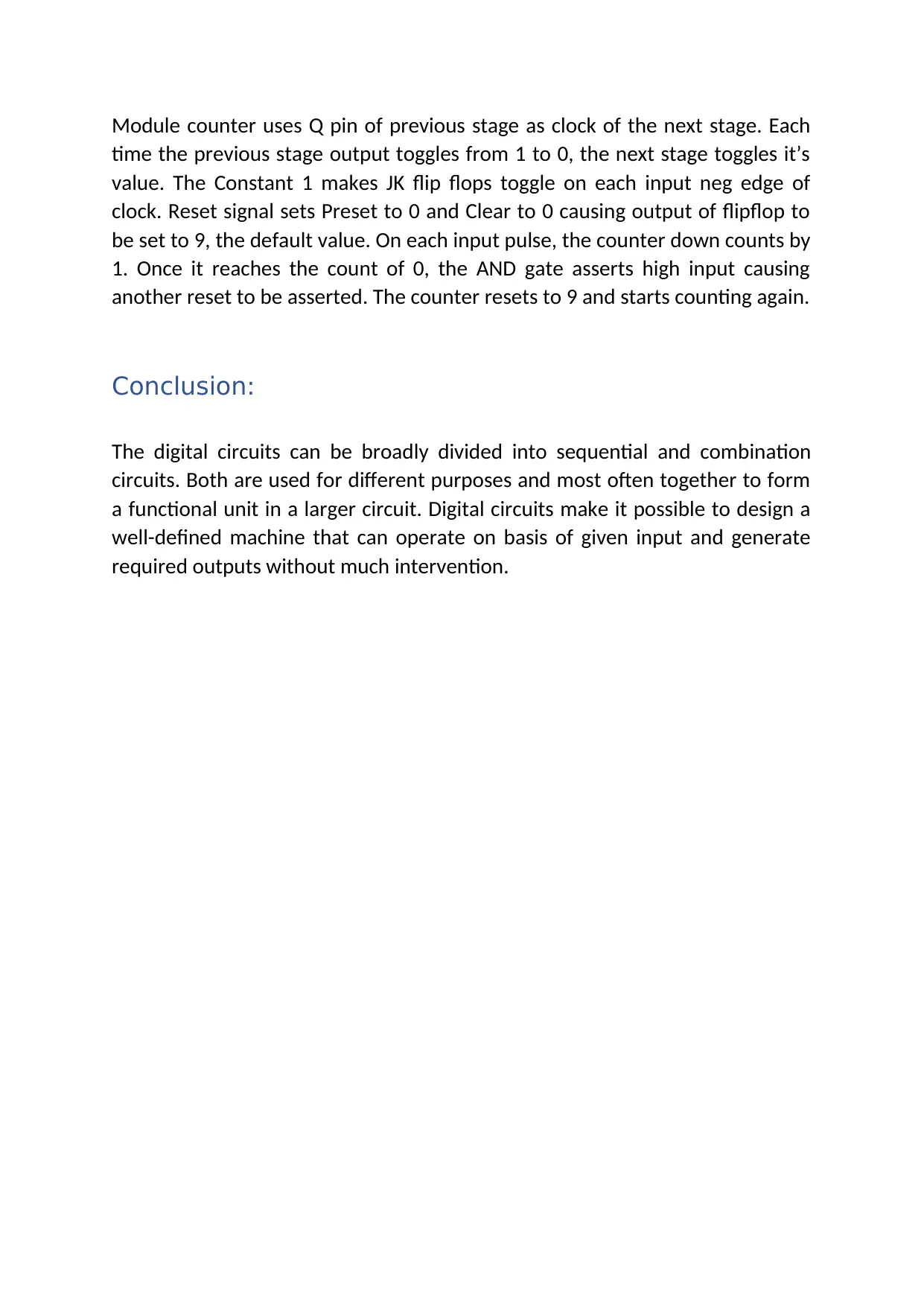

This assignment solution covers fundamental concepts in digital electronics, including logic functions, Boolean algebra, and circuit design. The solution addresses several key areas, starting with the analysis of logic gate behavior, demonstrating logical equivalence through truth tables and Boolean algebra. The assignment then delves into simplifying Boolean expressions using techniques like De Morgan's law and Karnaugh maps. Furthermore, the solution explores the design and operation of shift registers, specifically serial-in parallel-out and parallel-in parallel-out configurations. Finally, the assignment concludes with an examination of module counters, illustrating their functionality and implementation using JK flip-flops and reset mechanisms. The solution provides a comprehensive understanding of digital circuit design principles.

1 out of 6

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)