Princeton's IAS Computer: Structure, Operation, and Instruction Cycles

VerifiedAdded on 2022/12/29

|15

|606

|23

Presentation

AI Summary

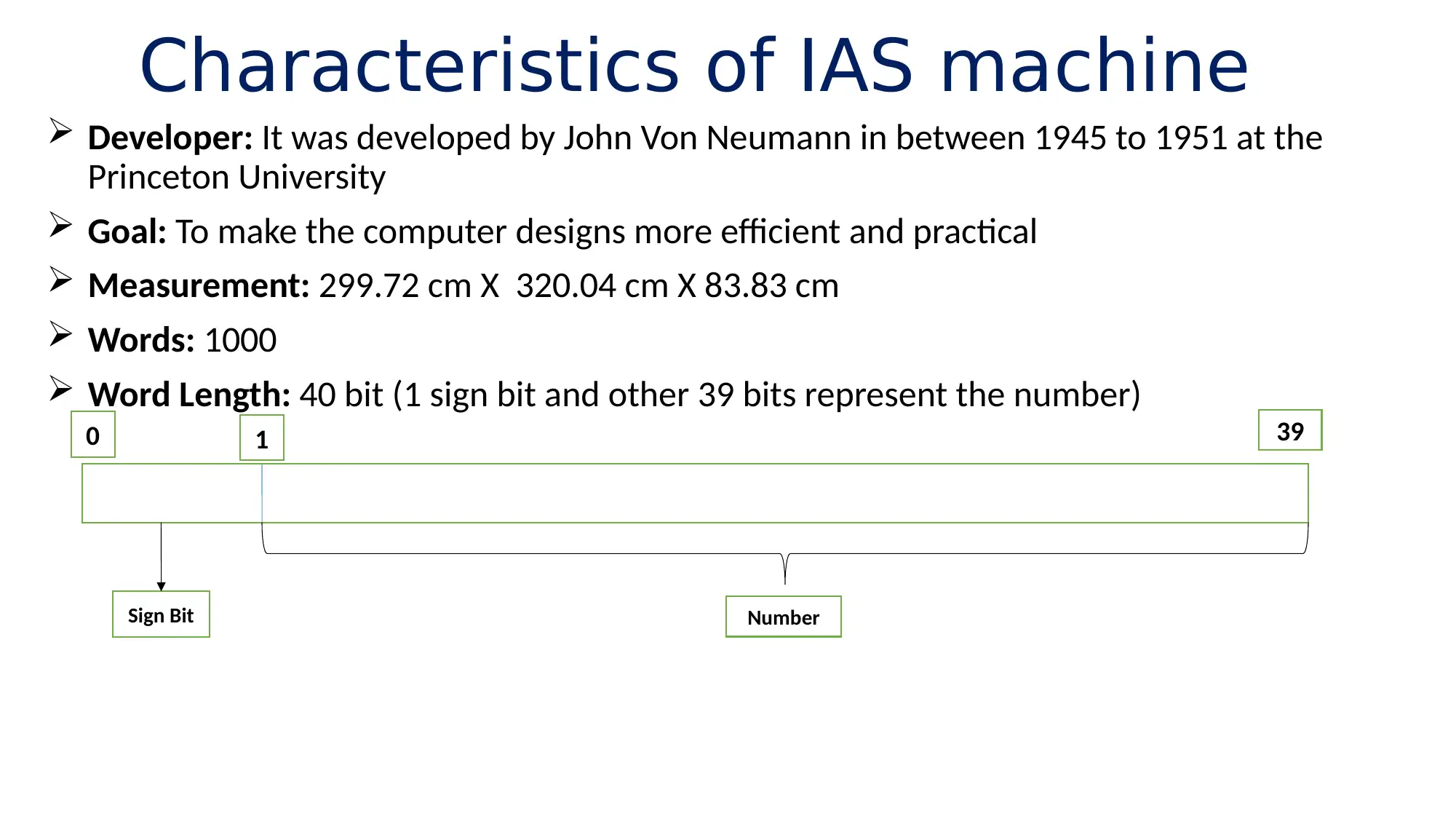

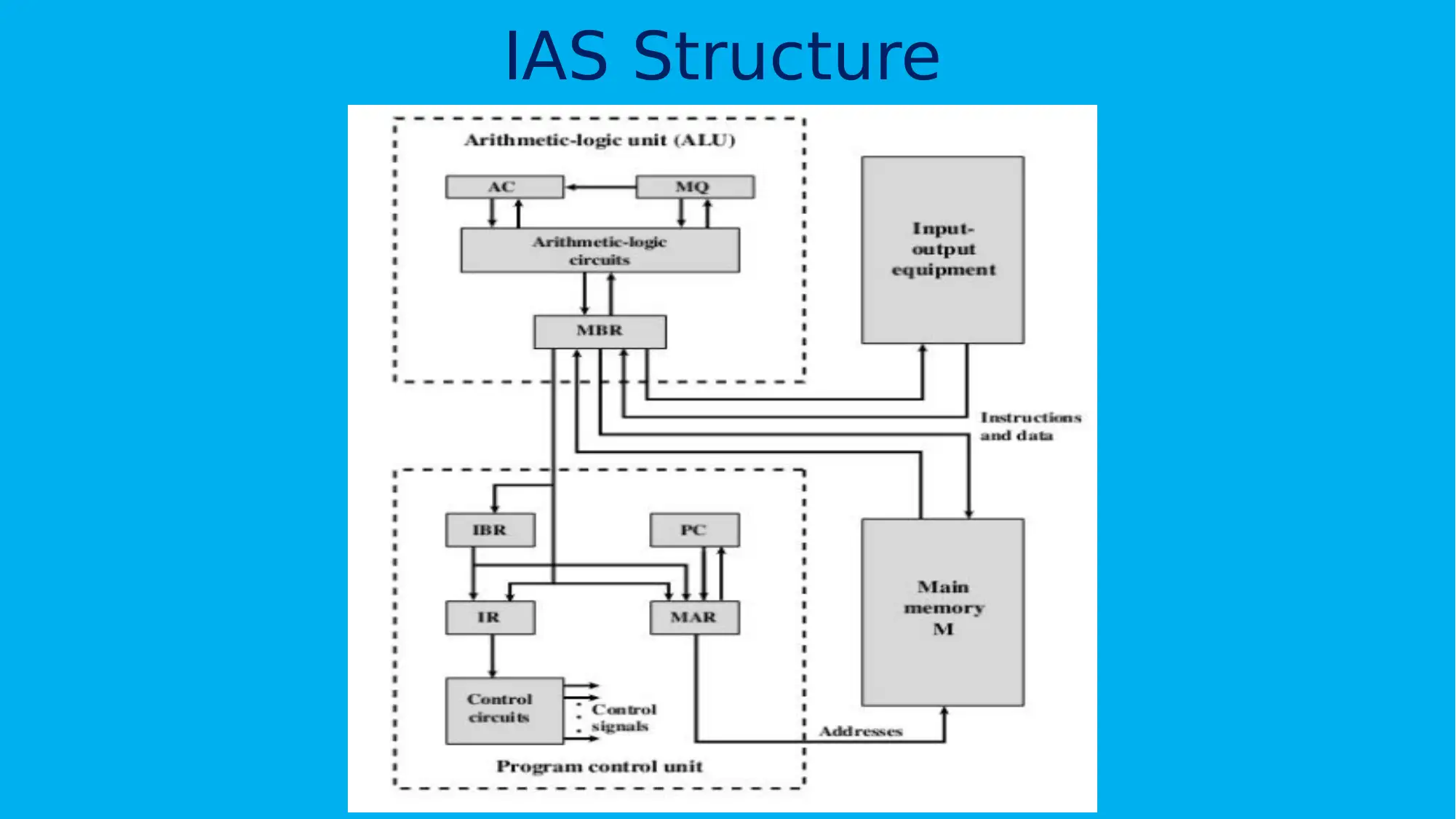

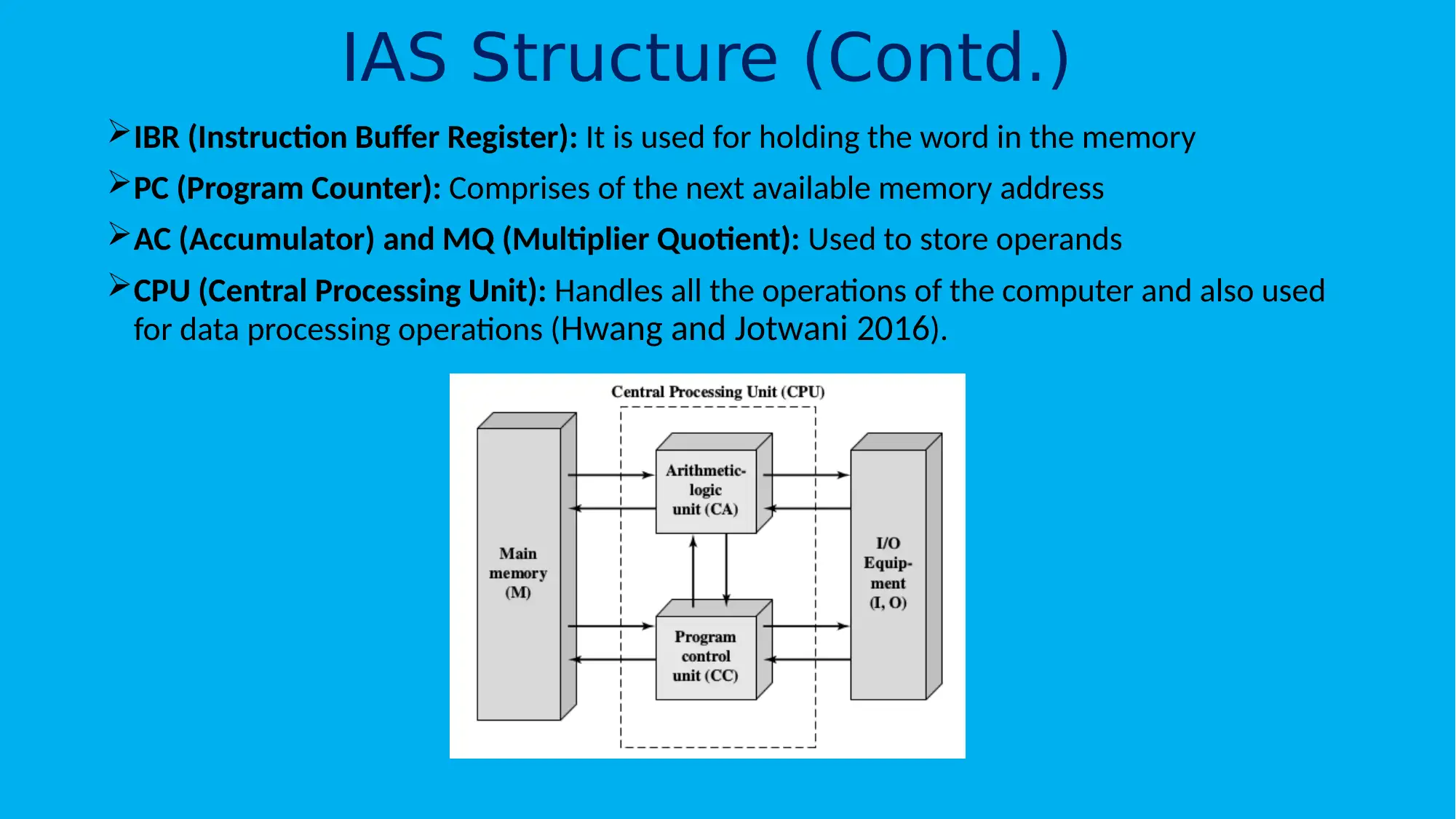

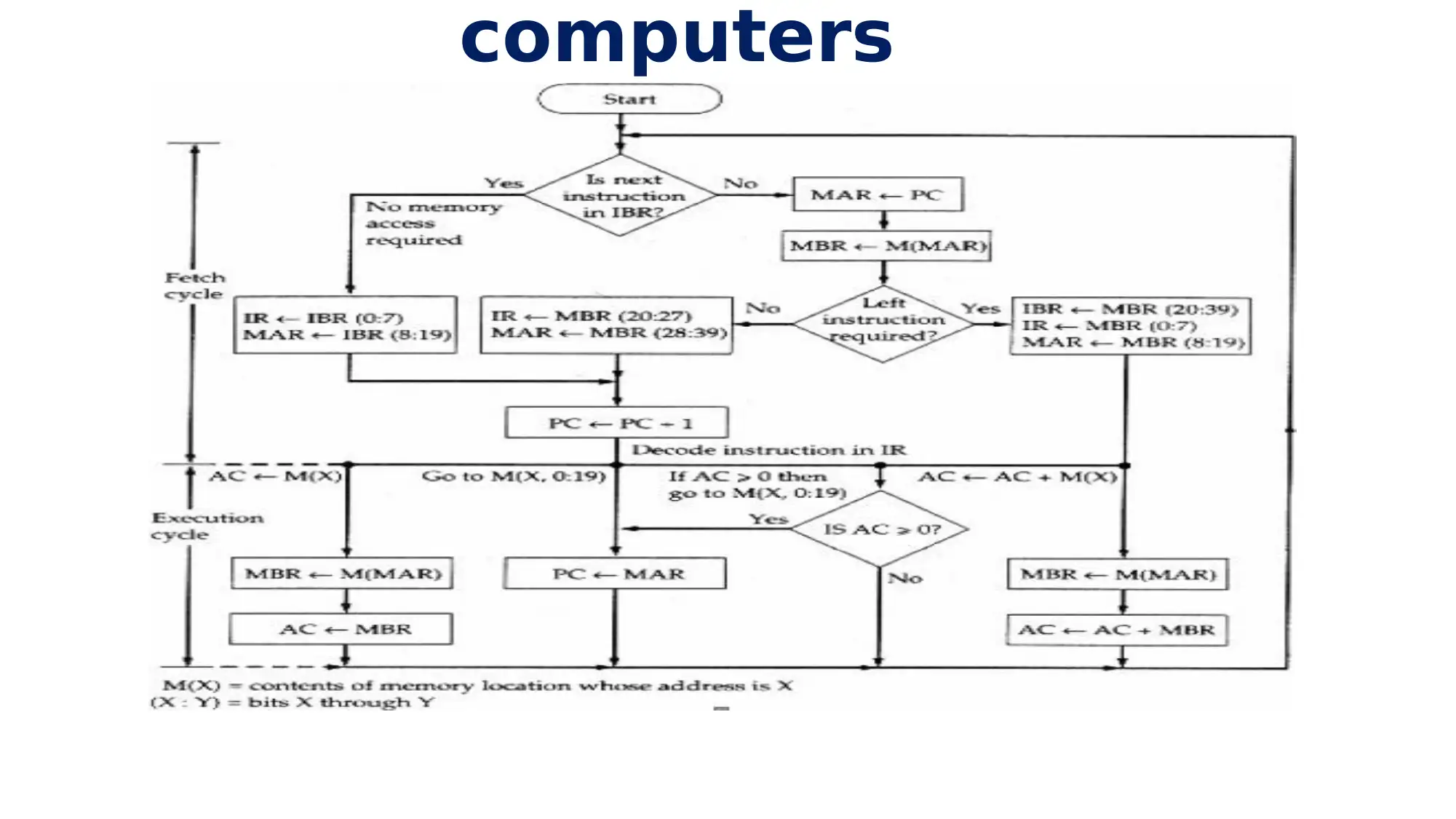

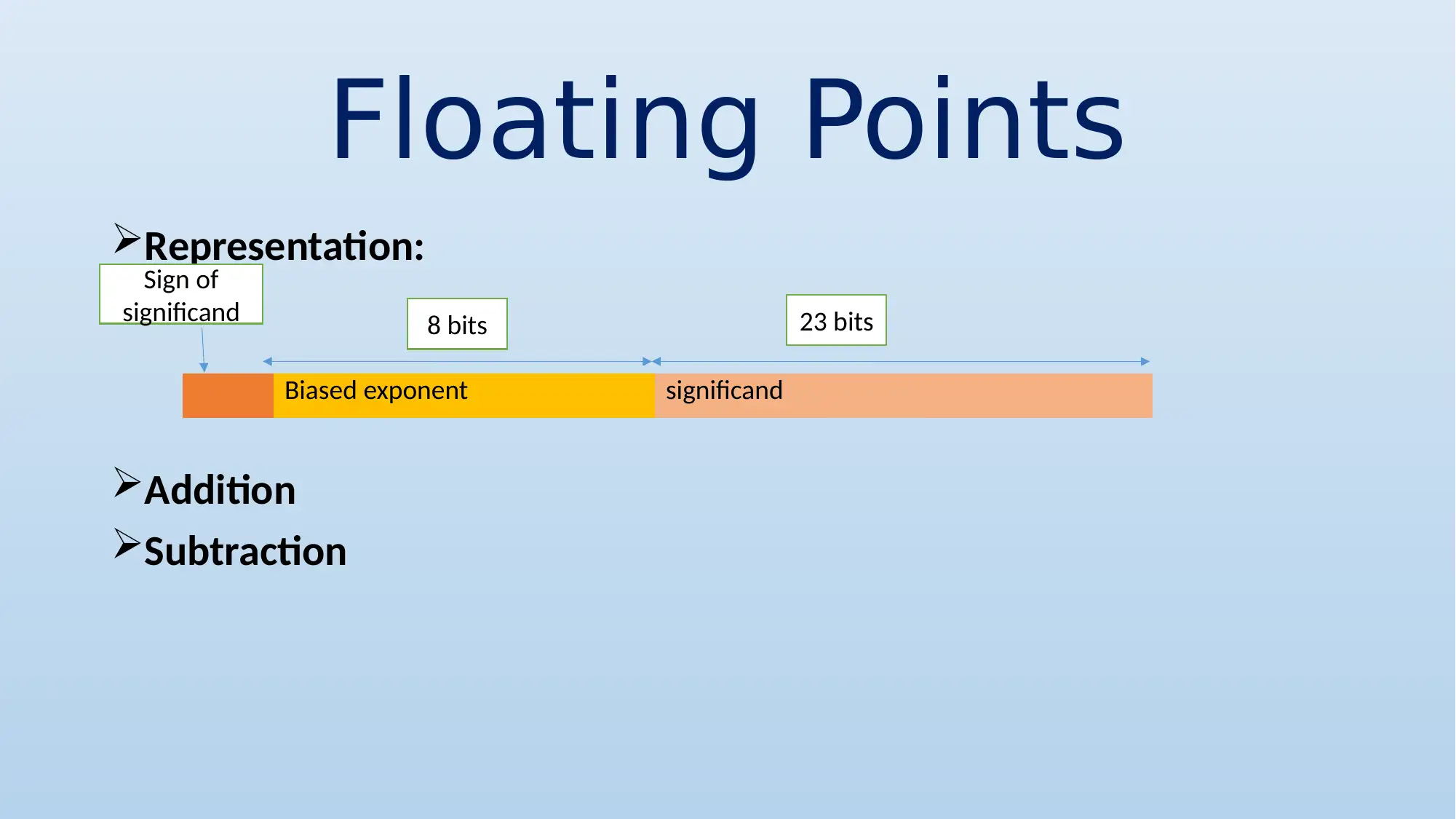

This presentation provides a comprehensive overview of the IAS (Institute for Advanced Study) computer, developed by John Von Neumann. It details the computer's characteristics, including its physical dimensions, word length, and the significance of its design. The presentation delves into the IAS structure, explaining the roles of key components such as the Memory Buffer Register (MBR), Memory Address Register (MAR), Instruction Register (IR), Instruction Buffer Register (IBR), Program Counter (PC), Accumulator (AC), and Multiplier Quotient (MQ). It further elucidates the Central Processing Unit (CPU) and its function in data processing. The presentation also covers the instruction cycles, differentiating between the fetch and execute cycles, and outlines various instruction types, including data transfer, unconditional and conditional branches, arithmetic operations, and address modification. Additionally, it discusses different scales of integration (SSI, MSI, LSI, VLSI, and VVLSI) and touches upon floating-point representation. The presentation concludes by highlighting the key features of the IAS computer and its impact on computer design.

1 out of 15

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)