Hardware Simulation: Implementing Logic Gates (Mux, Demux) and More

VerifiedAdded on 2022/08/12

|29

|2518

|26

Practical Assignment

AI Summary

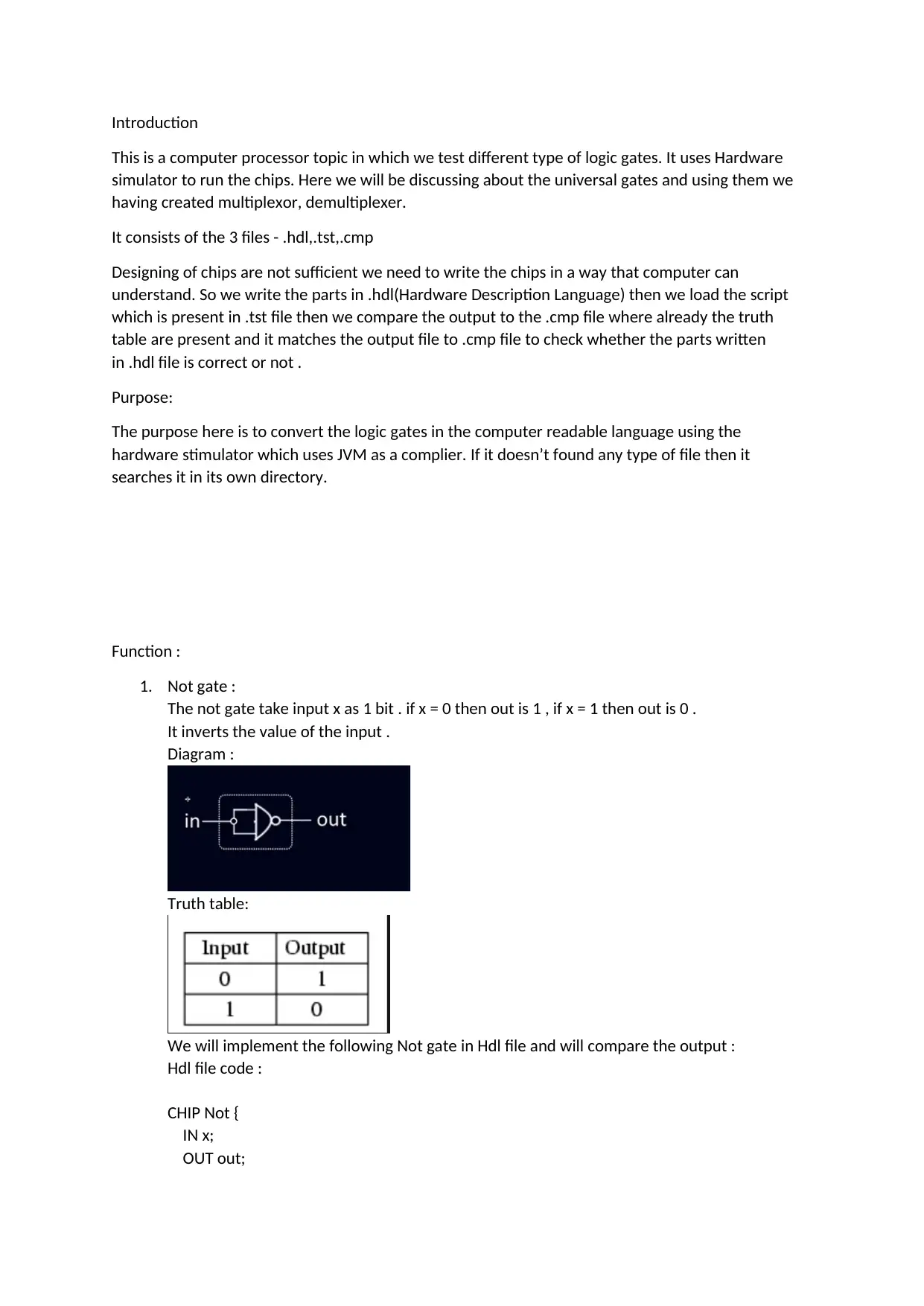

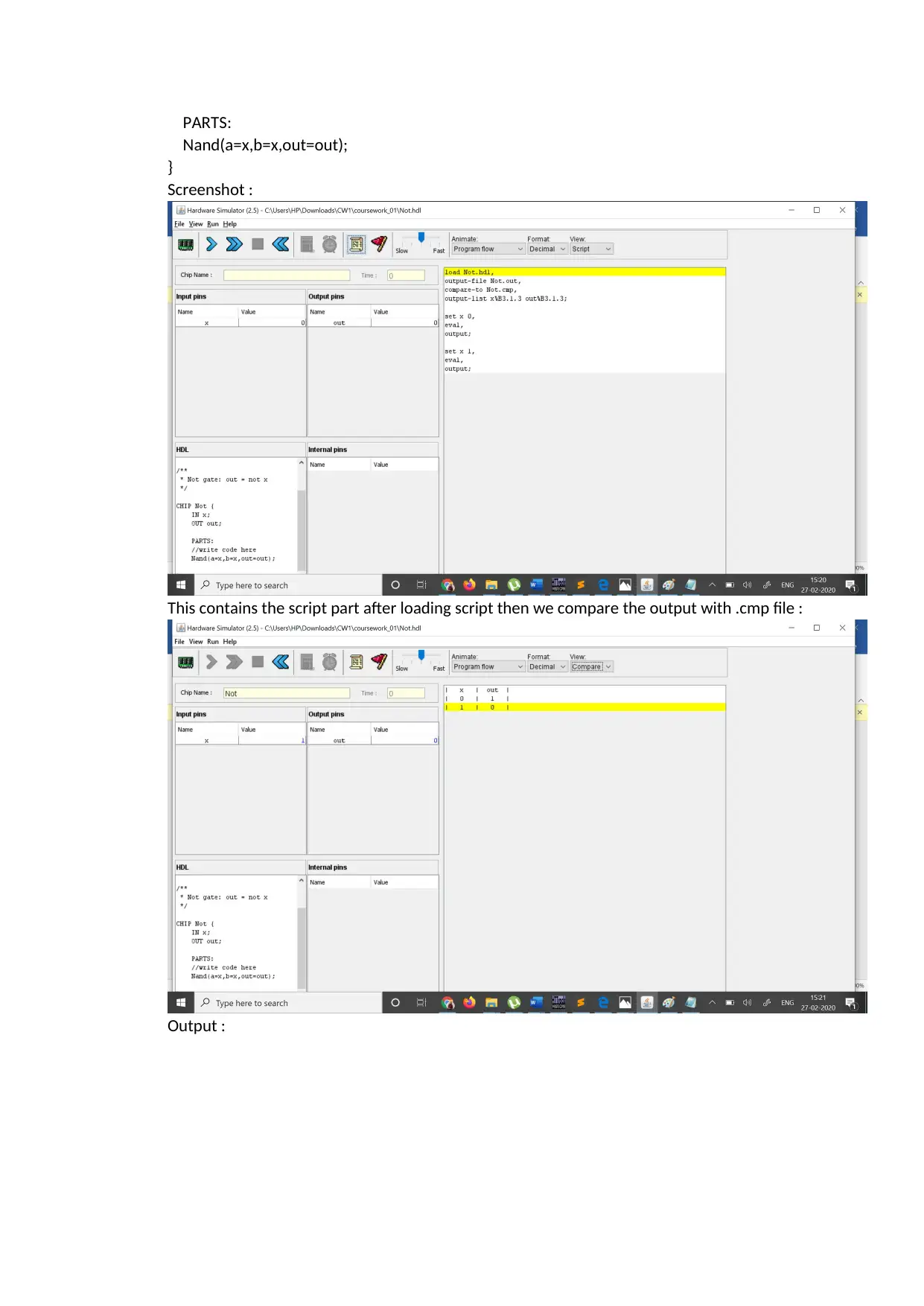

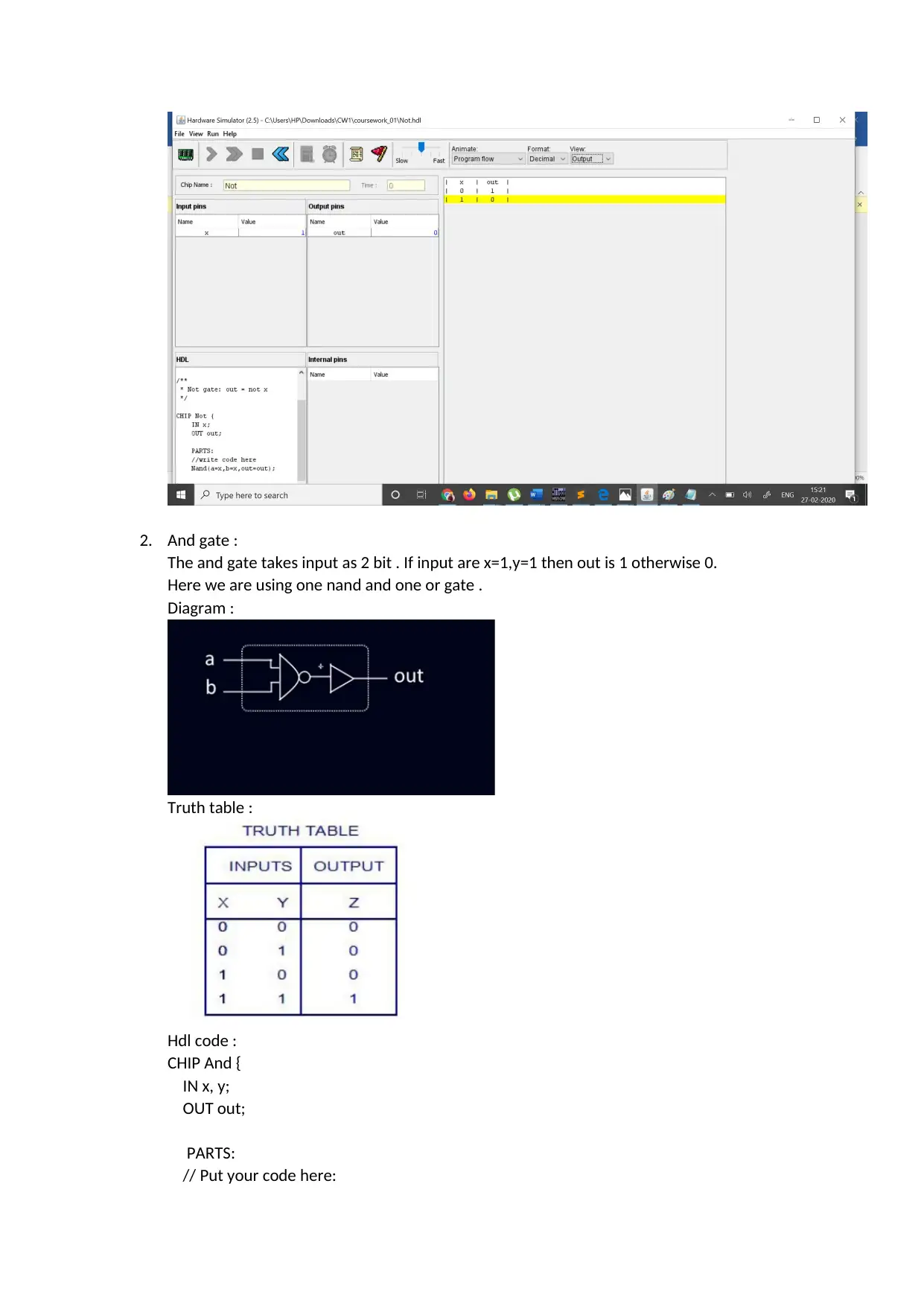

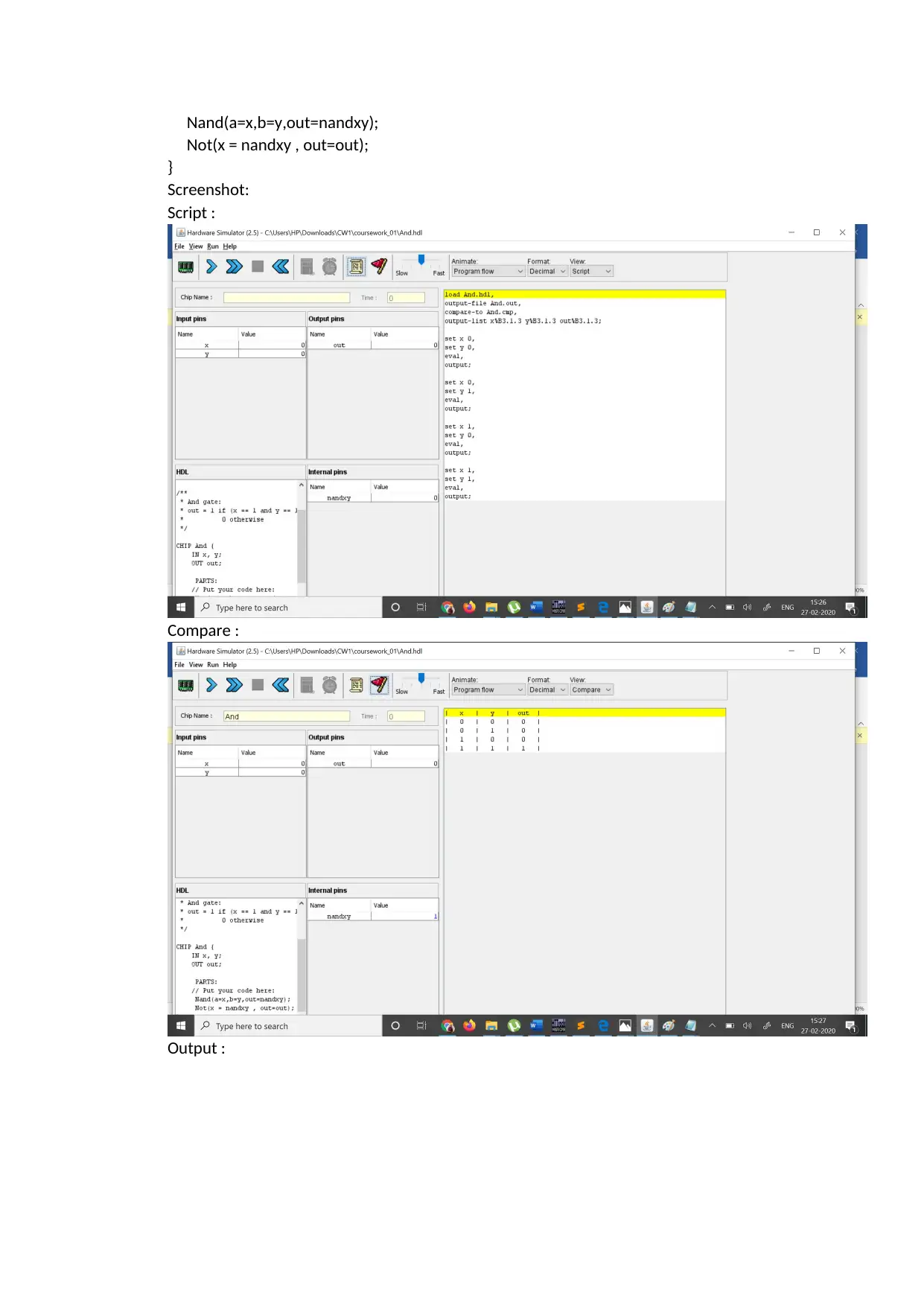

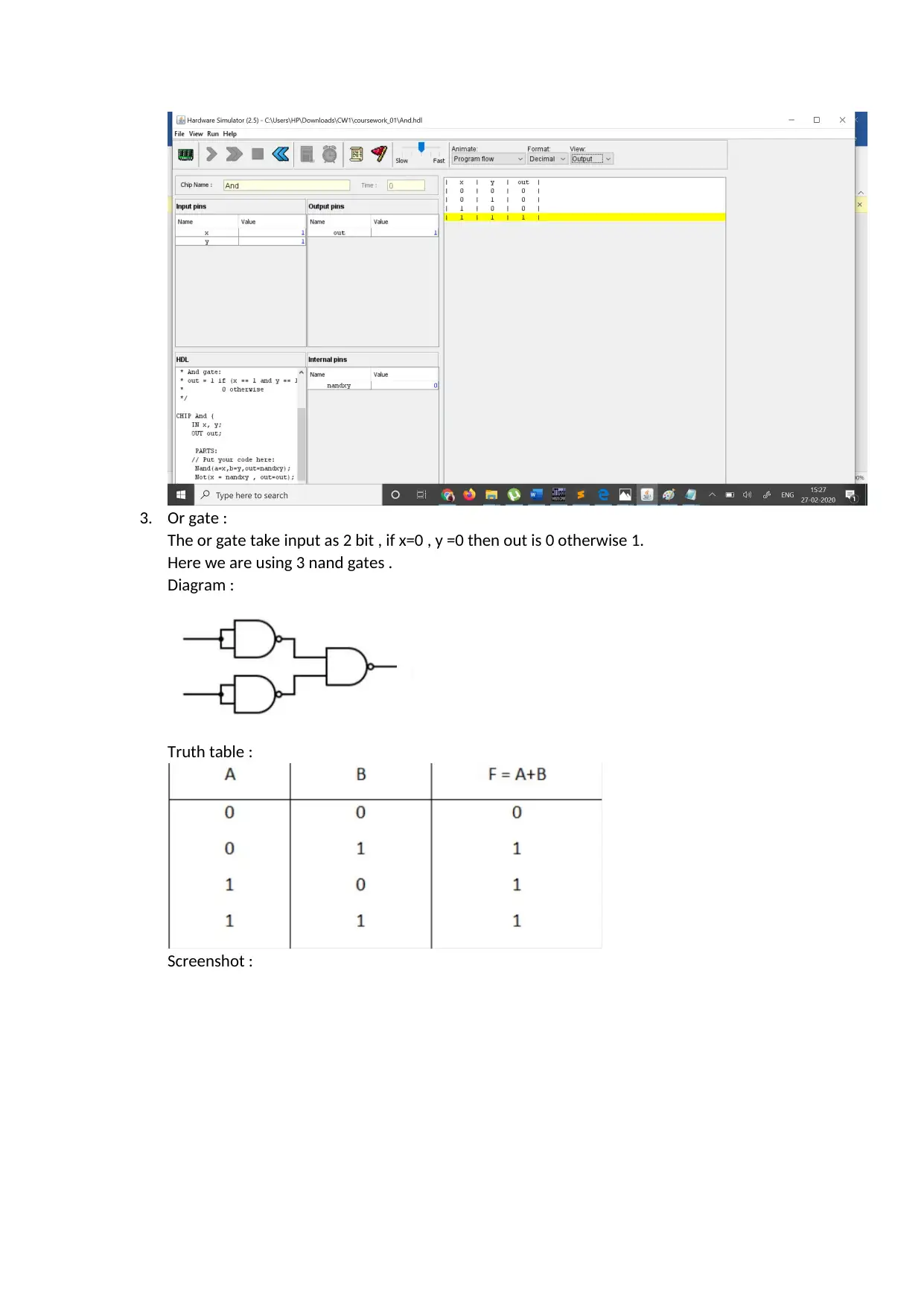

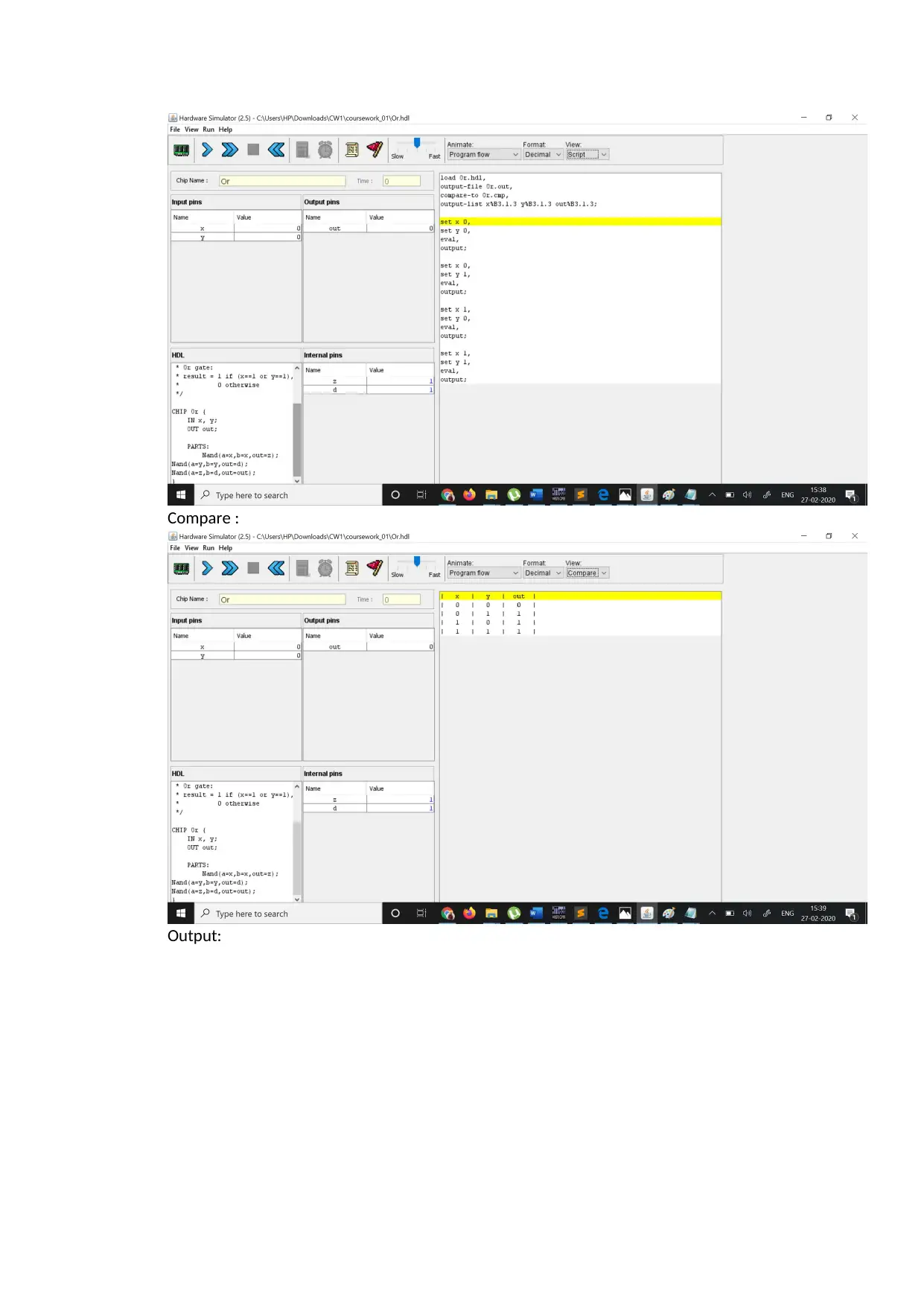

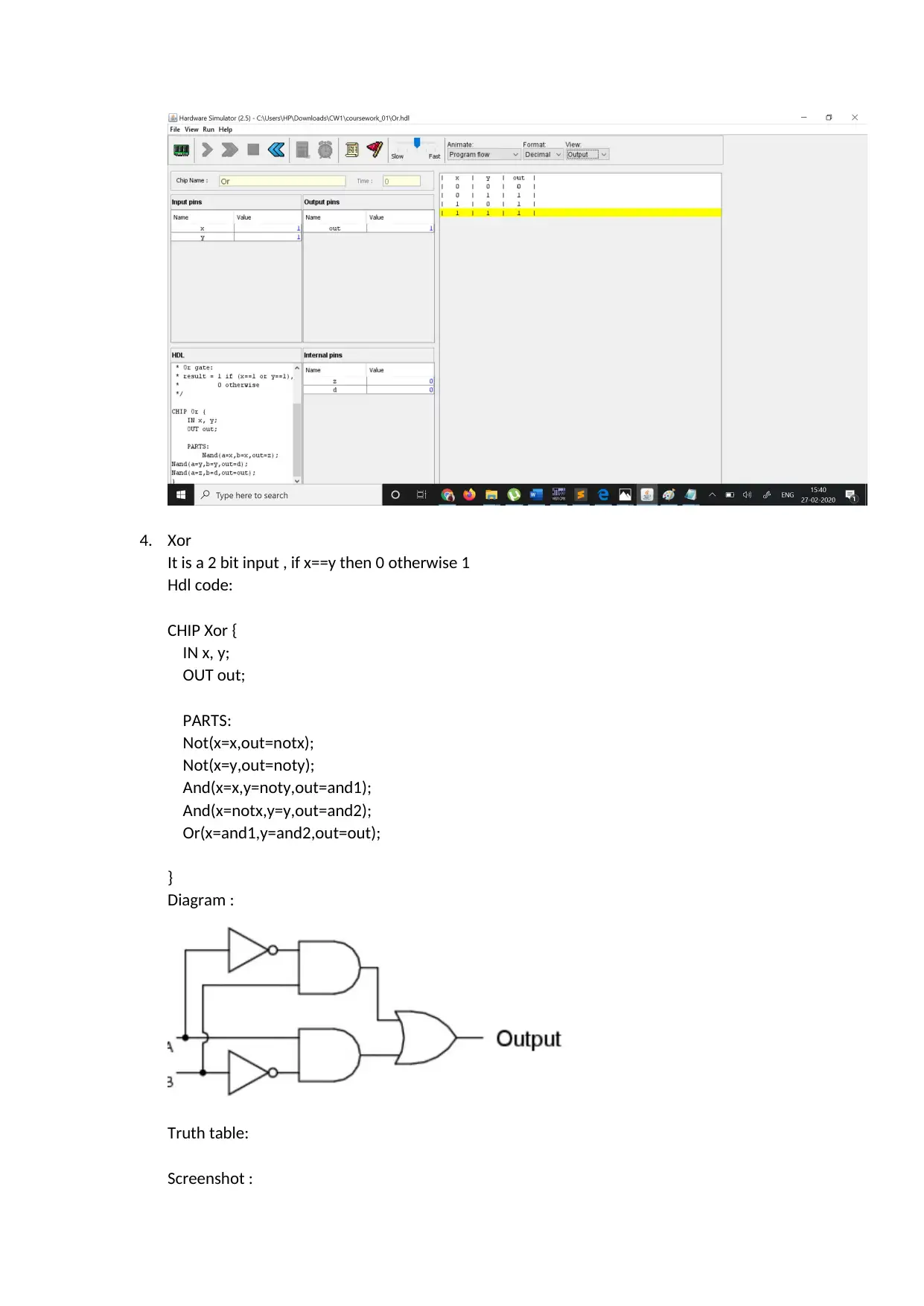

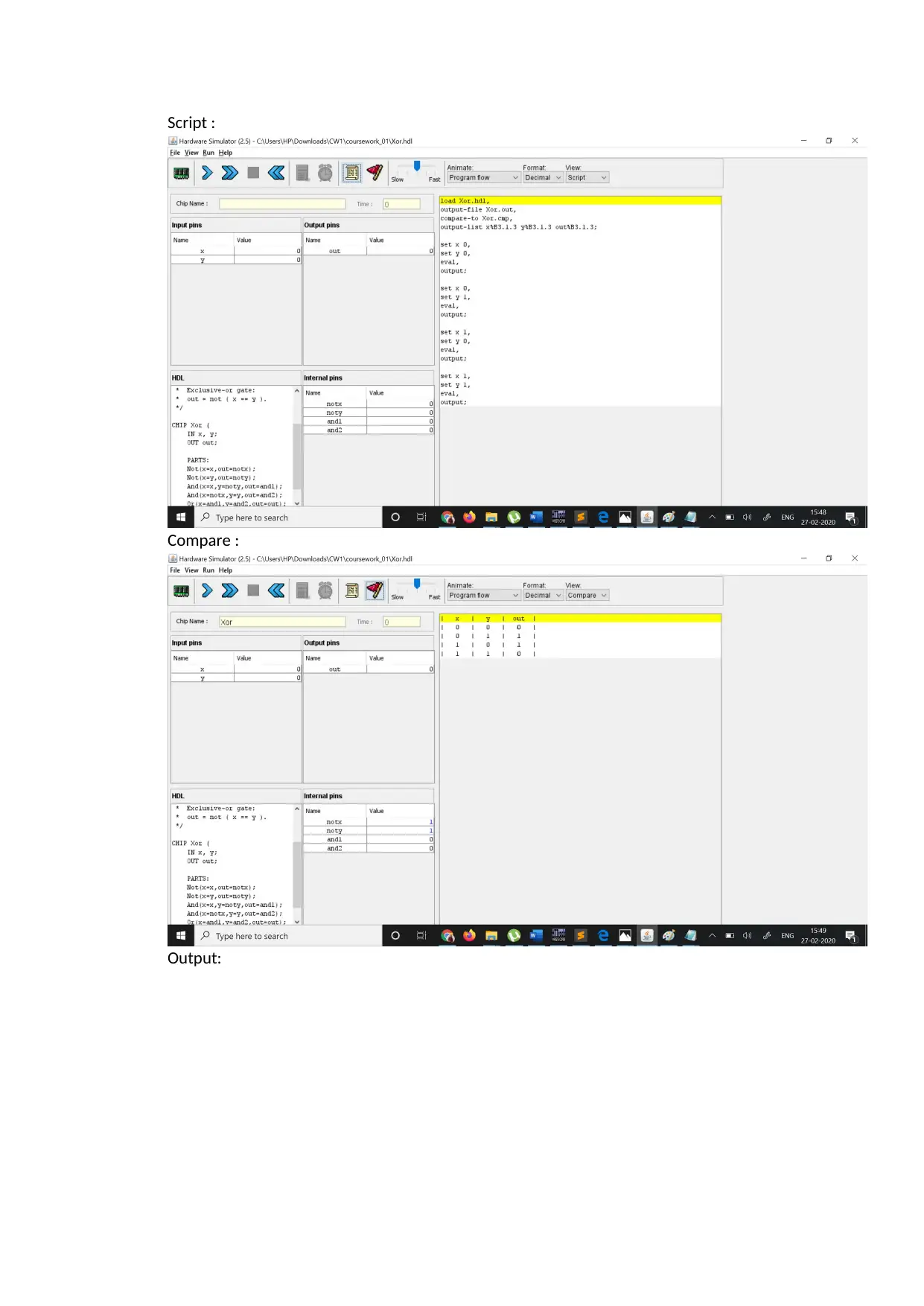

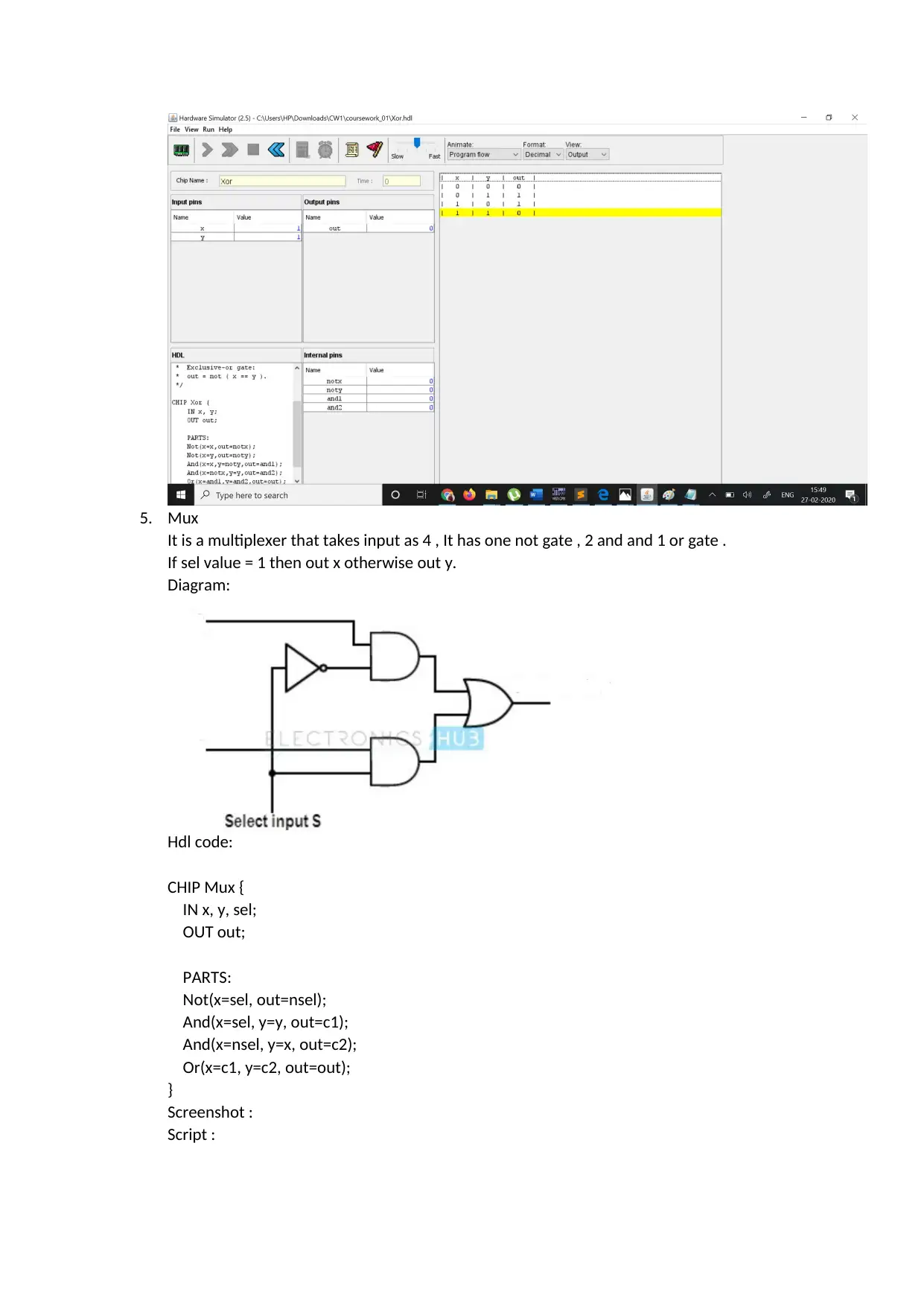

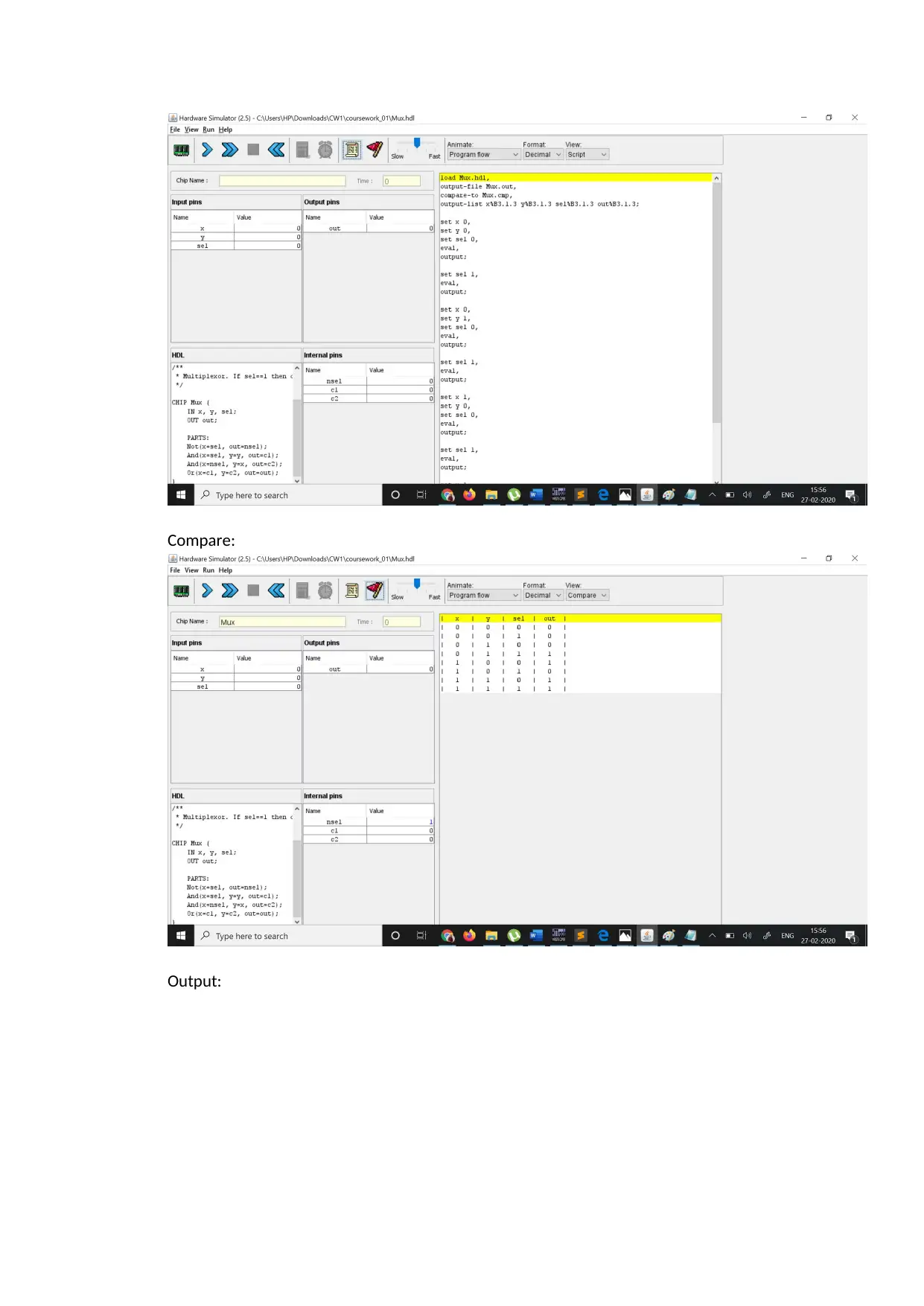

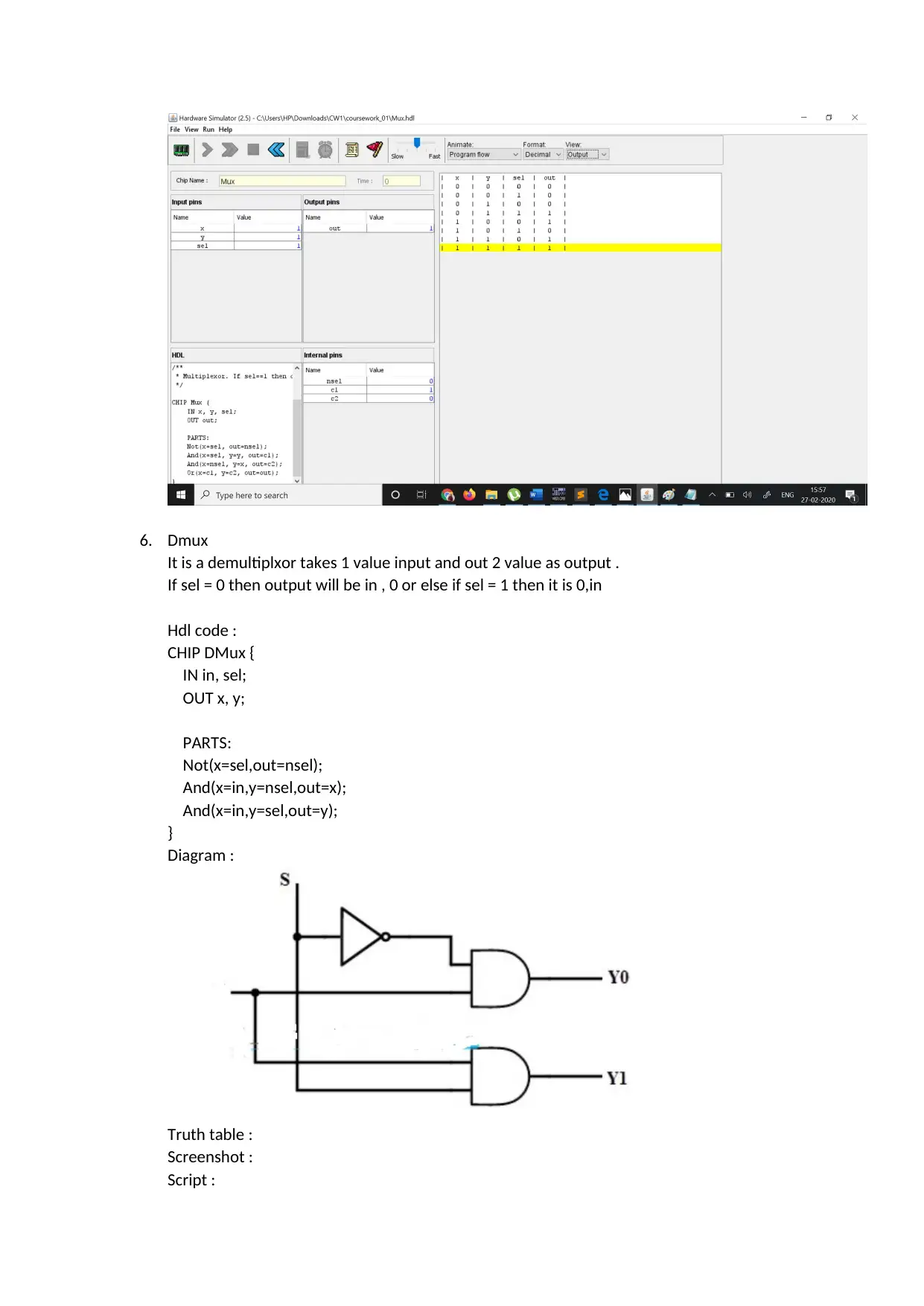

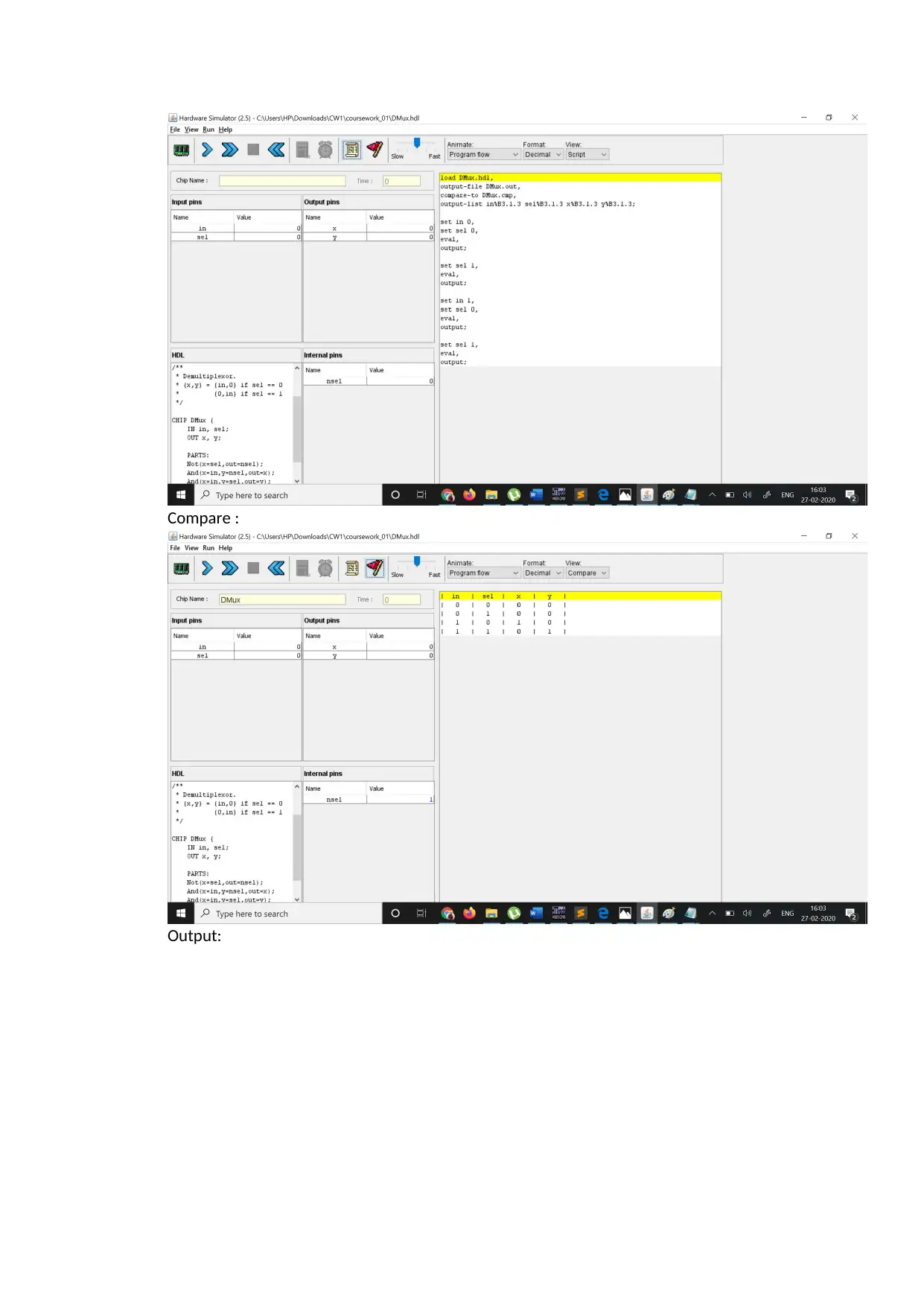

This assignment focuses on implementing various logic gates using a hardware simulator. The project begins with the basic gates like Not, And, Or, and Xor, demonstrating their functionality and truth tables within the .hdl (Hardware Description Language) files. The core of the assignment involves designing and simulating more complex circuits such as multiplexers (Mux) and demultiplexers (Demux), along with their 16-bit and 8-way variations, showing how these components are built using the fundamental gates. The .hdl files define the chip's structure, while .tst files contain scripts to test the chips, and .cmp files provide the expected outputs for comparison. The document illustrates the design process, including screenshots of the code, script execution, and comparison results, ensuring the correctness of each gate's implementation. The project culminates in the design and simulation of more intricate circuits like Or8way, Mux8Way16, DMux4Way, and DMux8Way, providing a comprehensive understanding of digital logic design and hardware simulation principles. The assignment showcases the practical application of logic gates in building complex digital circuits and how hardware simulators are used to verify their functionality.

1 out of 29

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)