1007ICT/7611ICT Assignment: Logic Circuit Design and Analysis

VerifiedAdded on 2022/08/22

|5

|963

|26

Practical Assignment

AI Summary

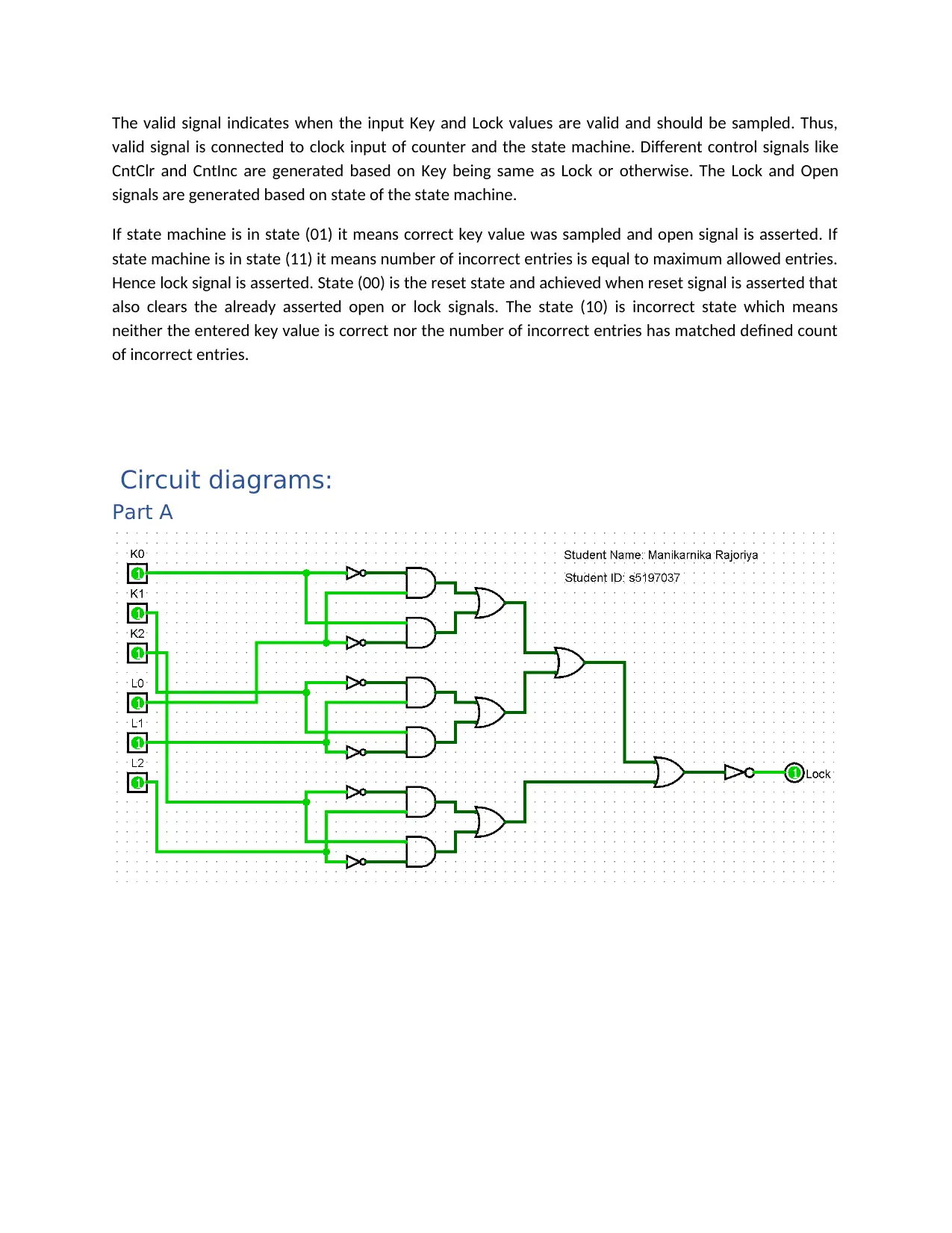

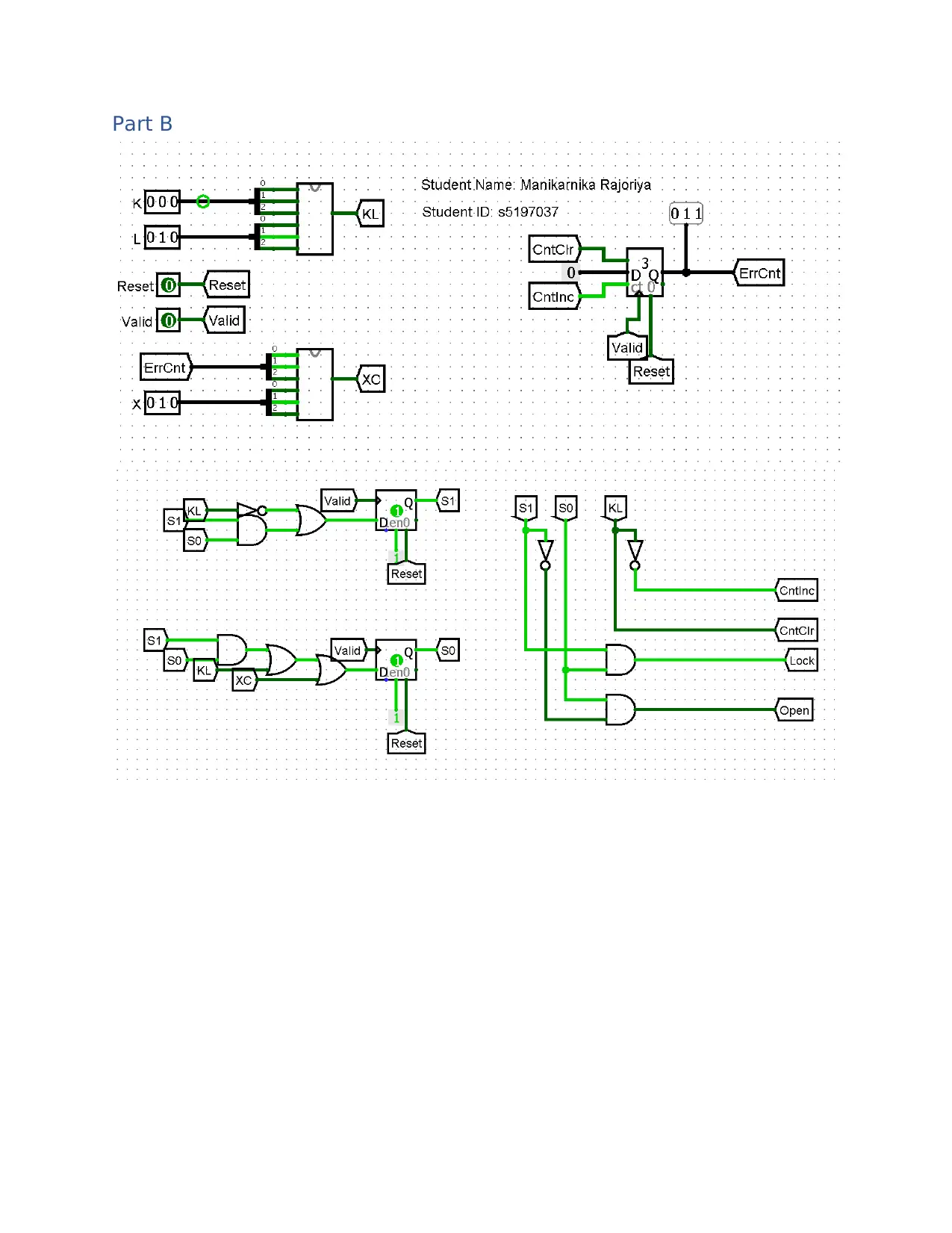

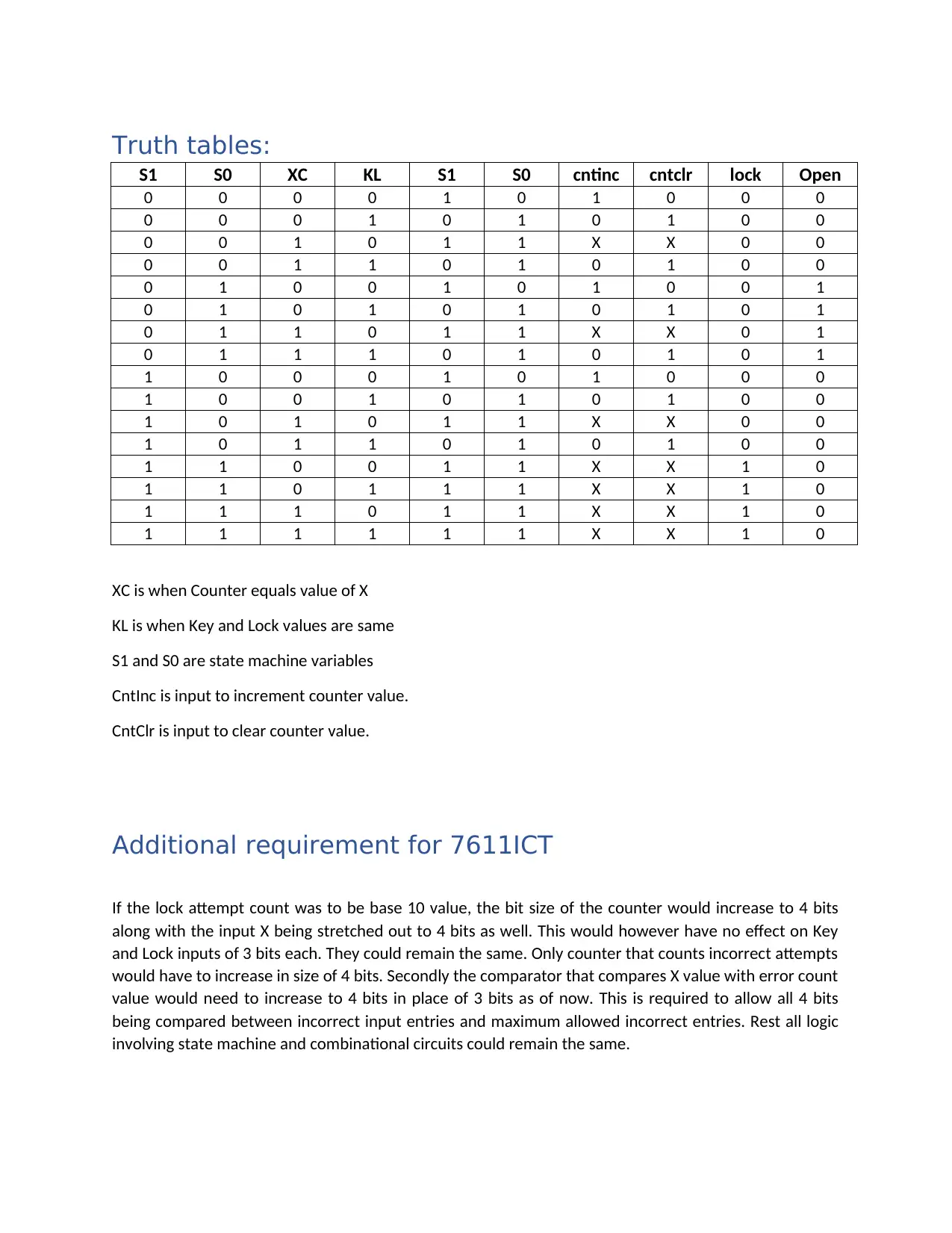

This assignment report details the design of a circuit as a state machine, addressing the requirements of the 1007ICT/7611ICT course. The circuit manages incorrect entry attempts and locks the system after a specified count. The solution includes two parts: Part A, a 3-bit comparator, and Part B, which utilizes the comparator within the state machine. The report presents circuit diagrams, truth tables, and descriptions of the states (Reset, Correct, Incorrect, and Lock). The functionality of the EXOR and NOR gates is explained. The design incorporates D flip-flops to define states and generates control signals such as CntInc, CntClr, Lock, and Open. The report also addresses an additional requirement for the 7611ICT course, discussing the impact of using a base-10 count for lock attempts and the necessary adjustments to the counter and comparator bit sizes. The student has used the Logisim simulator to create the circuits and provided a written report in PDF format.

1 out of 5

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)