MARIE and ISA: Answers to Questions 1-3

VerifiedAdded on 2023/06/12

|9

|811

|325

AI Summary

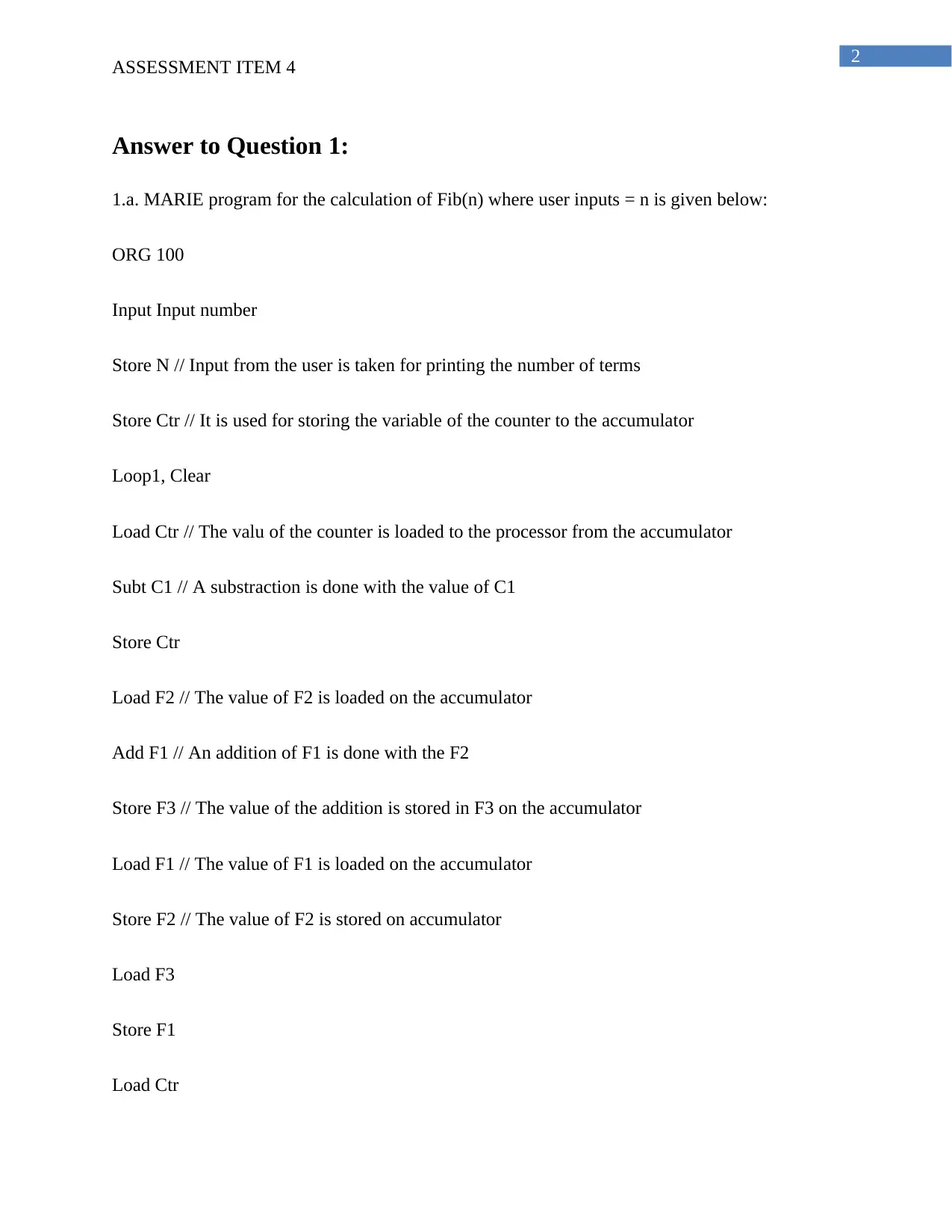

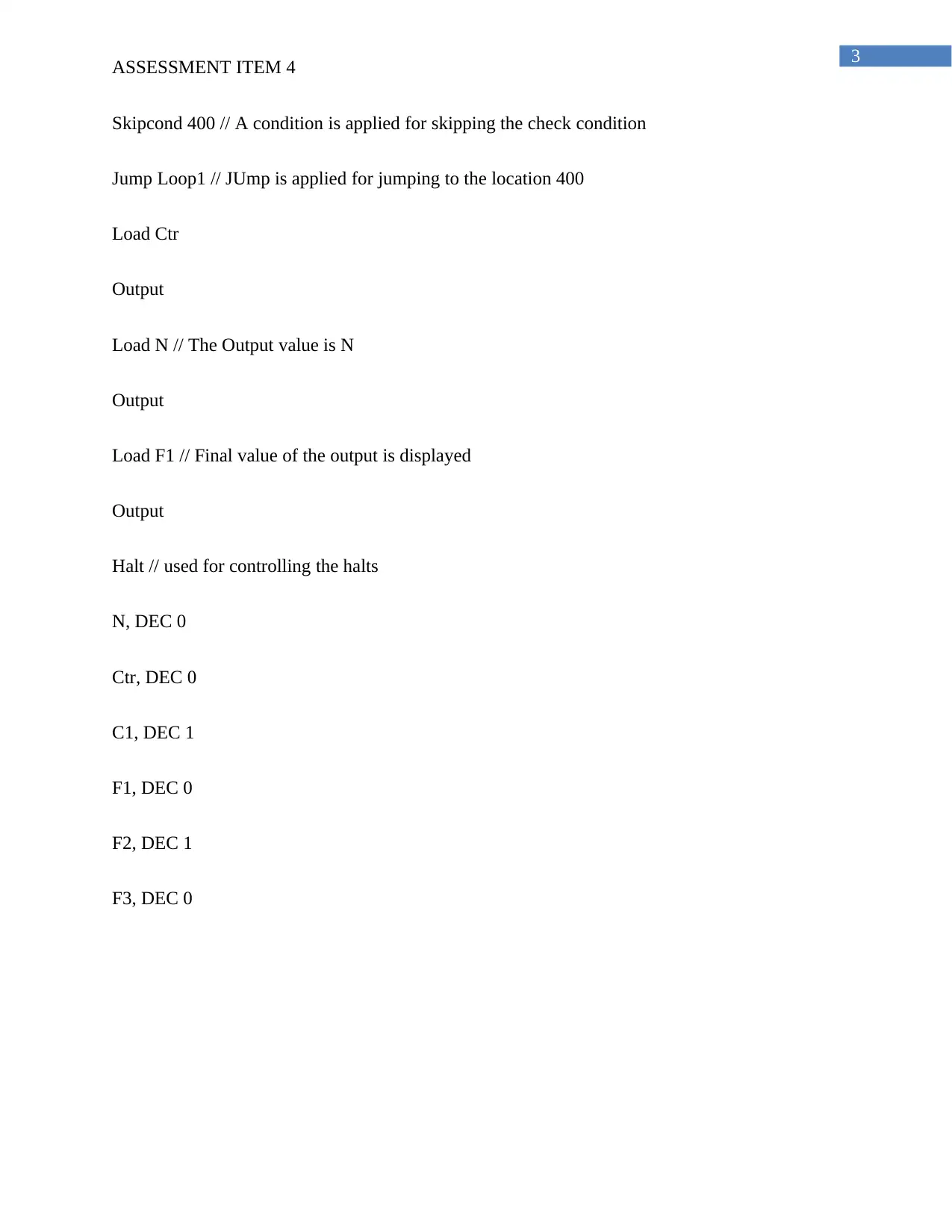

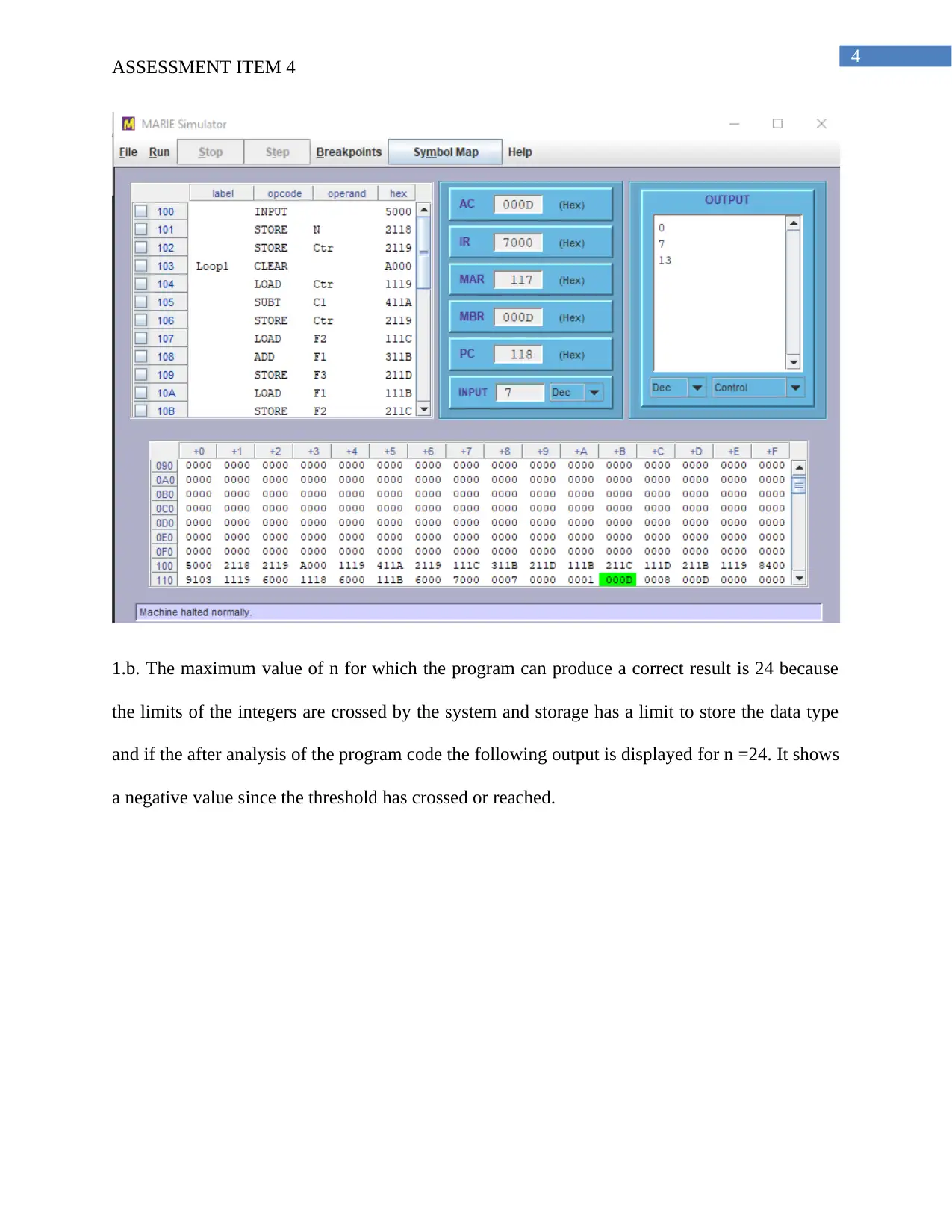

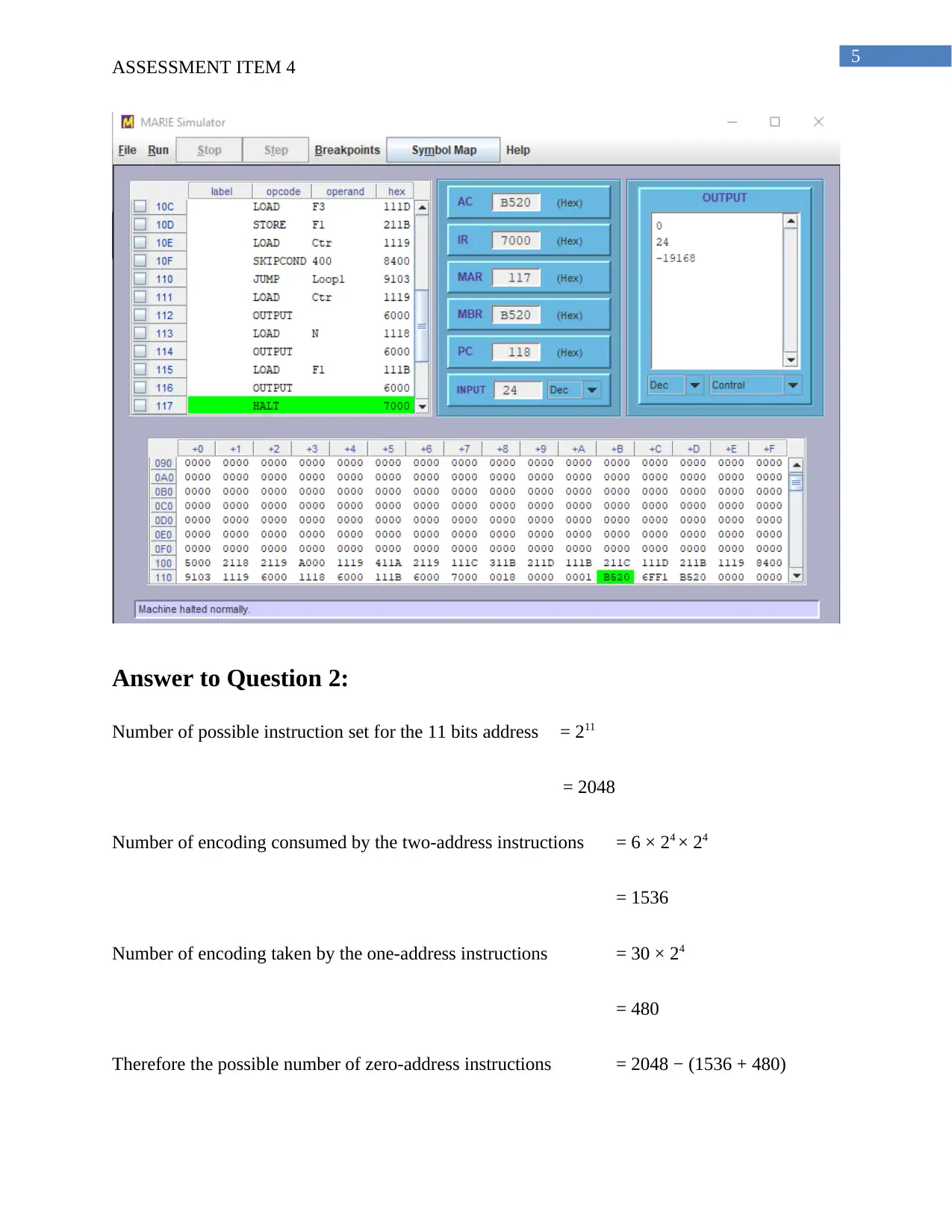

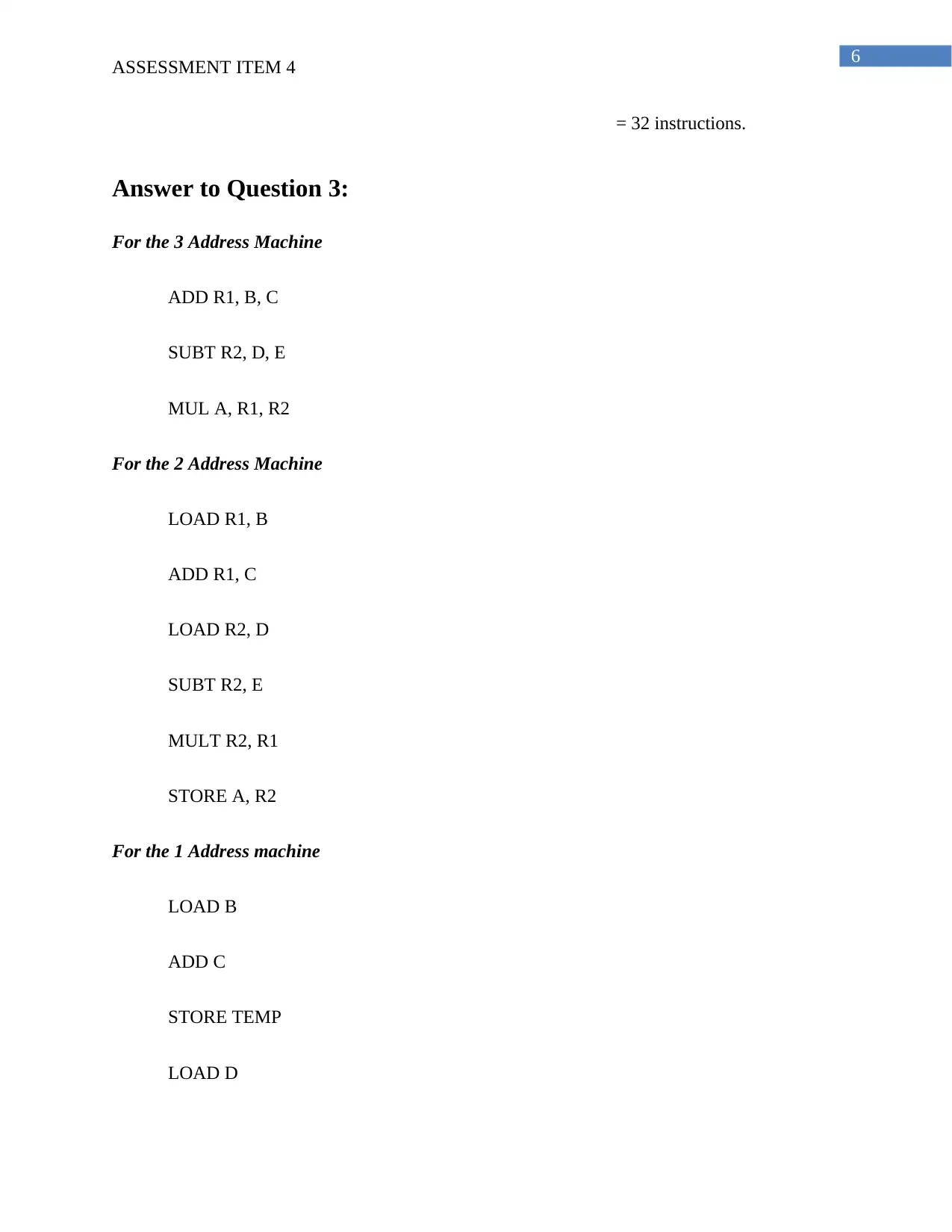

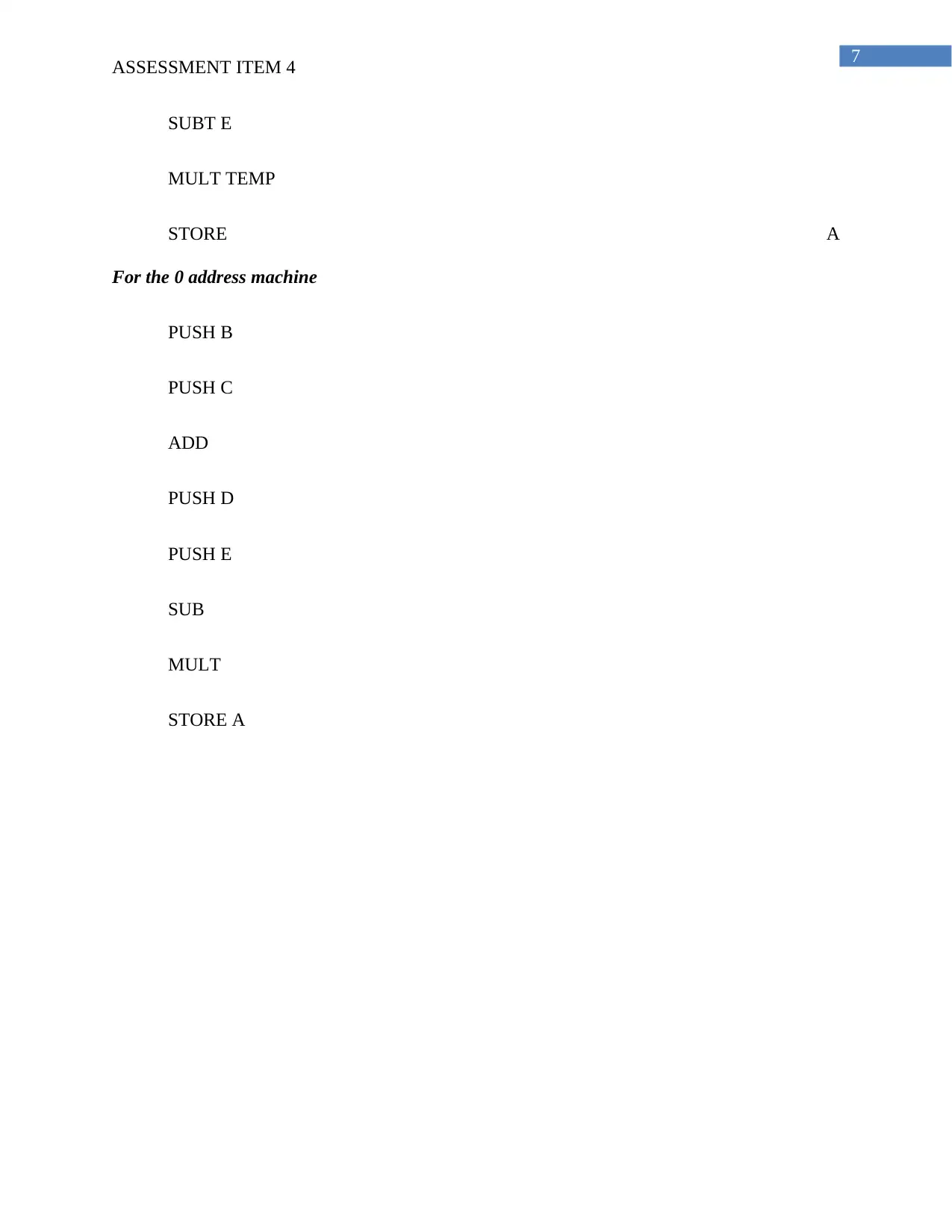

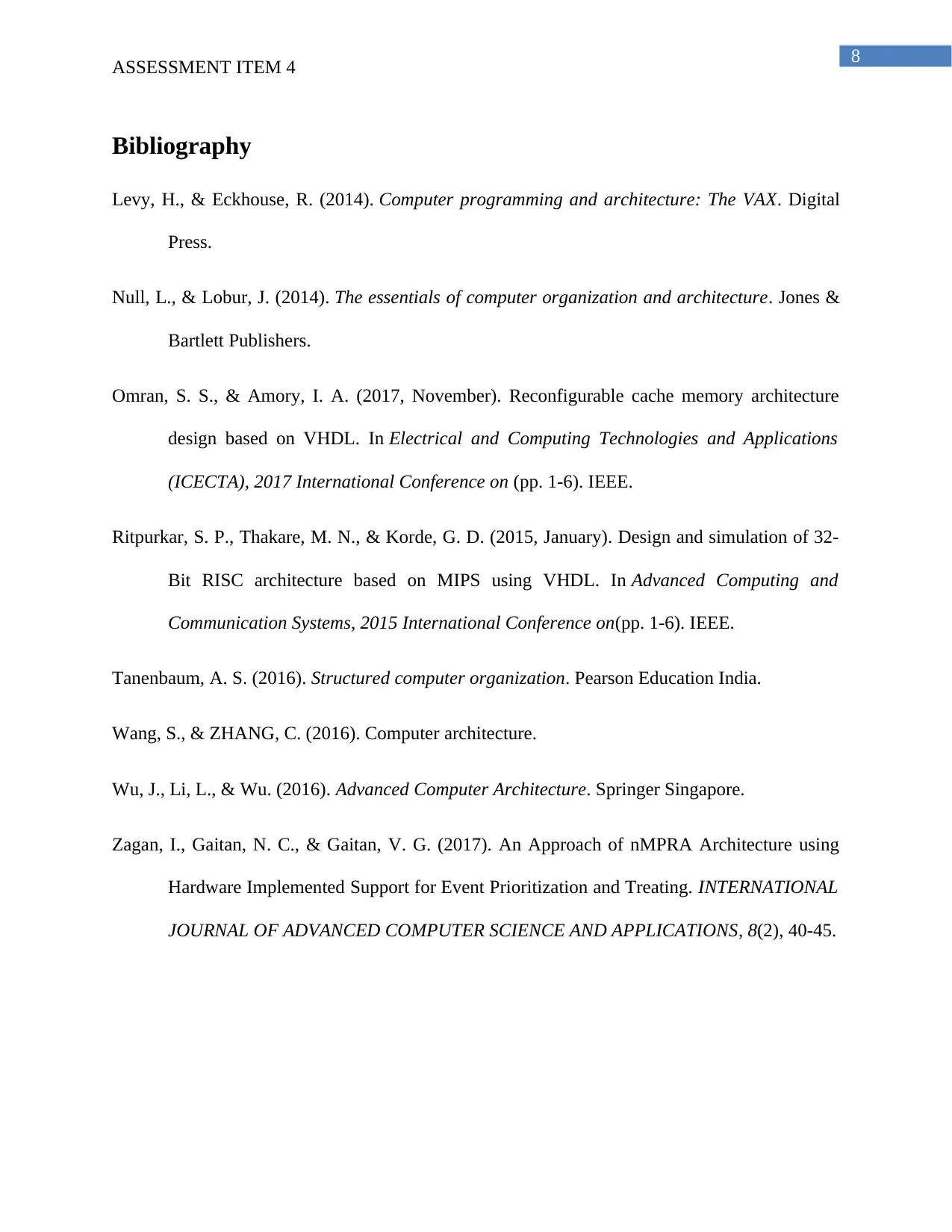

This article provides answers to questions 1-3 related to MARIE and ISA. It includes MARIE program for the calculation of Fib(n), maximum value of n, possible instruction set for the 11 bits address, and more.

Contribute Materials

Your contribution can guide someone’s learning journey. Share your

documents today.

1 out of 9

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)