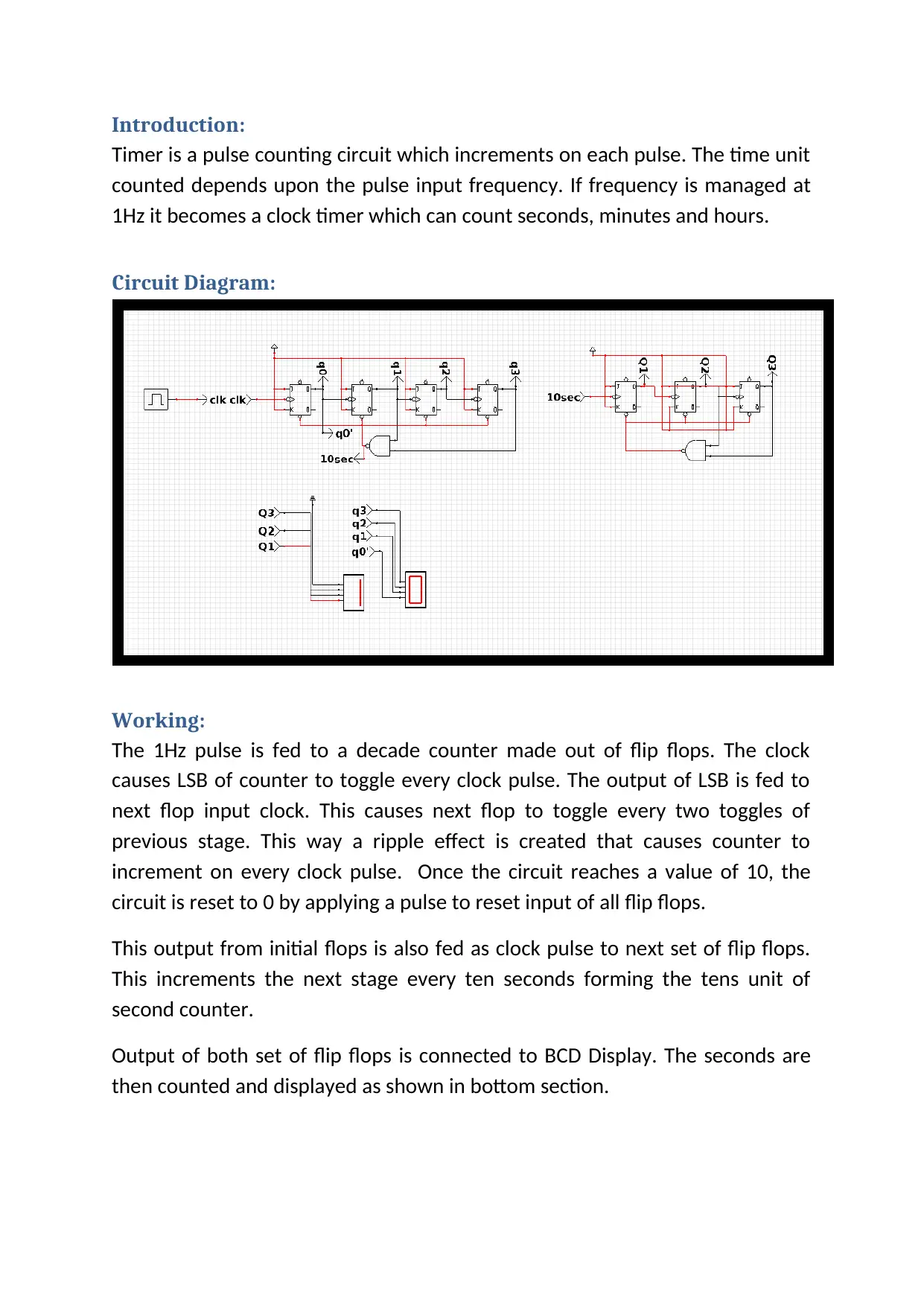

NIT3104 Computer Architecture Part A DESIGNING A DIGITAL TIMER

VerifiedAdded on 2023/04/03

|2

|202

|104

AI Summary

hi ther einside the pdf file you can see that part A is due on 5/27/2019 and part B is due on 06/03/2019 and i hope you guys will follow the given instruction thank you. and the weight of this both part A and B is 25% thanks.

Contribute Materials

Your contribution can guide someone’s learning journey. Share your

documents today.

1 out of 2

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)