Pipelined Processes on Multiple Processors

VerifiedAdded on 2023/06/04

|9

|1396

|373

AI Summary

This article discusses the instruction pipelining process of modern Intel processors and the latest ARM architecture. It includes Gantt charts and task lists for each pipeline process. No specific subject, course code, or college/university mentioned.

Contribute Materials

Your contribution can guide someone’s learning journey. Share your

documents today.

Pipelined processes on Multiple processors

Secure Best Marks with AI Grader

Need help grading? Try our AI Grader for instant feedback on your assignments.

Table of Contents

1. Chart - 1....................................................................................................................................1

2. Chart – 2...................................................................................................................................4

2

1. Chart - 1....................................................................................................................................1

2. Chart – 2...................................................................................................................................4

2

1. Chart - 1

Modern Intel Processor Instruction Pipeline

The instruction Pipelining process is listed below (Cicala, 2013).

Task Name

Modern Intel Preprocessor Instruction

pipelining

Instruction fetch

Instruction Cache

The Program Counter holds the address

of the current instruction

PC predictor the Program Counter (PC) to

the Instruction Cache to read the current

instruction.

Later machines would use more

complicated and accurate algorithms to guess

the next instruction address.

Instruction decode

Once fetched from the instruction cache,

the instruction bits were shifted down the

pipeline

Initial flip-flops from accepting new bits

Decode stage ended up with quite a lot of

hardware

Execute

Actual computation occurs

Performing Boolean operations

Three latency classes

Register-Register Operation

3

Modern Intel Processor Instruction Pipeline

The instruction Pipelining process is listed below (Cicala, 2013).

Task Name

Modern Intel Preprocessor Instruction

pipelining

Instruction fetch

Instruction Cache

The Program Counter holds the address

of the current instruction

PC predictor the Program Counter (PC) to

the Instruction Cache to read the current

instruction.

Later machines would use more

complicated and accurate algorithms to guess

the next instruction address.

Instruction decode

Once fetched from the instruction cache,

the instruction bits were shifted down the

pipeline

Initial flip-flops from accepting new bits

Decode stage ended up with quite a lot of

hardware

Execute

Actual computation occurs

Performing Boolean operations

Three latency classes

Register-Register Operation

3

Memory Reference

Multi-cycle Instructions

Memory access

Single cycle latency instructions

Ensures that both one and two cycle

instructions

Write back

Both single cycle and two cycle

instructions

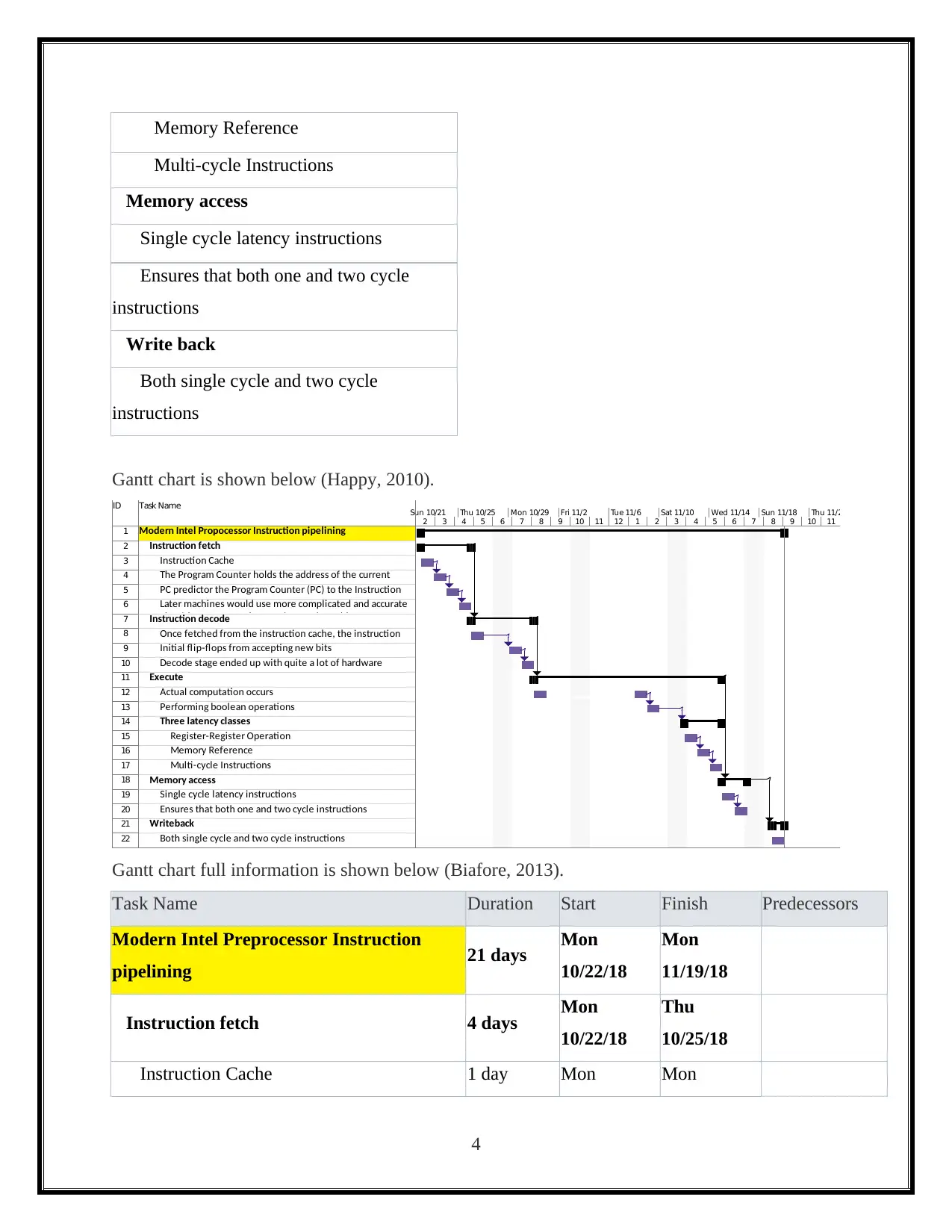

Gantt chart is shown below (Happy, 2010).

ID Task Name

1 Modern Intel Propocessor Instruction pipelining

2 Instruction fetch

3 Instruction Cache

4 The Program Counter holds the address of the current

instruction5 PC predictor the Program Counter (PC) to the Instruction

Cache to read the current instruction.6 Later machines would use more complicated and accurate

algorithms to guess the next instruction address.7 Instruction decode

8 Once fetched from the instruction cache, the instruction

bits were shifted down the pipeline9 Initial flip-flops from accepting new bits

10 Decode stage ended up with quite a lot of hardware

11 Execute

12 Actual computation occurs

13 Performing boolean operations

14 Three latency classes

15 Register-Register Operation

16 Memory Reference

17 Multi-cycle Instructions

18 Memory access

19 Single cycle latency instructions

20 Ensures that both one and two cycle instructions

21 Writeback

22 Both single cycle and two cycle instructions

2 3 4 5 6 7 8 9 10 11 12 1 2 3 4 5 6 7 8 9 10 11

Sun 10/21 Thu 10/25 Mon 10/29 Fri 11/2 Tue 11/6 Sat 11/10 Wed 11/14 Sun 11/18 Thu 11/22

Gantt chart full information is shown below (Biafore, 2013).

Task Name Duration Start Finish Predecessors

Modern Intel Preprocessor Instruction

pipelining 21 days Mon

10/22/18

Mon

11/19/18

Instruction fetch 4 days Mon

10/22/18

Thu

10/25/18

Instruction Cache 1 day Mon Mon

4

Multi-cycle Instructions

Memory access

Single cycle latency instructions

Ensures that both one and two cycle

instructions

Write back

Both single cycle and two cycle

instructions

Gantt chart is shown below (Happy, 2010).

ID Task Name

1 Modern Intel Propocessor Instruction pipelining

2 Instruction fetch

3 Instruction Cache

4 The Program Counter holds the address of the current

instruction5 PC predictor the Program Counter (PC) to the Instruction

Cache to read the current instruction.6 Later machines would use more complicated and accurate

algorithms to guess the next instruction address.7 Instruction decode

8 Once fetched from the instruction cache, the instruction

bits were shifted down the pipeline9 Initial flip-flops from accepting new bits

10 Decode stage ended up with quite a lot of hardware

11 Execute

12 Actual computation occurs

13 Performing boolean operations

14 Three latency classes

15 Register-Register Operation

16 Memory Reference

17 Multi-cycle Instructions

18 Memory access

19 Single cycle latency instructions

20 Ensures that both one and two cycle instructions

21 Writeback

22 Both single cycle and two cycle instructions

2 3 4 5 6 7 8 9 10 11 12 1 2 3 4 5 6 7 8 9 10 11

Sun 10/21 Thu 10/25 Mon 10/29 Fri 11/2 Tue 11/6 Sat 11/10 Wed 11/14 Sun 11/18 Thu 11/22

Gantt chart full information is shown below (Biafore, 2013).

Task Name Duration Start Finish Predecessors

Modern Intel Preprocessor Instruction

pipelining 21 days Mon

10/22/18

Mon

11/19/18

Instruction fetch 4 days Mon

10/22/18

Thu

10/25/18

Instruction Cache 1 day Mon Mon

4

Paraphrase This Document

Need a fresh take? Get an instant paraphrase of this document with our AI Paraphraser

10/22/18 10/22/18

The Program Counter holds the address of

the current instruction 1 day Tue

10/23/18

Tue

10/23/18 3

PC predictor the Program Counter (PC) to

the Instruction Cache to read the current

instruction.

1 day Wed

10/24/18

Wed

10/24/18 4

Later machines would use more

complicated and accurate algorithms to guess

the next instruction address.

1 day Thu

10/25/18

Thu

10/25/18 5

Instruction decode 3 days Fri 10/26/18 Tue

10/30/18 2

Once fetched from the instruction cache,

the instruction bits were shifted down the

pipeline

1 day Fri 10/26/18 Fri 10/26/18

Initial flip-flops from accepting new bits 1 day Mon

10/29/18

Mon

10/29/18 8

Decode stage ended up with quite a lot of

hardware 1 day Tue

10/30/18

Tue

10/30/18 9

Execute 11 days Wed

10/31/18

Wed

11/14/18 7

Actual computation occurs 2 days Wed

10/31/18 Thu 11/8/18

Performing Boolean operations 1 day Fri 11/9/18 Fri 11/9/18 12

Three latency classes 3 days Mon

11/12/18

Wed

11/14/18 13

Register-Register Operation 1 day Mon

11/12/18

Mon

11/12/18

Memory Reference 1 day Tue

11/13/18

Tue

11/13/18 15

Multi-cycle Instructions 1 day Wed Wed 16

5

The Program Counter holds the address of

the current instruction 1 day Tue

10/23/18

Tue

10/23/18 3

PC predictor the Program Counter (PC) to

the Instruction Cache to read the current

instruction.

1 day Wed

10/24/18

Wed

10/24/18 4

Later machines would use more

complicated and accurate algorithms to guess

the next instruction address.

1 day Thu

10/25/18

Thu

10/25/18 5

Instruction decode 3 days Fri 10/26/18 Tue

10/30/18 2

Once fetched from the instruction cache,

the instruction bits were shifted down the

pipeline

1 day Fri 10/26/18 Fri 10/26/18

Initial flip-flops from accepting new bits 1 day Mon

10/29/18

Mon

10/29/18 8

Decode stage ended up with quite a lot of

hardware 1 day Tue

10/30/18

Tue

10/30/18 9

Execute 11 days Wed

10/31/18

Wed

11/14/18 7

Actual computation occurs 2 days Wed

10/31/18 Thu 11/8/18

Performing Boolean operations 1 day Fri 11/9/18 Fri 11/9/18 12

Three latency classes 3 days Mon

11/12/18

Wed

11/14/18 13

Register-Register Operation 1 day Mon

11/12/18

Mon

11/12/18

Memory Reference 1 day Tue

11/13/18

Tue

11/13/18 15

Multi-cycle Instructions 1 day Wed Wed 16

5

11/14/18 11/14/18

Memory access 2 days Thu

11/15/18 Fri 11/16/18 11

Single cycle latency instructions 1 day Thu

11/15/18

Thu

11/15/18

Ensures that both one and two cycle

instructions 1 day Fri 11/16/18 Fri 11/16/18 19

Write back 1 day Mon

11/19/18

Mon

11/19/18 18

Both single cycle and two cycle

instructions 1 day Mon

11/19/18

Mon

11/19/18

2. Chart – 2

Latest ARM Architecture compared to Modern Intel processor Gantt chart is shown below.

Latest ARM Architecture Pipeline process is listed below.

Task Name

Latest ARM Architecture

Two Fetch stages

First stage of instruction fetches and branch prediction.

Second stage of instruction fetches and branch

prediction.

Decode stage

Instruction decodes.

Issue stage

Register read and instruction issue.

MP11 CPU integer execution pipeline.

Four stages of the MP11 CPU integer execution

pipeline.

Shifter stage.

6

Memory access 2 days Thu

11/15/18 Fri 11/16/18 11

Single cycle latency instructions 1 day Thu

11/15/18

Thu

11/15/18

Ensures that both one and two cycle

instructions 1 day Fri 11/16/18 Fri 11/16/18 19

Write back 1 day Mon

11/19/18

Mon

11/19/18 18

Both single cycle and two cycle

instructions 1 day Mon

11/19/18

Mon

11/19/18

2. Chart – 2

Latest ARM Architecture compared to Modern Intel processor Gantt chart is shown below.

Latest ARM Architecture Pipeline process is listed below.

Task Name

Latest ARM Architecture

Two Fetch stages

First stage of instruction fetches and branch prediction.

Second stage of instruction fetches and branch

prediction.

Decode stage

Instruction decodes.

Issue stage

Register read and instruction issue.

MP11 CPU integer execution pipeline.

Four stages of the MP11 CPU integer execution

pipeline.

Shifter stage.

6

First stage of the multiply-accumulate pipeline.

Address generation stage.

Main integer operation calculation.

First stage of data cache access.

Second stage of the multiply-accumulate pipeline.

Pipeline stage to enable saturation of integer

results.

Third stage of the multiply-accumulate pipeline.

Second stage of data cache access.

Write back of data from the multiply or main

execution pipelines.

Write back of data from the Load Store Unit.

Gantt chart is shown below.

ID Task Name

1 Latest ARM Architecture

2 Two Fetch stages

3 First stage of instruction fetch and branch prediction.

4 Second stage of instruction fetch and branch prediction.

5 Decode stage

6 Instruction decode.

7 Issue stage

8 Register read and instruction issue.

9 MP11 CPU integer execution pipeline.

10 Four stages of the MP11 CPU integer execution pipeline.

11 Shifter stage.

12 First stage of the multiply-accumulate pipeline.

13 Address generation stage.

14 Main integer operation calculation.

15 First stage of data cache access.

16 Second stage of the multiply-accumulate pipeline.

17 Pipeline stage to enable saturation of integer results.

18 Third stage of the multiply-accumulate pipeline.

19 Second stage of data cache access.

20 Write back of data from the multiply or main

execution pipelines.21 Write back of data from the Load Store Unit.

S M T W T F S S M T W T F S S M T W T F S S M T W T

Oct 21, '18 Oct 28, '18 Nov 4, '18 Nov 11, '18

Gantt Chart Full is shown below ("ARM Information Center", 2018).

7

Address generation stage.

Main integer operation calculation.

First stage of data cache access.

Second stage of the multiply-accumulate pipeline.

Pipeline stage to enable saturation of integer

results.

Third stage of the multiply-accumulate pipeline.

Second stage of data cache access.

Write back of data from the multiply or main

execution pipelines.

Write back of data from the Load Store Unit.

Gantt chart is shown below.

ID Task Name

1 Latest ARM Architecture

2 Two Fetch stages

3 First stage of instruction fetch and branch prediction.

4 Second stage of instruction fetch and branch prediction.

5 Decode stage

6 Instruction decode.

7 Issue stage

8 Register read and instruction issue.

9 MP11 CPU integer execution pipeline.

10 Four stages of the MP11 CPU integer execution pipeline.

11 Shifter stage.

12 First stage of the multiply-accumulate pipeline.

13 Address generation stage.

14 Main integer operation calculation.

15 First stage of data cache access.

16 Second stage of the multiply-accumulate pipeline.

17 Pipeline stage to enable saturation of integer results.

18 Third stage of the multiply-accumulate pipeline.

19 Second stage of data cache access.

20 Write back of data from the multiply or main

execution pipelines.21 Write back of data from the Load Store Unit.

S M T W T F S S M T W T F S S M T W T F S S M T W T

Oct 21, '18 Oct 28, '18 Nov 4, '18 Nov 11, '18

Gantt Chart Full is shown below ("ARM Information Center", 2018).

7

Secure Best Marks with AI Grader

Need help grading? Try our AI Grader for instant feedback on your assignments.

Task Name Duration Start Finish Predecessors

Latest ARM Architecture 12 days Mon

10/22/18 Tue 11/6/18

Two Fetch stages 2 days Mon

10/22/18 Tue 10/23/18

First stage of instruction fetches and branch

prediction. 1 day Mon

10/22/18

Mon

10/22/18

Second stage of instruction fetches and branch

prediction. 1 day Tue 10/23/18 Tue 10/23/18 3

Decode stage 1 day Wed

10/24/18

Wed

10/24/18 2

Instruction decodes. 1 day Wed

10/24/18

Wed

10/24/18

Issue stage 1 day Thu

10/25/18

Thu

10/25/18 5

Register read and instruction issue. 1 day Thu 10/25/18 Thu 10/25/18

MP11 CPU integer execution pipeline. 8 days Fri 10/26/18 Tue 11/6/18 7

Four stages of the MP11 CPU integer

execution pipeline. 1 day Fri 10/26/18 Fri 10/26/18

Shifter stage. 2 days Mon

10/29/18 Tue 10/30/18 10

First stage of the multiply-accumulate

pipeline. 1 day Mon

10/29/18

Mon

10/29/18

Address generation stage. 1 day Tue 10/30/18 Tue 10/30/18 12

Main integer operation calculation. 2 days Wed

10/31/18 Thu 11/1/18 11

First stage of data cache access. 1 day Wed

10/31/18

Wed

10/31/18

Second stage of the multiply-accumulate

pipeline. 1 day Thu 11/1/18 Thu 11/1/18 15

Pipeline stage to enable saturation of

integer results. 2 days Fri 11/2/18 Mon 11/5/18 14

Third stage of the multiply-accumulate

pipeline. 1 day Fri 11/2/18 Fri 11/2/18

Second stage of data cache access. 1 day Mon 11/5/18 Mon 11/5/18 18

Write back of data from the multiply or

main execution pipelines. 1 day Tue 11/6/18 Tue 11/6/18 17

Write back of data from the Load Store Unit. 1 day Tue 11/6/18 Tue 11/6/18

8

Latest ARM Architecture 12 days Mon

10/22/18 Tue 11/6/18

Two Fetch stages 2 days Mon

10/22/18 Tue 10/23/18

First stage of instruction fetches and branch

prediction. 1 day Mon

10/22/18

Mon

10/22/18

Second stage of instruction fetches and branch

prediction. 1 day Tue 10/23/18 Tue 10/23/18 3

Decode stage 1 day Wed

10/24/18

Wed

10/24/18 2

Instruction decodes. 1 day Wed

10/24/18

Wed

10/24/18

Issue stage 1 day Thu

10/25/18

Thu

10/25/18 5

Register read and instruction issue. 1 day Thu 10/25/18 Thu 10/25/18

MP11 CPU integer execution pipeline. 8 days Fri 10/26/18 Tue 11/6/18 7

Four stages of the MP11 CPU integer

execution pipeline. 1 day Fri 10/26/18 Fri 10/26/18

Shifter stage. 2 days Mon

10/29/18 Tue 10/30/18 10

First stage of the multiply-accumulate

pipeline. 1 day Mon

10/29/18

Mon

10/29/18

Address generation stage. 1 day Tue 10/30/18 Tue 10/30/18 12

Main integer operation calculation. 2 days Wed

10/31/18 Thu 11/1/18 11

First stage of data cache access. 1 day Wed

10/31/18

Wed

10/31/18

Second stage of the multiply-accumulate

pipeline. 1 day Thu 11/1/18 Thu 11/1/18 15

Pipeline stage to enable saturation of

integer results. 2 days Fri 11/2/18 Mon 11/5/18 14

Third stage of the multiply-accumulate

pipeline. 1 day Fri 11/2/18 Fri 11/2/18

Second stage of data cache access. 1 day Mon 11/5/18 Mon 11/5/18 18

Write back of data from the multiply or

main execution pipelines. 1 day Tue 11/6/18 Tue 11/6/18 17

Write back of data from the Load Store Unit. 1 day Tue 11/6/18 Tue 11/6/18

8

References

ARM Information Center. (2018). Retrieved from http://infocenter.arm.com/help/index.jsp?

topic=/com.arm.doc.ddi0084f/ch01s01s01.html

Biafore, B. (2013). Microsoft Project 2013. Sebastopol: O'Reilly Media.

Cicala, G. (2013). Project management using Microsoft Project 2013. Wilmington, DE: Project

Assistants, Inc.

Happy, R. (2010). Project 2010 Project Management. Hoboken: John Wiley & Sons.

9

ARM Information Center. (2018). Retrieved from http://infocenter.arm.com/help/index.jsp?

topic=/com.arm.doc.ddi0084f/ch01s01s01.html

Biafore, B. (2013). Microsoft Project 2013. Sebastopol: O'Reilly Media.

Cicala, G. (2013). Project management using Microsoft Project 2013. Wilmington, DE: Project

Assistants, Inc.

Happy, R. (2010). Project 2010 Project Management. Hoboken: John Wiley & Sons.

9

1 out of 9

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)