Electrical Engineering: Phase Locked Loop (PLL) MATLAB Simulation

VerifiedAdded on 2023/01/18

|4

|724

|57

Practical Assignment

AI Summary

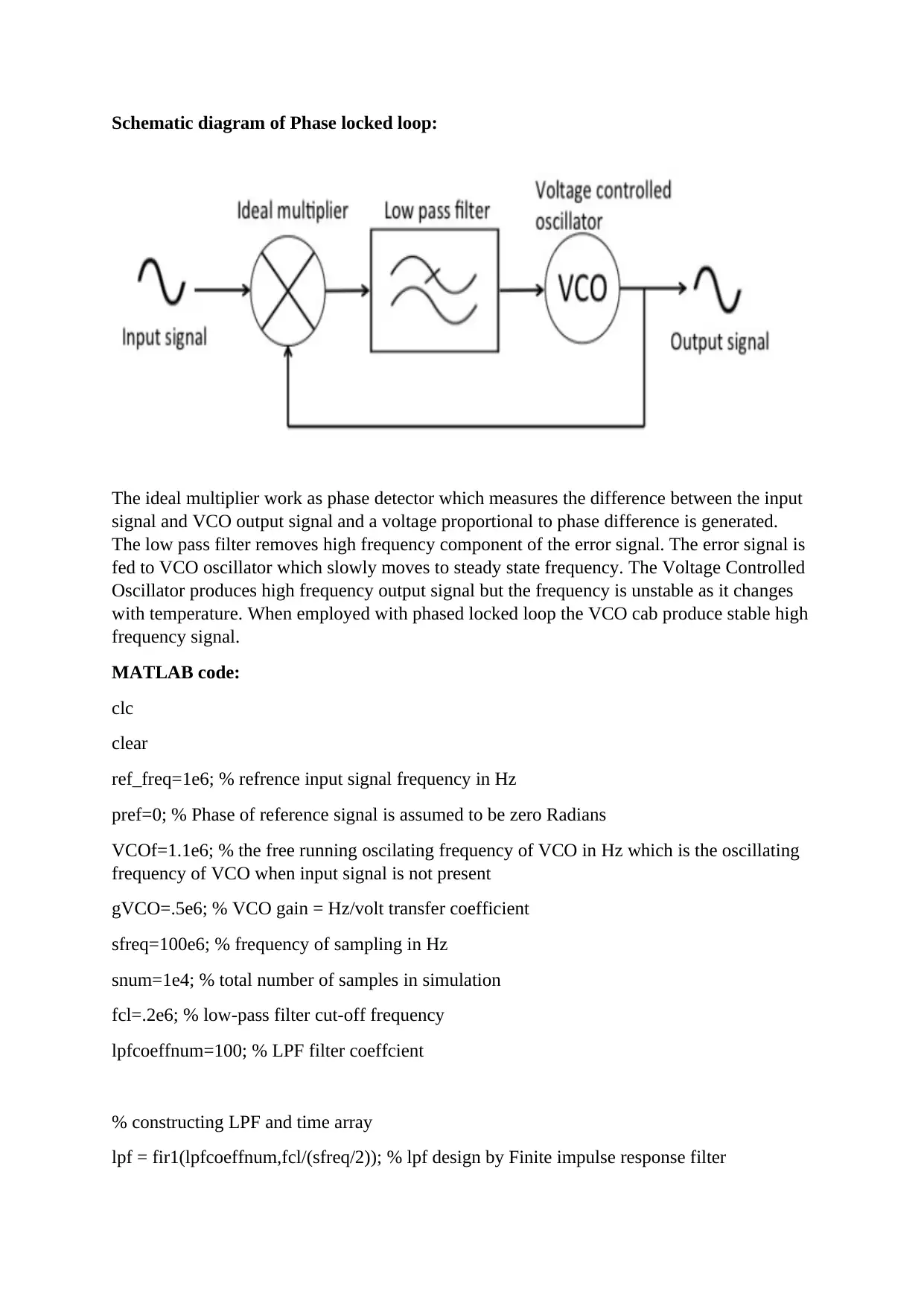

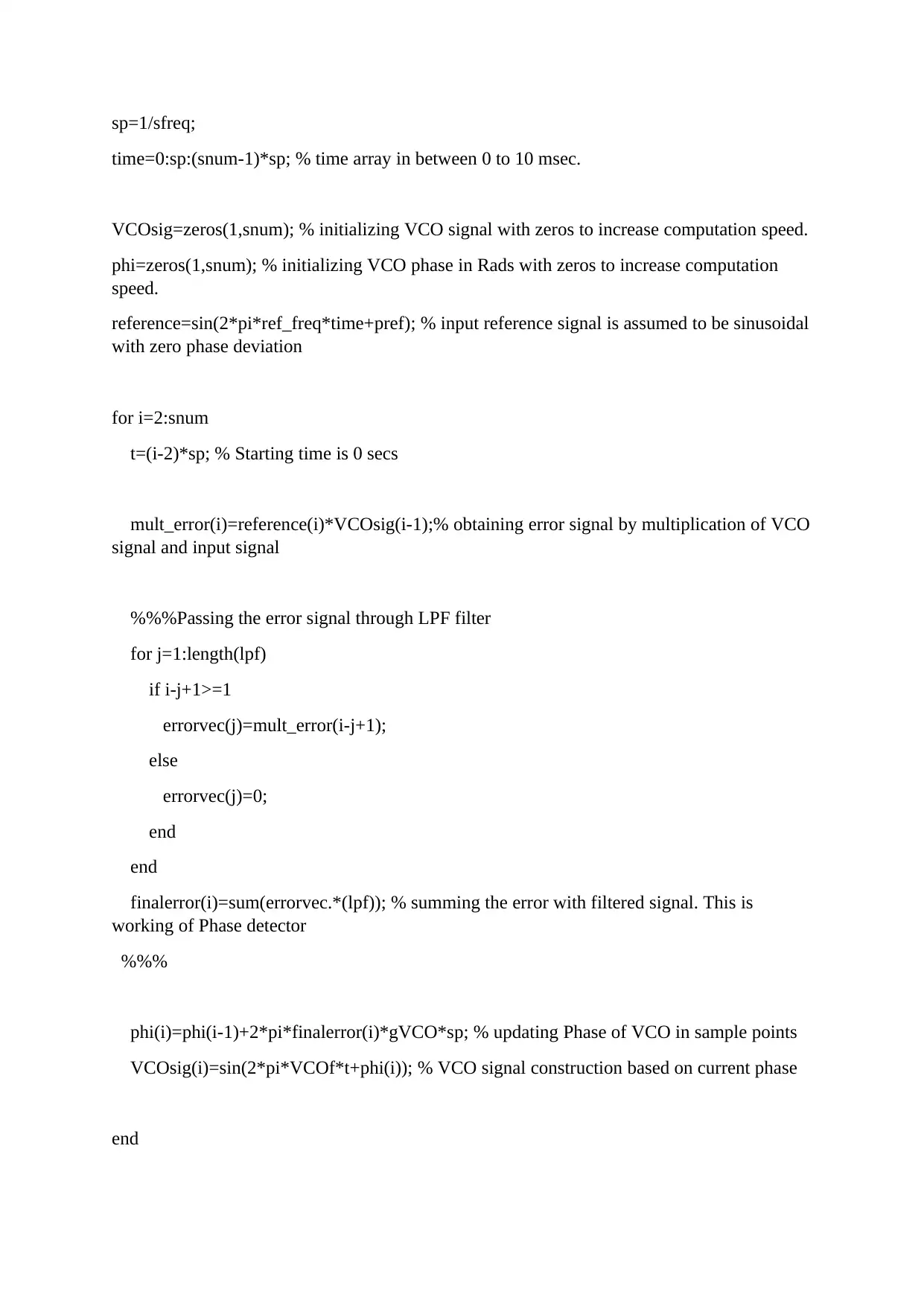

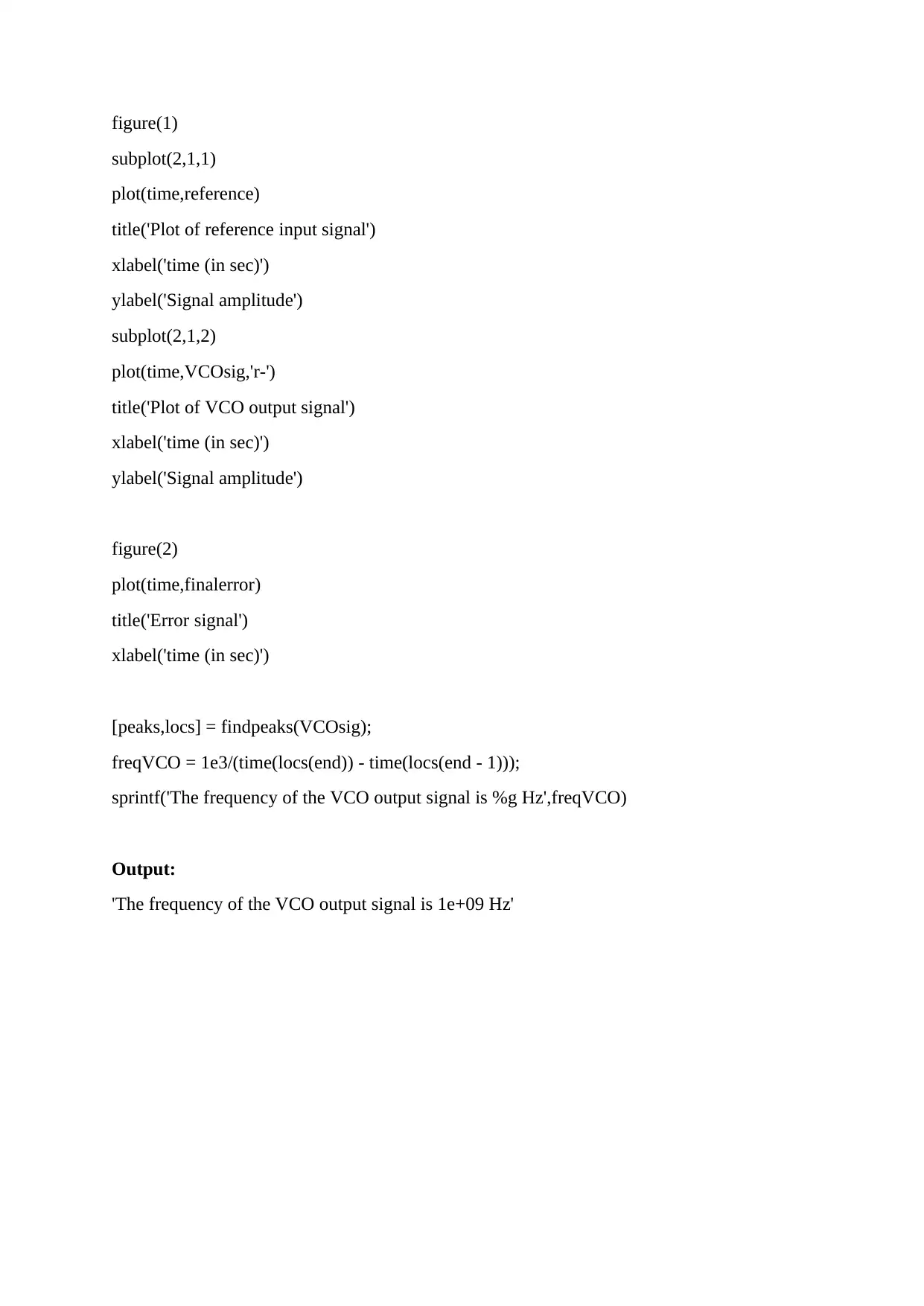

This assignment presents a detailed MATLAB simulation of a Phase Locked Loop (PLL). It begins with a schematic diagram illustrating the PLL's components: a phase detector (multiplier), a low-pass filter, and a voltage-controlled oscillator (VCO). The simulation then provides MATLAB code that implements the PLL, defining parameters such as reference frequency, VCO free-running frequency, VCO gain, sampling frequency, and filter coefficients. The code constructs the input reference signal and VCO output signal over time, calculating the error signal and updating the VCO's phase. The output includes plots of the reference input signal, VCO output signal, and error signal, along with the calculated VCO output frequency. This assignment serves as a practical example of PLL design and analysis, demonstrating how a PLL can be used to generate a stable high-frequency signal.

1 out of 4

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)