Traffic Light Controller Design: ELEC2141 Assignment Solution

VerifiedAdded on 2023/04/06

|13

|839

|100

Project

AI Summary

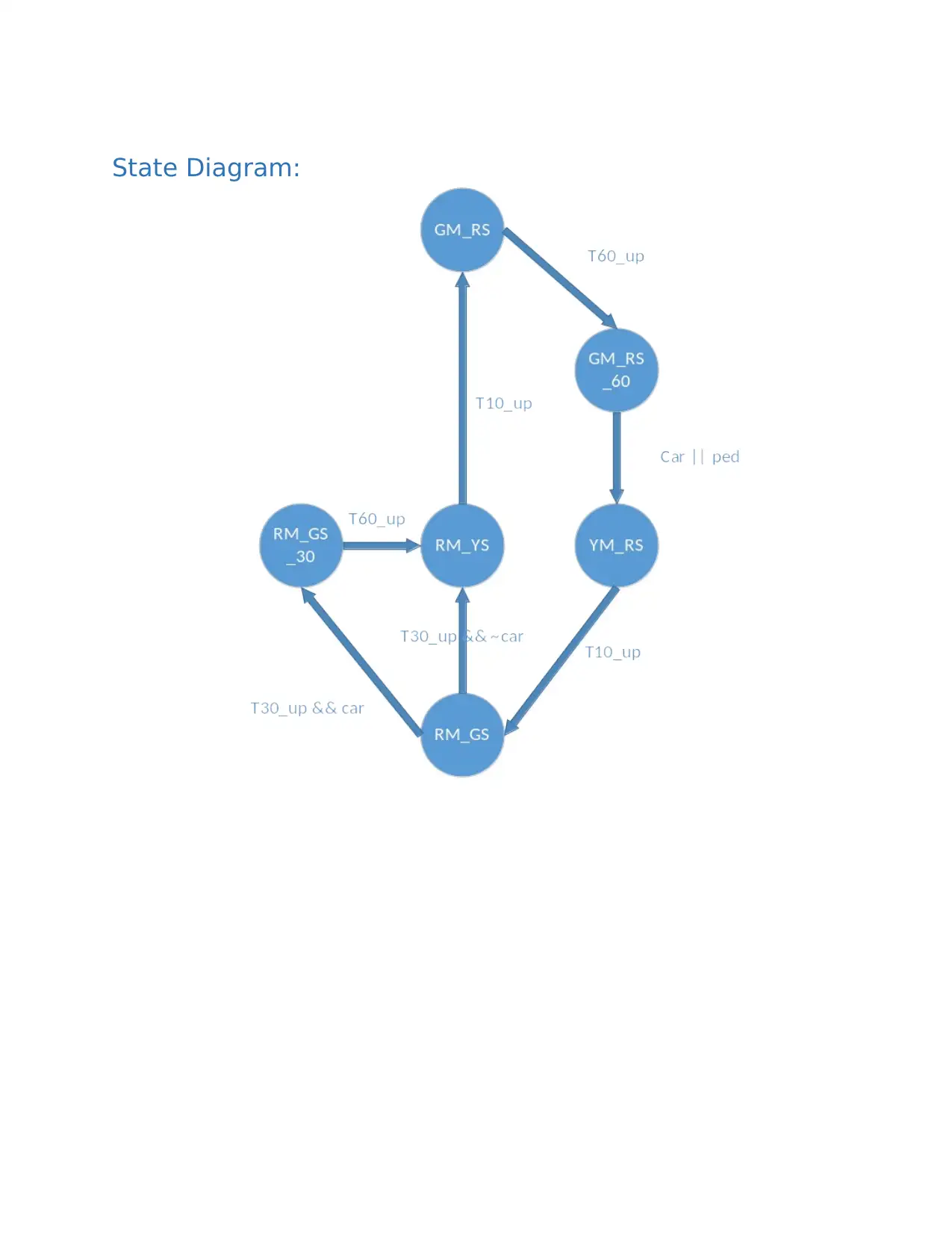

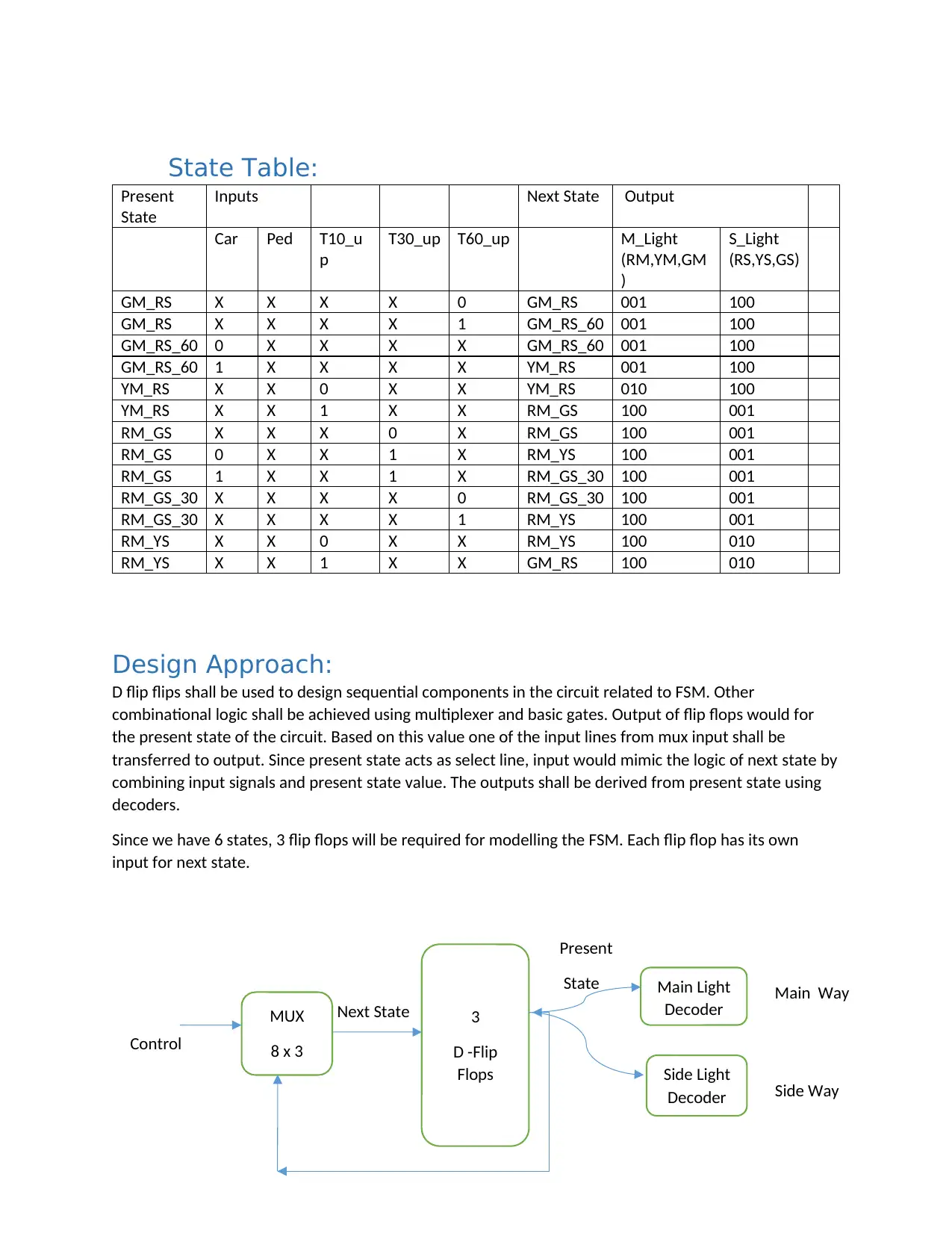

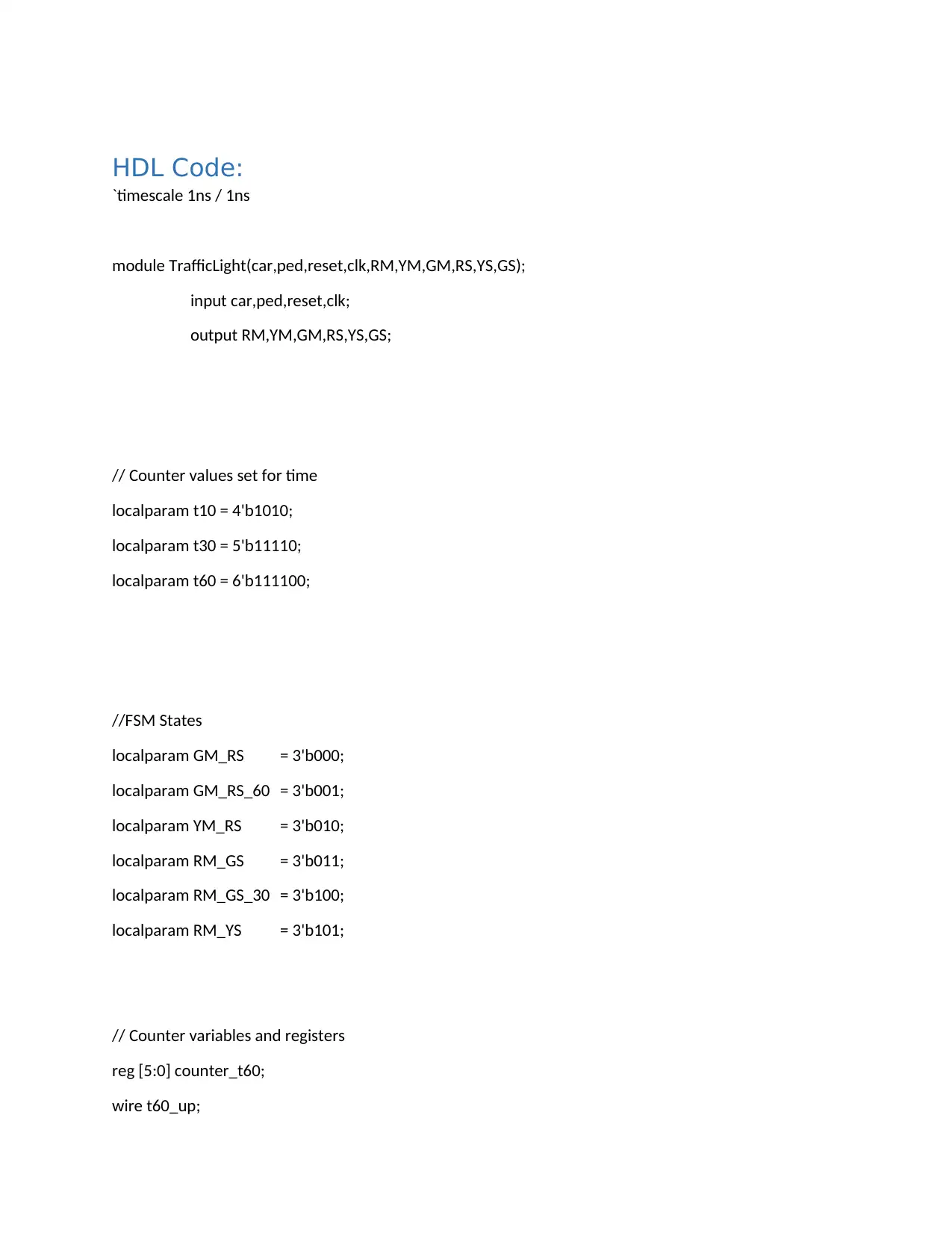

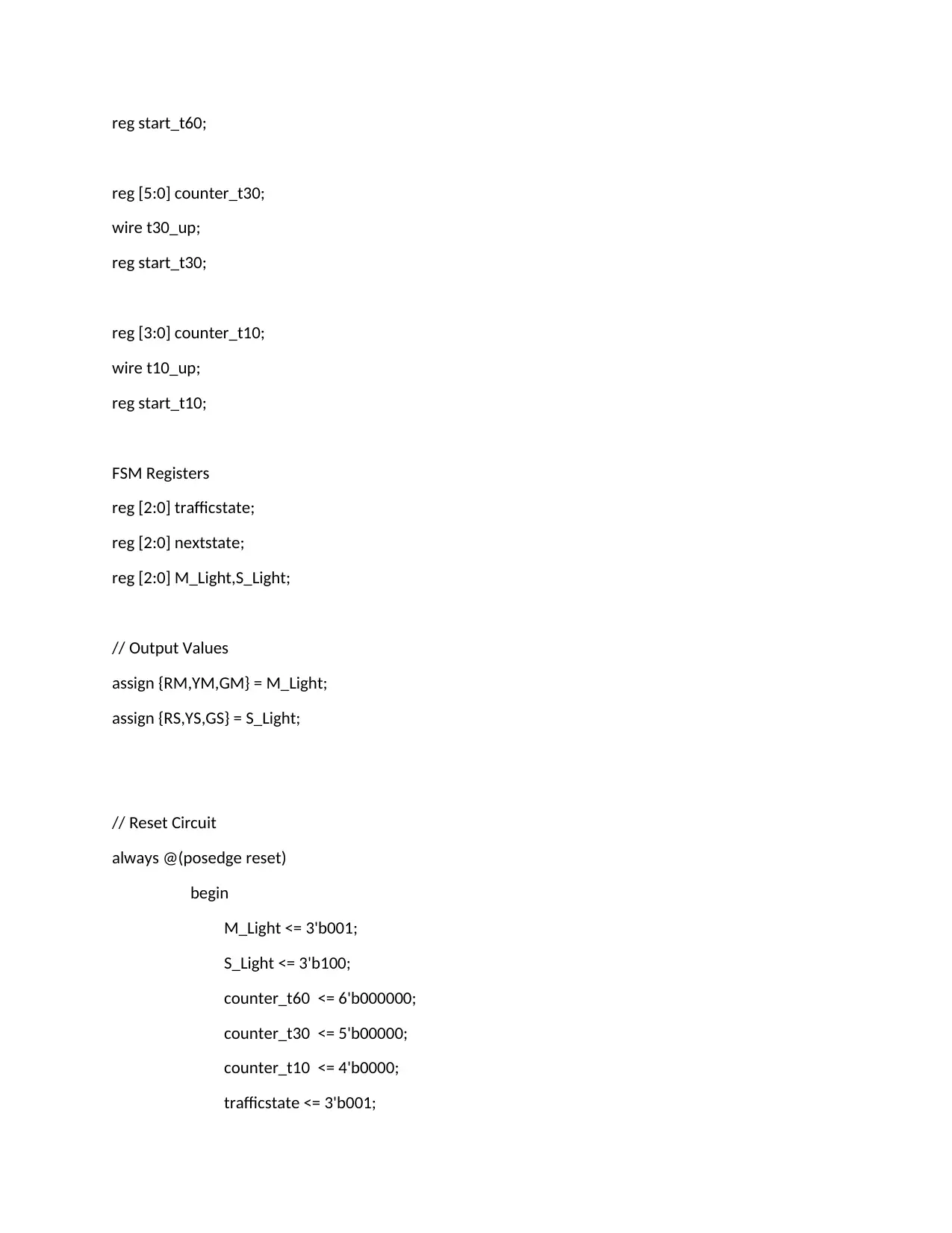

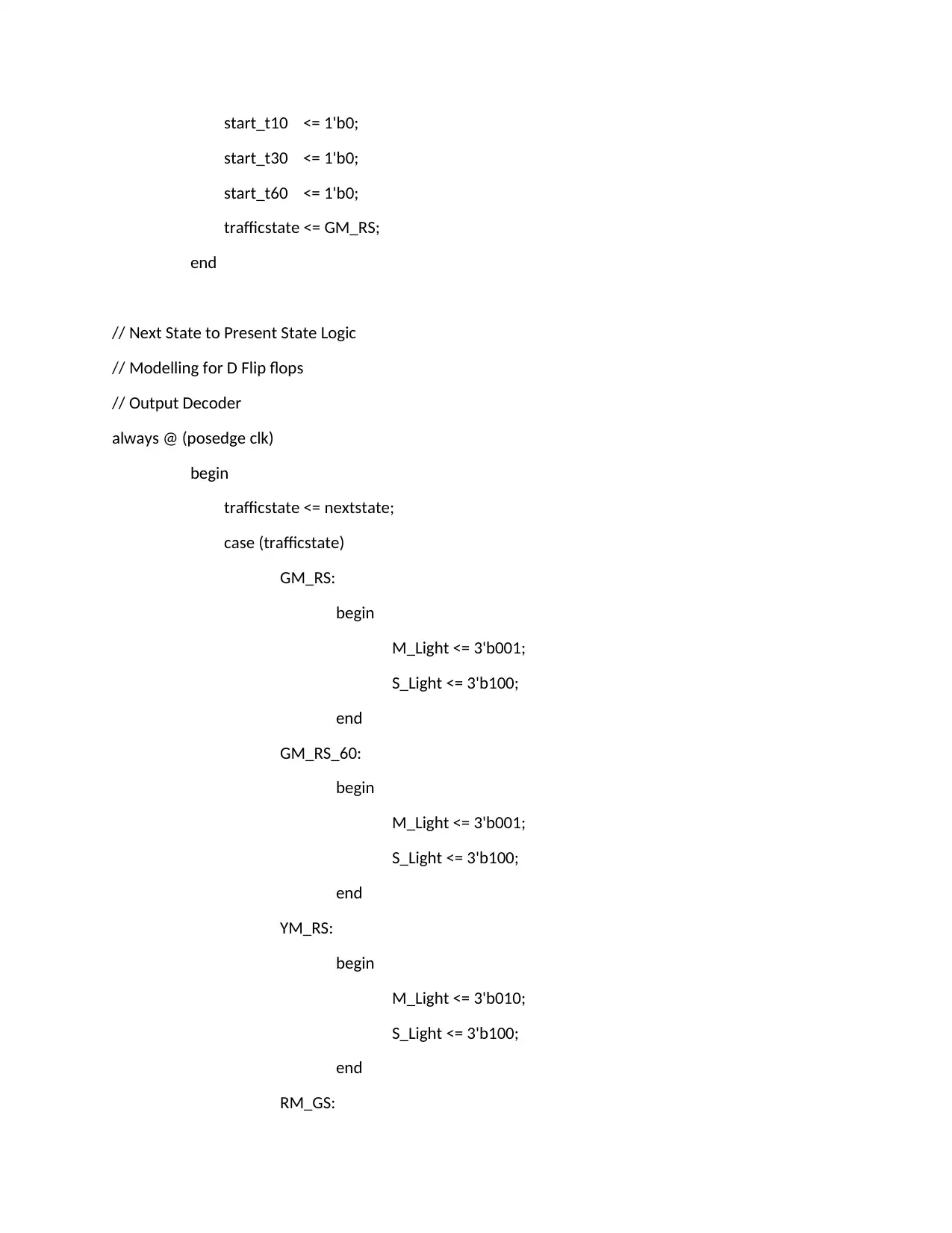

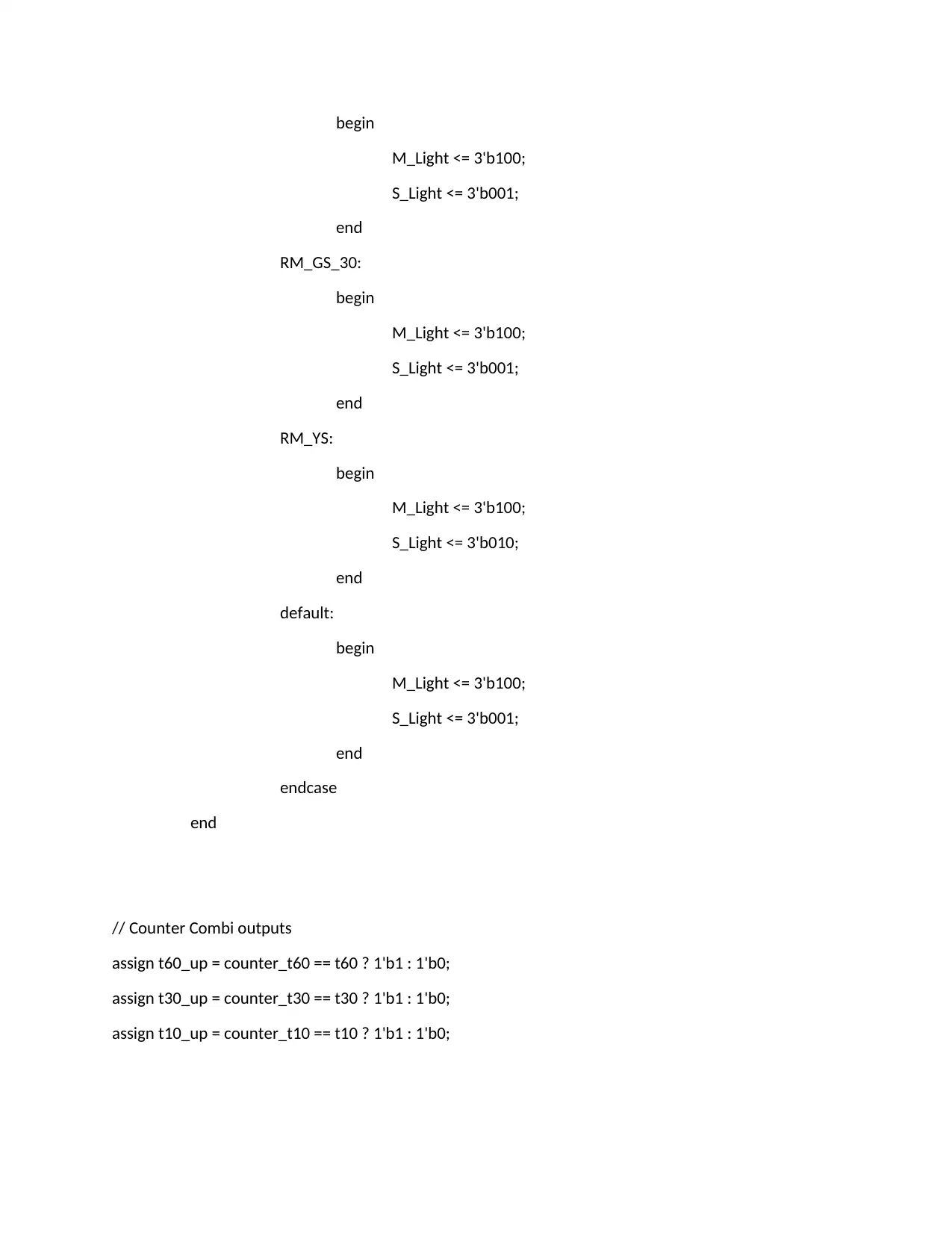

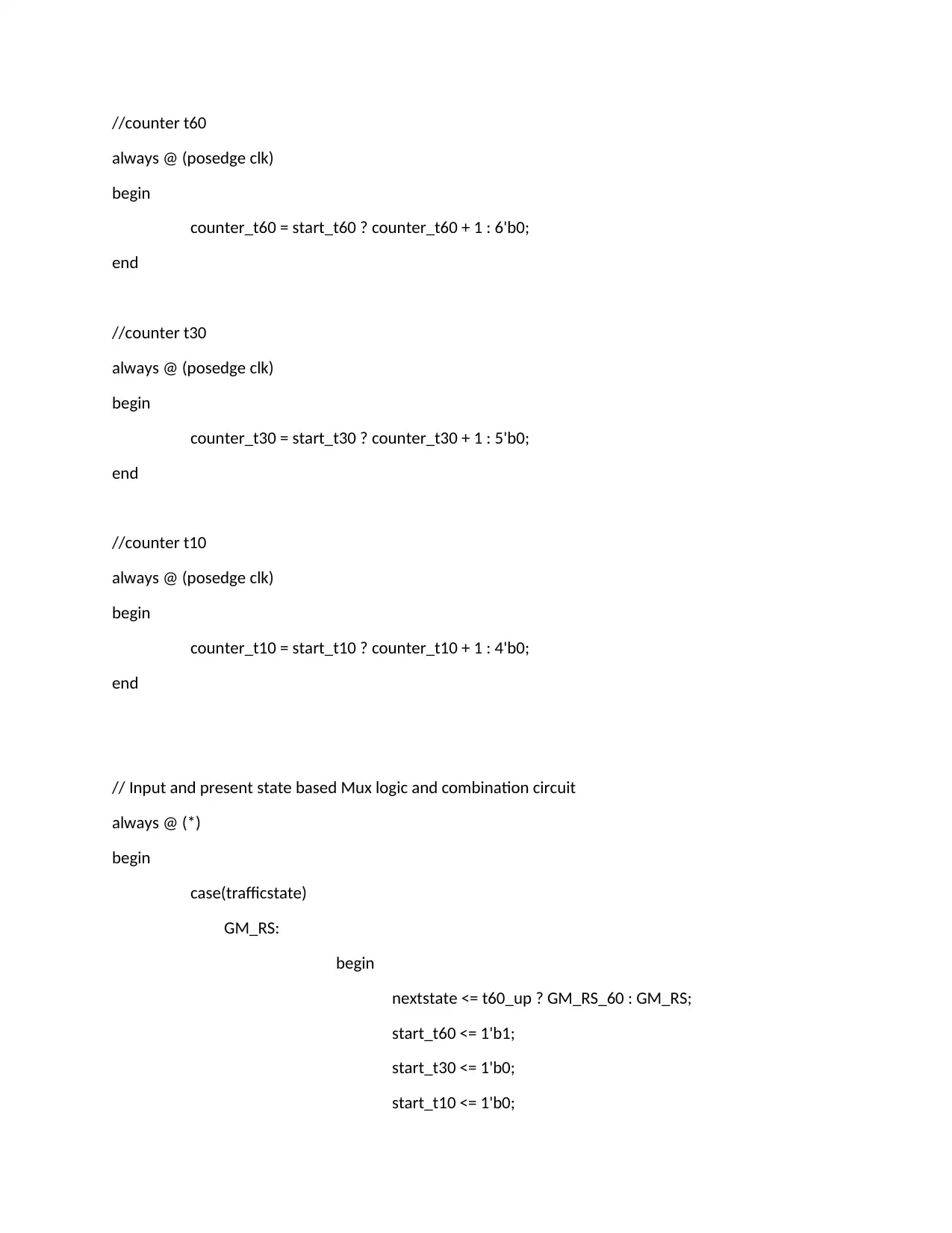

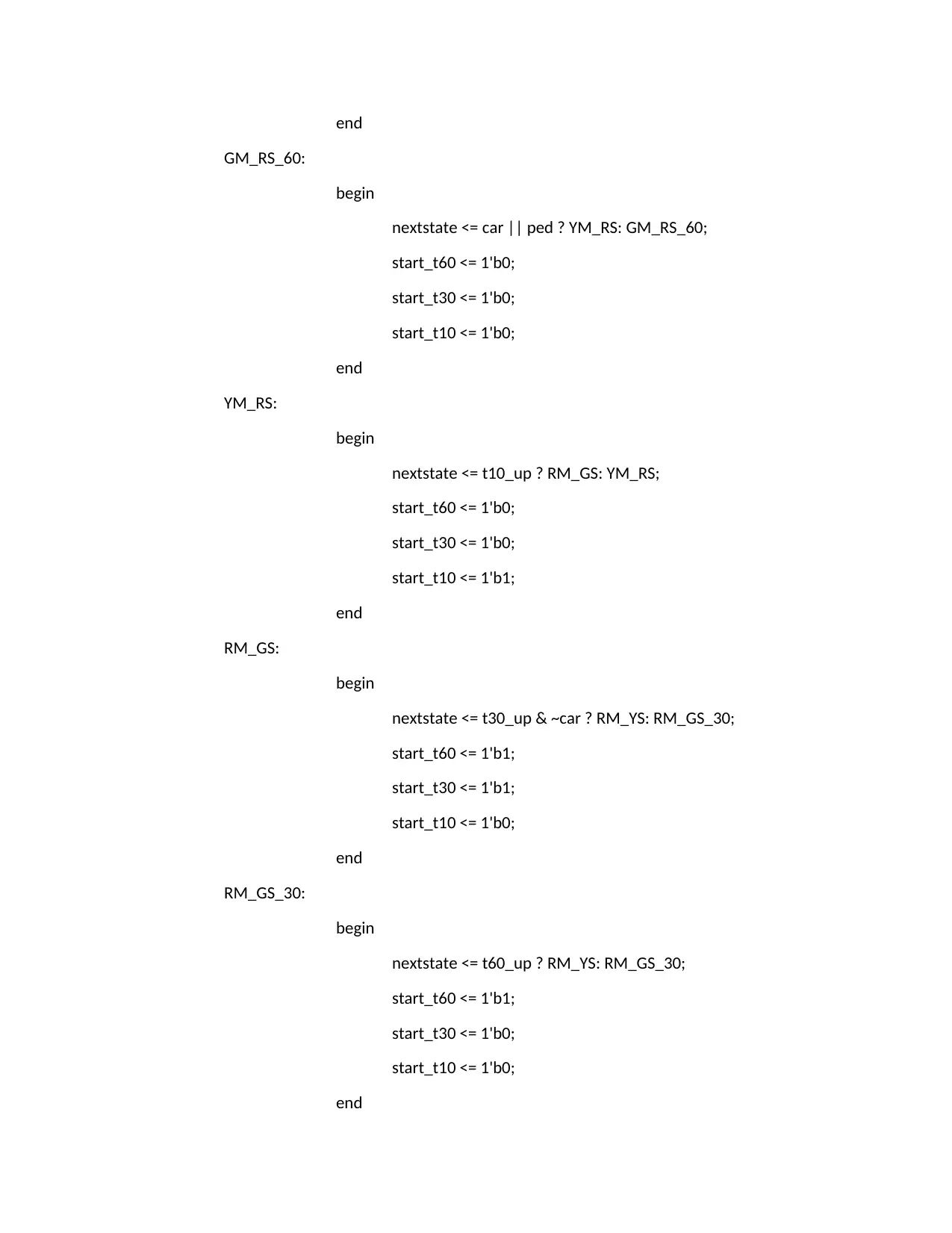

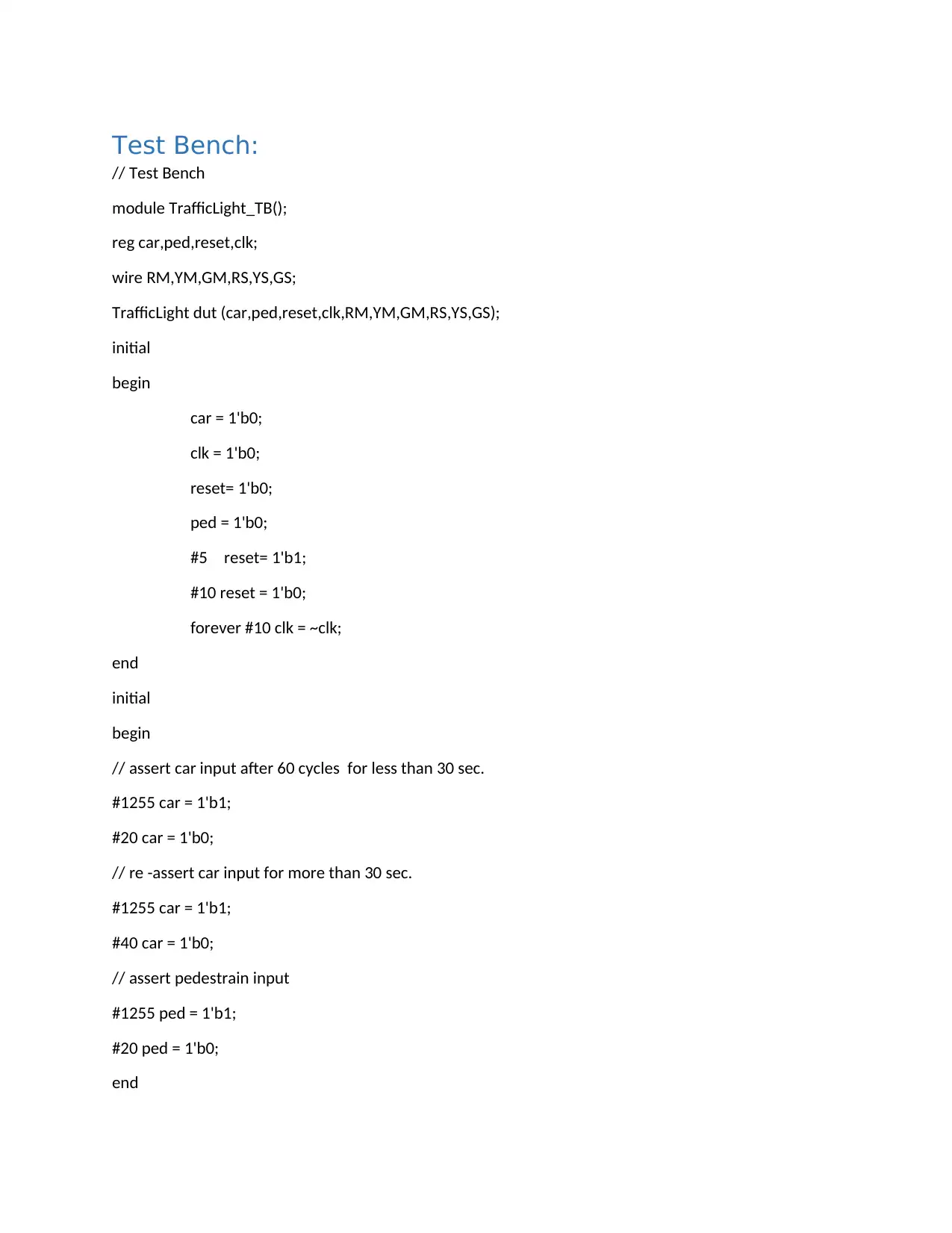

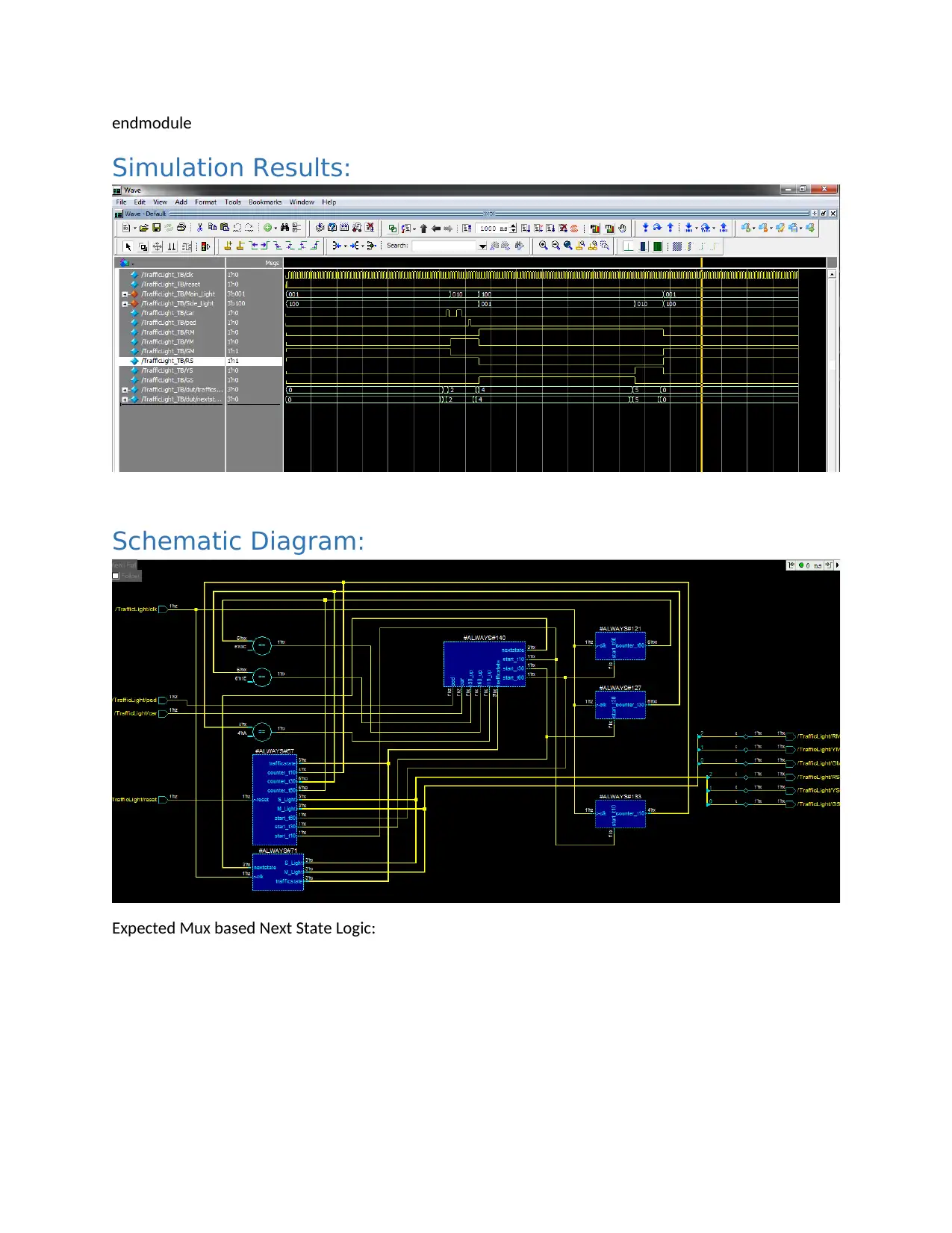

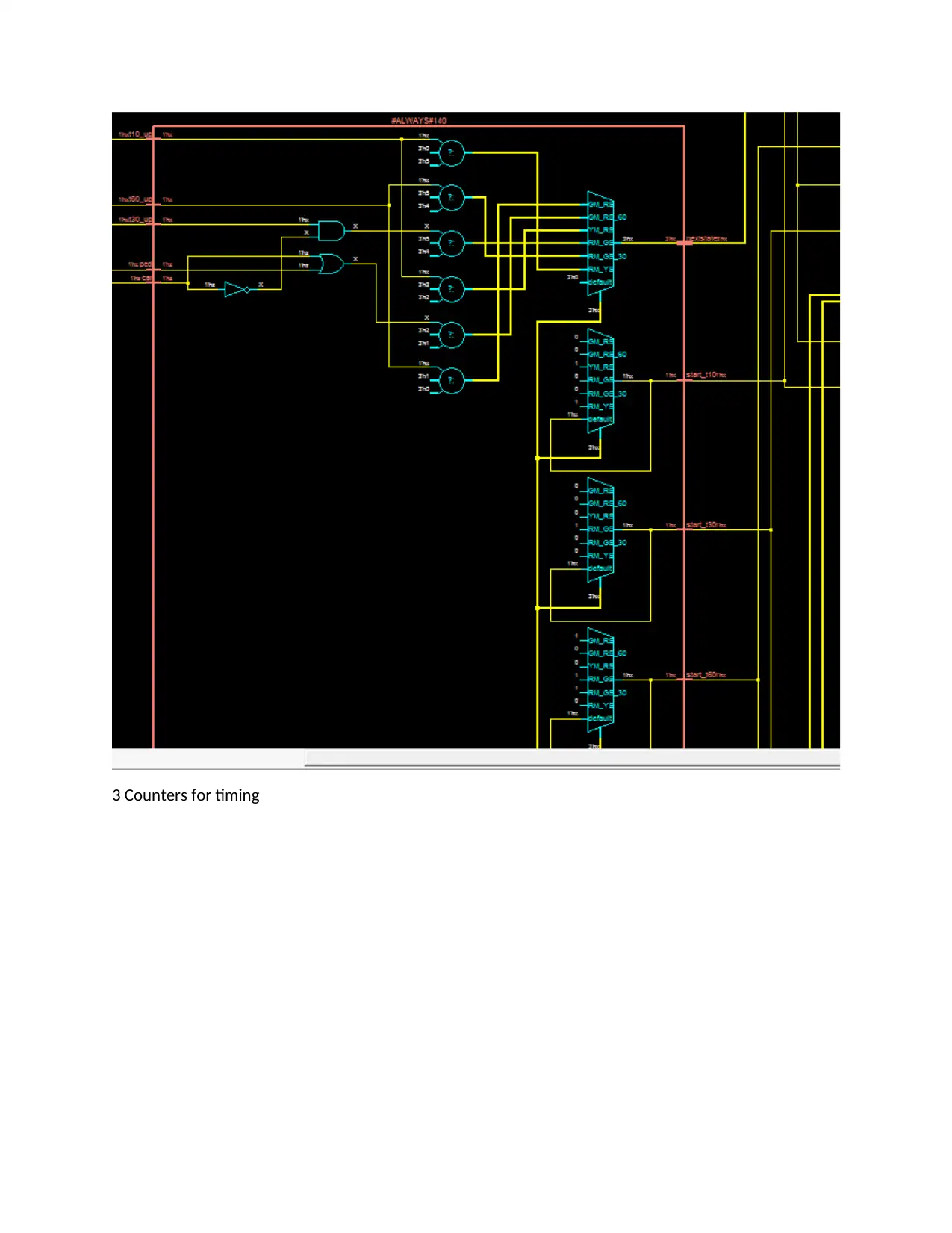

This document presents a detailed solution for a traffic light controller design, addressing the requirements of the ELEC2141 Digital Circuit Design assignment. The solution begins with a state diagram and state table, followed by a design approach utilizing D flip-flops for sequential components and multiplexers with basic gates for combinational logic. The assignment includes the HDL code in Verilog, defining states, counters, and logic for the traffic light's operation, along with a test bench for simulation and verification. The test bench simulates various scenarios, including car and pedestrian inputs. The simulation results, schematic diagram, and expected MUX-based next-state logic are also provided, ensuring a comprehensive understanding of the traffic light controller's functionality. The assignment is a complete project solution, incorporating all necessary components for a thorough design and implementation of the traffic light controller.

1 out of 13

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)