VHDL Assignment: Register File Implementation in VHDL

Write and test a VHDL entity to model a register file and submit the VHDL source files along with a report documenting the system structure.

4 Pages928 Words211 Views

Added on 2023-04-20

About This Document

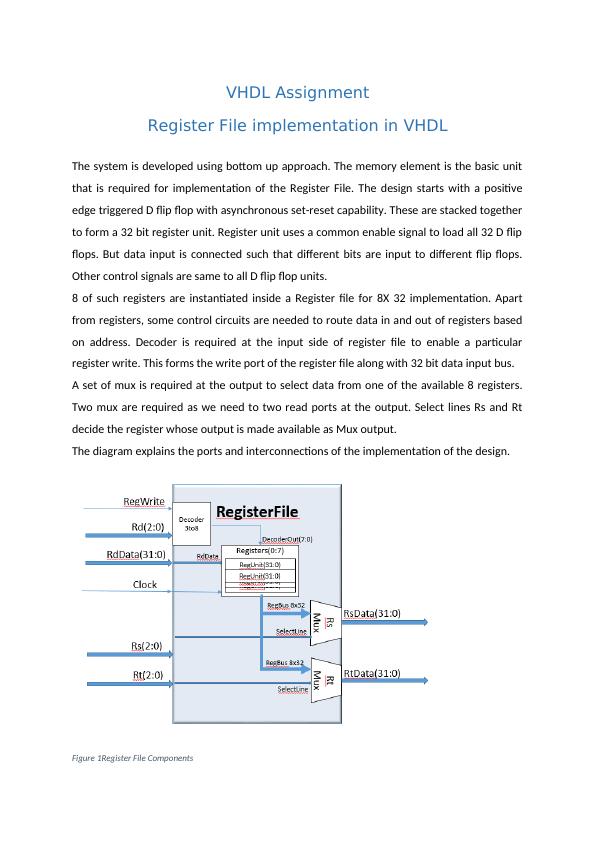

This VHDL assignment focuses on the implementation of a Register File using a bottom-up approach. It covers the design of memory elements, control circuits, and multiplexers. The code sections and testbench for verification are also provided.

VHDL Assignment: Register File Implementation in VHDL

Write and test a VHDL entity to model a register file and submit the VHDL source files along with a report documenting the system structure.

Added on 2023-04-20

ShareRelated Documents

End of preview

Want to access all the pages? Upload your documents or become a member.