University Project: Designing a Virtual Memory Manager (CS 440)

VerifiedAdded on 2023/05/29

|4

|553

|446

Project

AI Summary

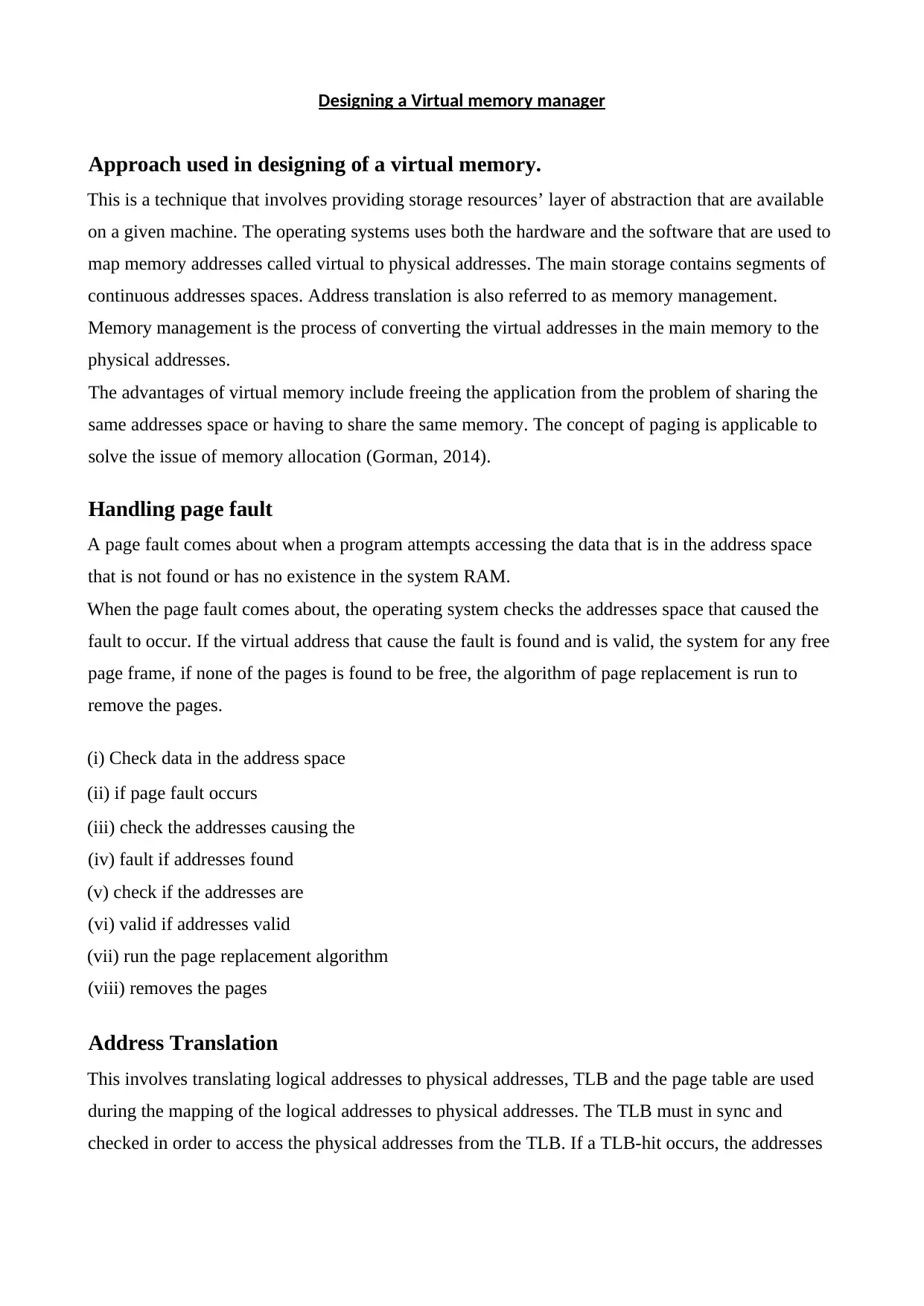

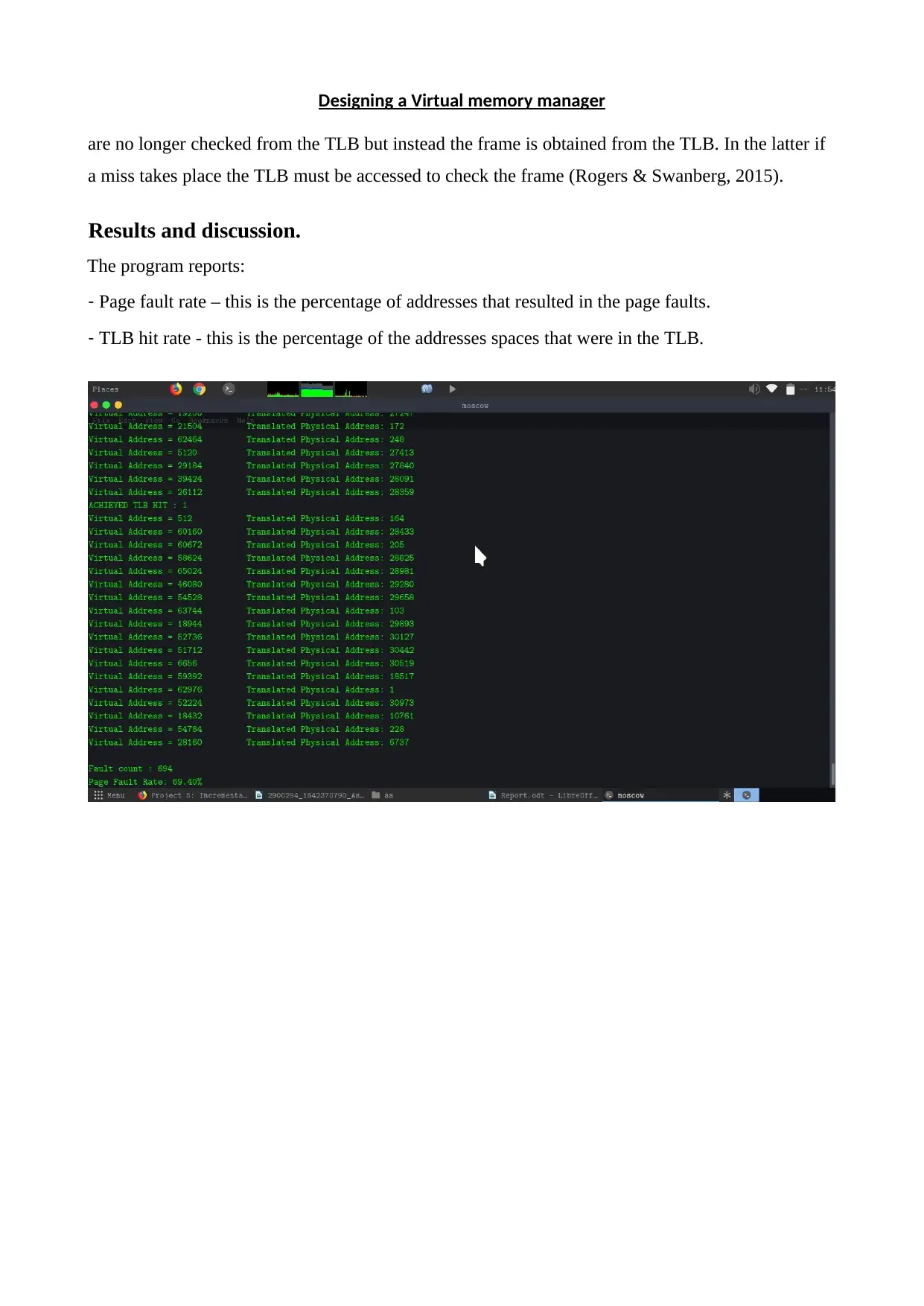

This project focuses on designing a virtual memory manager for a virtual address space of 65,536 bytes. The solution involves translating logical addresses to physical addresses using a TLB and a page table. The project includes a program that reads logical addresses from a file and outputs the corresponding physical addresses and byte values. The report details the approach, including pseudo-code, results, and discussion, such as page fault rates and TLB hit rates. Innovative features like using hashing for the page table are also discussed. The assignment covers key concepts like address translation, page faults, and page replacement algorithms. The solution includes a compilable and runnable code, a report, and references to support the implementation and understanding of virtual memory management principles.

1 out of 4

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)