ITC544 Assignment 2 Solution: RAM Chips and Instruction Set

VerifiedAdded on 2020/03/16

|3

|297

|170

Homework Assignment

AI Summary

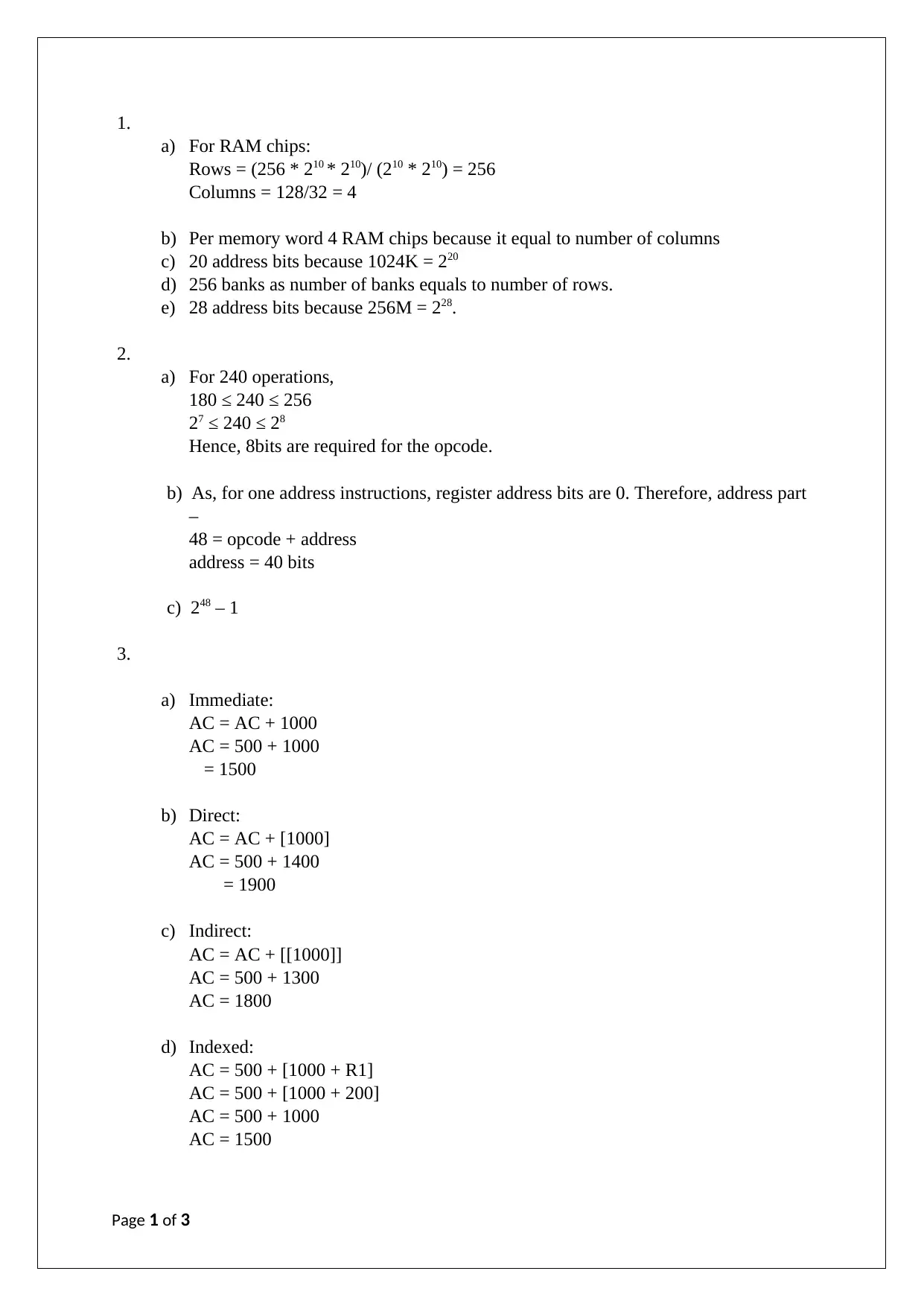

This assignment solution for ITC544 covers several key concepts in computer architecture. The solution begins with an analysis of RAM chips, calculating the number of rows, columns, and banks based on given parameters. It then delves into instruction set design, determining the number of bits required for opcodes based on the number of operations. Furthermore, the solution explores different addressing modes, calculating effective addresses for immediate, direct, indirect, and indexed addressing. Finally, the assignment demonstrates the implementation of code using different instruction formats: 2-address, 1-address, and 0-address machines, showcasing the versatility of instruction sets in performing operations. This solution provides a comprehensive understanding of computer organization and assembly language principles.

1 out of 3

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)