CISC and RISC Architectures: Advantages, Disadvantages, and Comparison

VerifiedAdded on 2020/04/07

|8

|1605

|930

Report

AI Summary

This report provides a comprehensive comparison of CISC (Complex Instruction Set Computer) and RISC (Reduced Instruction Set Computer) architectures. It begins with an introduction to instruction set design and its role in processor functionality, highlighting the differences between CISC and RISC. The report delves into the characteristics of each architecture, explaining the structure, advantages, and disadvantages of CISC, including its complex instruction set, variable instruction length, and microprogrammed control, alongside examples such as Intel 80486 and IBM 370/168. It then details the RISC architecture, emphasizing its simplified instruction set, pipelining, and extensive register sets, with examples like ARM and Power architecture. A comparative table summarizes the key differences between CISC and RISC. The report concludes by recommending RISC over CISC, citing its faster speed, reduced memory usage, and shorter structure cycle, and references relevant sources.

Running head: CISC and RISC Architecture 1

CISC and RISC Architecture

Name

Affiliate institution

CISC and RISC Architecture

Name

Affiliate institution

Paraphrase This Document

Need a fresh take? Get an instant paraphrase of this document with our AI Paraphraser

Running head: CISC and RISC Architecture 2

Table of Contents

RISC and CISC Architectures........................................................................................................................3

Introduction.............................................................................................................................................3

Computer Instruction Set Computer (CISC) Architecture:.......................................................................4

Reduced Instruction Set Computer (RISC)Architecture...........................................................................5

Advantages of CISC Architecture.............................................................................................................6

Advantages of RISC Architecture.............................................................................................................7

Conclusion...............................................................................................................................................7

Recommendation....................................................................................................................................7

References...................................................................................................................................................8

Table of Contents

RISC and CISC Architectures........................................................................................................................3

Introduction.............................................................................................................................................3

Computer Instruction Set Computer (CISC) Architecture:.......................................................................4

Reduced Instruction Set Computer (RISC)Architecture...........................................................................5

Advantages of CISC Architecture.............................................................................................................6

Advantages of RISC Architecture.............................................................................................................7

Conclusion...............................................................................................................................................7

Recommendation....................................................................................................................................7

References...................................................................................................................................................8

Running head: CISC and RISC Architecture 3

RISC and CISC Architectures

Introduction

Every processor is developed with the capabilities to implement a set of rules for executing a definite set

of basic functions. Instruction set design is the processor element which is required for creation of

machine level application programs to carry out any logical or mathematical operations.

The instruction set is fixed in the hardware which acts as a connection between hardware and software.

A compiler translates high level language to machine language.

If several complex commands are increased within the instruction set of the CPU, the processor

operations become slow and consumes a lot of time. [1]

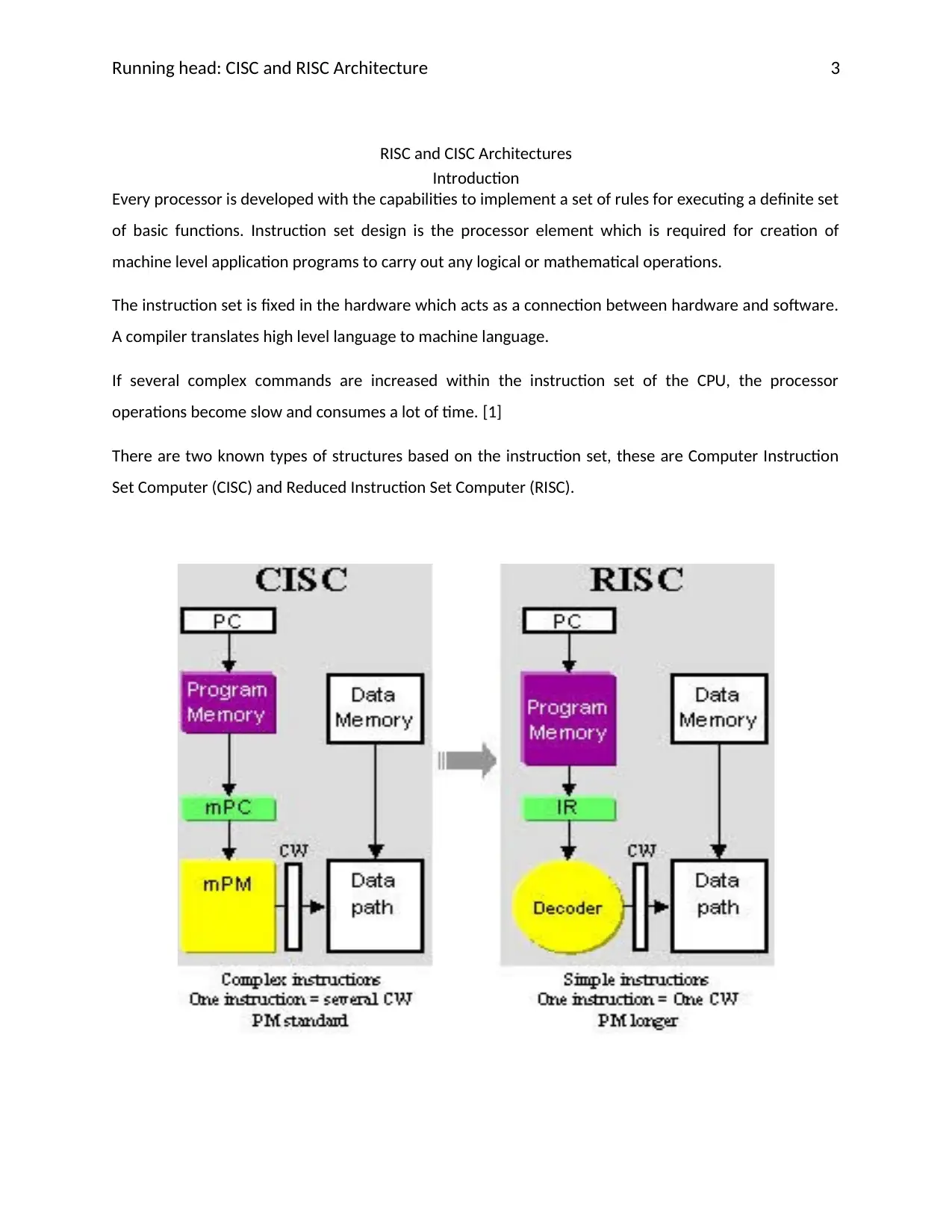

There are two known types of structures based on the instruction set, these are Computer Instruction

Set Computer (CISC) and Reduced Instruction Set Computer (RISC).

RISC and CISC Architectures

Introduction

Every processor is developed with the capabilities to implement a set of rules for executing a definite set

of basic functions. Instruction set design is the processor element which is required for creation of

machine level application programs to carry out any logical or mathematical operations.

The instruction set is fixed in the hardware which acts as a connection between hardware and software.

A compiler translates high level language to machine language.

If several complex commands are increased within the instruction set of the CPU, the processor

operations become slow and consumes a lot of time. [1]

There are two known types of structures based on the instruction set, these are Computer Instruction

Set Computer (CISC) and Reduced Instruction Set Computer (RISC).

⊘ This is a preview!⊘

Do you want full access?

Subscribe today to unlock all pages.

Trusted by 1+ million students worldwide

Running head: CISC and RISC Architecture 4

Computer Instruction Set Computer (CISC) Architecture:

The compiler changes high level language instructions to low level language instructions, prior to

execution of the instructions by the processor. Compilers had to change complex code into long series of

machine operations, if high level languages are designed for complex mathematical operations. As such,

the compiler construction consumed a lot of time. [2]

CISC was created to enhance easy construction of the compiler. The main objective of structuring CISC

processors is to create the processor with several elaborate instructions set.

Designing instructions for a CISC processor is simple as it offers single machine guidelines for the

statements structured in a high-level language.

An instruction with a changeable length format is incorporated by CISC. The instructions that need

register elements may consume two bytes while the instructions that need two memory addresses may

consume five bytes.

Thus, CISC has the changeable length encryption of instructions and the number of revolution needed to

run the instructions may be different.

several CISC designs, scan the inputs and write their results in the memory system rather than in a

register document. The figure above shows the structure of CISC with cache memory and programmed

control.

This architecture utilizes consolidated cache memory for storing both information and instructions.

Therefore, they have a common path for both data and instructions. Most instructions in this

architecture are kept in memory and run by microprogram and possesses several addressing modes and

instruction formats.

In CISC processor, command signals for running an instruction are created by a microprogram execution.

This micro program involves a series of microinstructions.

The microinstructions are run individually and in turn required control signals for instruction execution

are developed in steps. This may considerably reduce the speed of the instruction execution. Some of

the features of CISC include; large number of commands, utilization of several addressing modes,

commands that work on operands in memory, and variable length for command formats. Examples of

CISC processor include; Intel 80486, IBM 370/168, and VAX 11/780. [3]

Computer Instruction Set Computer (CISC) Architecture:

The compiler changes high level language instructions to low level language instructions, prior to

execution of the instructions by the processor. Compilers had to change complex code into long series of

machine operations, if high level languages are designed for complex mathematical operations. As such,

the compiler construction consumed a lot of time. [2]

CISC was created to enhance easy construction of the compiler. The main objective of structuring CISC

processors is to create the processor with several elaborate instructions set.

Designing instructions for a CISC processor is simple as it offers single machine guidelines for the

statements structured in a high-level language.

An instruction with a changeable length format is incorporated by CISC. The instructions that need

register elements may consume two bytes while the instructions that need two memory addresses may

consume five bytes.

Thus, CISC has the changeable length encryption of instructions and the number of revolution needed to

run the instructions may be different.

several CISC designs, scan the inputs and write their results in the memory system rather than in a

register document. The figure above shows the structure of CISC with cache memory and programmed

control.

This architecture utilizes consolidated cache memory for storing both information and instructions.

Therefore, they have a common path for both data and instructions. Most instructions in this

architecture are kept in memory and run by microprogram and possesses several addressing modes and

instruction formats.

In CISC processor, command signals for running an instruction are created by a microprogram execution.

This micro program involves a series of microinstructions.

The microinstructions are run individually and in turn required control signals for instruction execution

are developed in steps. This may considerably reduce the speed of the instruction execution. Some of

the features of CISC include; large number of commands, utilization of several addressing modes,

commands that work on operands in memory, and variable length for command formats. Examples of

CISC processor include; Intel 80486, IBM 370/168, and VAX 11/780. [3]

Paraphrase This Document

Need a fresh take? Get an instant paraphrase of this document with our AI Paraphraser

Running head: CISC and RISC Architecture 5

Reduced Instruction Set Computer (RISC)Architecture

In RISC architecture, the command set of the computer is made easy to minimize time of the execution.

It utilizes highly optimized and small and set of commands which are normally register to register

functions.

The frequency of the execution is maximized by using fewer number of commands as compared with

CISC which have single long command. And the augmentation of every command in the processor is

attained through pipeline method.

The pipelining method permits the processor to function on unique steps of instruction such as fetch,

decode, and execute commands at the same time. These cycles that is, fetch, decode and execute of

one or several commands in this pipeline method are overlapped.

Thus, several instructions can be run in a shorter period of time. So as to prevent more communication

or to minimize access time, RISC processors are issued with registers of multiple sets with enhanced

register utilization so that regularly viewed operands remain in high-speed storage.

The above figure is the structure of RISC processor, which utilizes different instruction and access paths

and data caches. In this architecture there is one command per machine cycle.

A machine cycle is described as the time covered to get two operands from registers, execute ALU

operation and keep the output in a register. Because of this one cycle command, instruction execution is

carried at a high speed in comparison to micro commands on CISC processor.

Most RISC processors utilize hardwired control for the instruction of the machine and therefore,

microinstructions are not necessary, thereby there is no need of accessing a control memory for

microprogram during execution of instruction as in the case of CISC processor. The structure of the

control unit is also easy because of the limited number of commands. Some of the features of RISC

include; restricted and minimized number of commands, utilization of lesser number of addressing

modes, simple and uniform instruction format, reduced access time of external memory by a large

number of registers, load and store commands possesses memory access, it is hardwired, and have

pipeline architecture. Some of the examples of RISC processors are alpha, PA-RISCA, VR, PIC, ARM, and

power architecture. [4]

Reduced Instruction Set Computer (RISC)Architecture

In RISC architecture, the command set of the computer is made easy to minimize time of the execution.

It utilizes highly optimized and small and set of commands which are normally register to register

functions.

The frequency of the execution is maximized by using fewer number of commands as compared with

CISC which have single long command. And the augmentation of every command in the processor is

attained through pipeline method.

The pipelining method permits the processor to function on unique steps of instruction such as fetch,

decode, and execute commands at the same time. These cycles that is, fetch, decode and execute of

one or several commands in this pipeline method are overlapped.

Thus, several instructions can be run in a shorter period of time. So as to prevent more communication

or to minimize access time, RISC processors are issued with registers of multiple sets with enhanced

register utilization so that regularly viewed operands remain in high-speed storage.

The above figure is the structure of RISC processor, which utilizes different instruction and access paths

and data caches. In this architecture there is one command per machine cycle.

A machine cycle is described as the time covered to get two operands from registers, execute ALU

operation and keep the output in a register. Because of this one cycle command, instruction execution is

carried at a high speed in comparison to micro commands on CISC processor.

Most RISC processors utilize hardwired control for the instruction of the machine and therefore,

microinstructions are not necessary, thereby there is no need of accessing a control memory for

microprogram during execution of instruction as in the case of CISC processor. The structure of the

control unit is also easy because of the limited number of commands. Some of the features of RISC

include; restricted and minimized number of commands, utilization of lesser number of addressing

modes, simple and uniform instruction format, reduced access time of external memory by a large

number of registers, load and store commands possesses memory access, it is hardwired, and have

pipeline architecture. Some of the examples of RISC processors are alpha, PA-RISCA, VR, PIC, ARM, and

power architecture. [4]

Running head: CISC and RISC Architecture 6

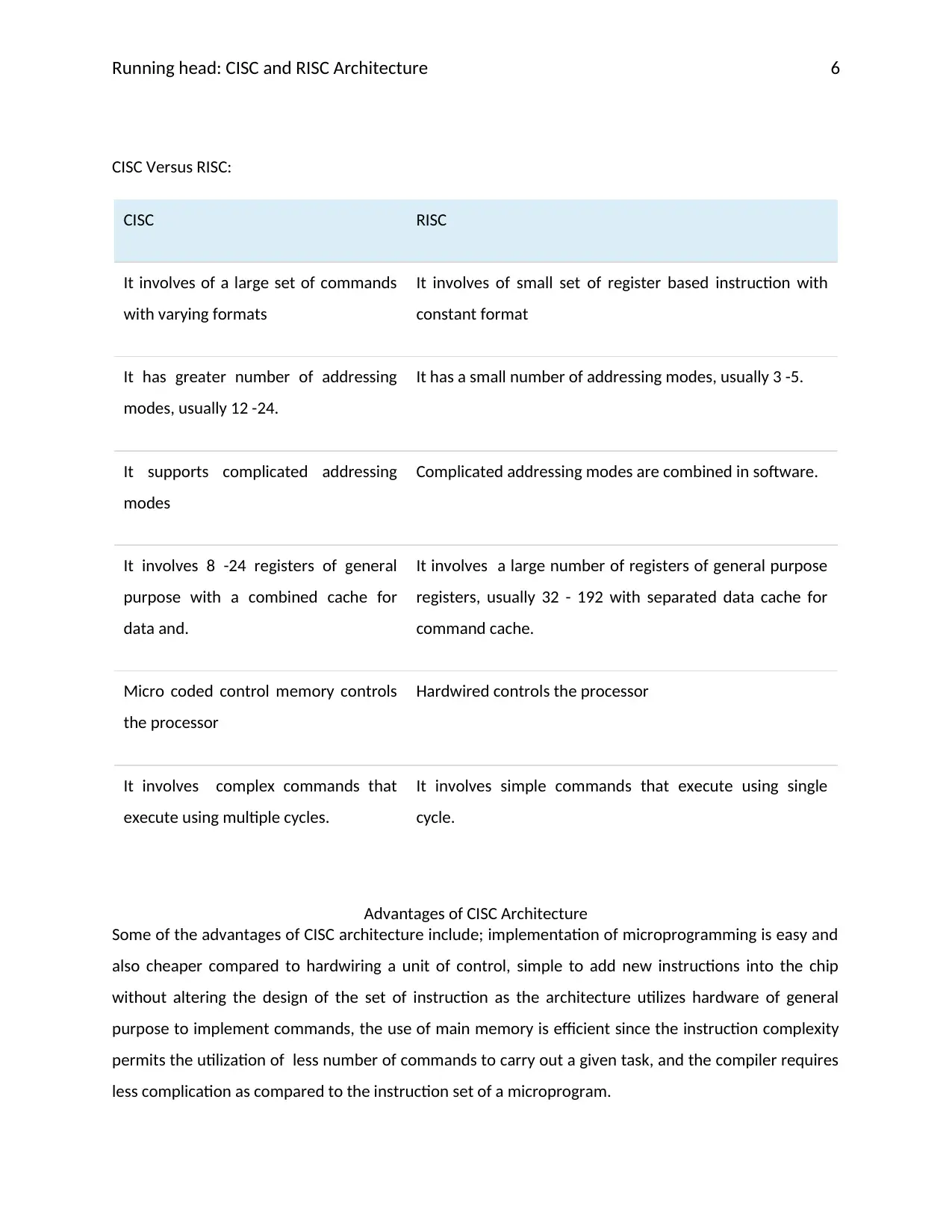

CISC Versus RISC:

CISC RISC

It involves of a large set of commands

with varying formats

It involves of small set of register based instruction with

constant format

It has greater number of addressing

modes, usually 12 -24.

It has a small number of addressing modes, usually 3 -5.

It supports complicated addressing

modes

Complicated addressing modes are combined in software.

It involves 8 -24 registers of general

purpose with a combined cache for

data and.

It involves a large number of registers of general purpose

registers, usually 32 - 192 with separated data cache for

command cache.

Micro coded control memory controls

the processor

Hardwired controls the processor

It involves complex commands that

execute using multiple cycles.

It involves simple commands that execute using single

cycle.

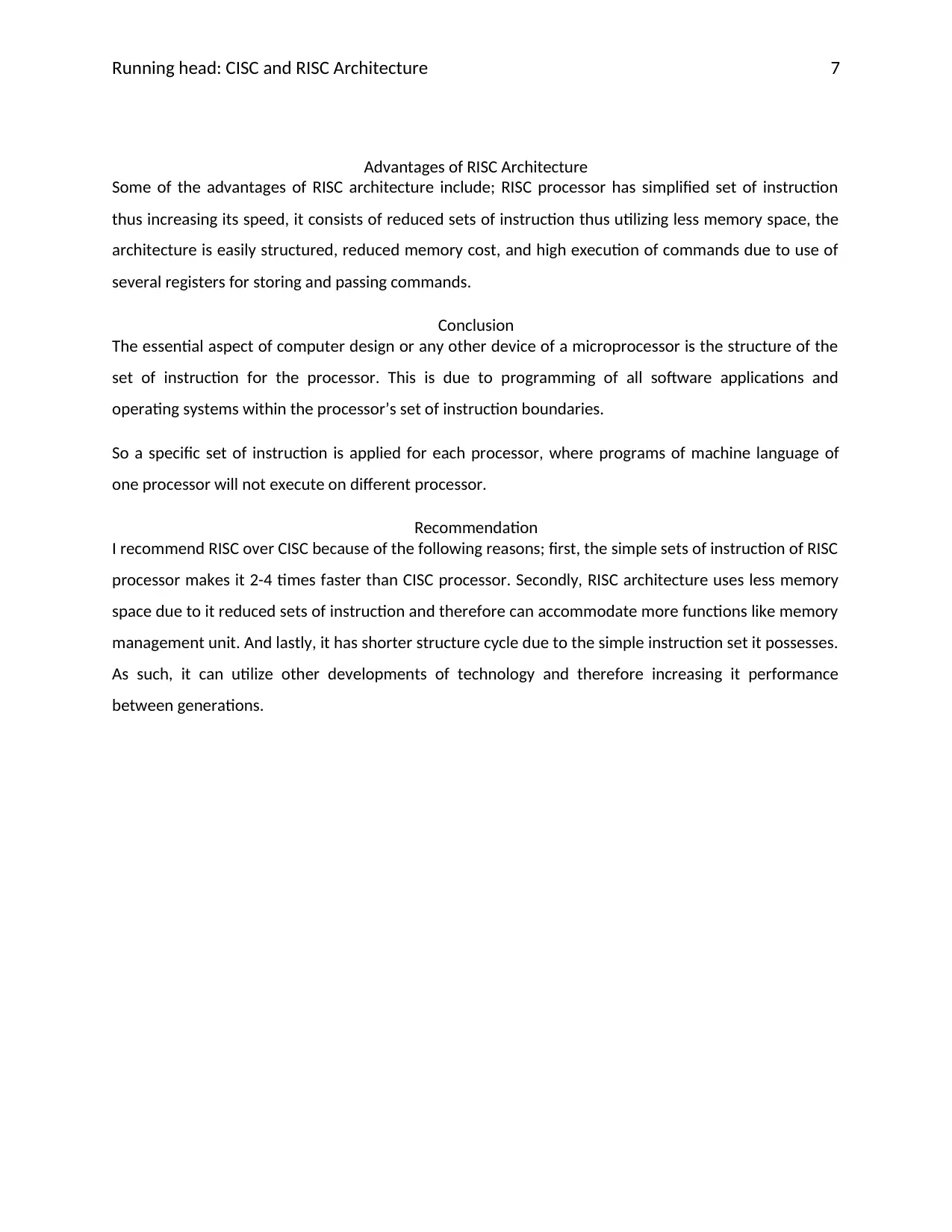

Advantages of CISC Architecture

Some of the advantages of CISC architecture include; implementation of microprogramming is easy and

also cheaper compared to hardwiring a unit of control, simple to add new instructions into the chip

without altering the design of the set of instruction as the architecture utilizes hardware of general

purpose to implement commands, the use of main memory is efficient since the instruction complexity

permits the utilization of less number of commands to carry out a given task, and the compiler requires

less complication as compared to the instruction set of a microprogram.

CISC Versus RISC:

CISC RISC

It involves of a large set of commands

with varying formats

It involves of small set of register based instruction with

constant format

It has greater number of addressing

modes, usually 12 -24.

It has a small number of addressing modes, usually 3 -5.

It supports complicated addressing

modes

Complicated addressing modes are combined in software.

It involves 8 -24 registers of general

purpose with a combined cache for

data and.

It involves a large number of registers of general purpose

registers, usually 32 - 192 with separated data cache for

command cache.

Micro coded control memory controls

the processor

Hardwired controls the processor

It involves complex commands that

execute using multiple cycles.

It involves simple commands that execute using single

cycle.

Advantages of CISC Architecture

Some of the advantages of CISC architecture include; implementation of microprogramming is easy and

also cheaper compared to hardwiring a unit of control, simple to add new instructions into the chip

without altering the design of the set of instruction as the architecture utilizes hardware of general

purpose to implement commands, the use of main memory is efficient since the instruction complexity

permits the utilization of less number of commands to carry out a given task, and the compiler requires

less complication as compared to the instruction set of a microprogram.

⊘ This is a preview!⊘

Do you want full access?

Subscribe today to unlock all pages.

Trusted by 1+ million students worldwide

Running head: CISC and RISC Architecture 7

Advantages of RISC Architecture

Some of the advantages of RISC architecture include; RISC processor has simplified set of instruction

thus increasing its speed, it consists of reduced sets of instruction thus utilizing less memory space, the

architecture is easily structured, reduced memory cost, and high execution of commands due to use of

several registers for storing and passing commands.

Conclusion

The essential aspect of computer design or any other device of a microprocessor is the structure of the

set of instruction for the processor. This is due to programming of all software applications and

operating systems within the processor’s set of instruction boundaries.

So a specific set of instruction is applied for each processor, where programs of machine language of

one processor will not execute on different processor.

Recommendation

I recommend RISC over CISC because of the following reasons; first, the simple sets of instruction of RISC

processor makes it 2-4 times faster than CISC processor. Secondly, RISC architecture uses less memory

space due to it reduced sets of instruction and therefore can accommodate more functions like memory

management unit. And lastly, it has shorter structure cycle due to the simple instruction set it possesses.

As such, it can utilize other developments of technology and therefore increasing it performance

between generations.

Advantages of RISC Architecture

Some of the advantages of RISC architecture include; RISC processor has simplified set of instruction

thus increasing its speed, it consists of reduced sets of instruction thus utilizing less memory space, the

architecture is easily structured, reduced memory cost, and high execution of commands due to use of

several registers for storing and passing commands.

Conclusion

The essential aspect of computer design or any other device of a microprocessor is the structure of the

set of instruction for the processor. This is due to programming of all software applications and

operating systems within the processor’s set of instruction boundaries.

So a specific set of instruction is applied for each processor, where programs of machine language of

one processor will not execute on different processor.

Recommendation

I recommend RISC over CISC because of the following reasons; first, the simple sets of instruction of RISC

processor makes it 2-4 times faster than CISC processor. Secondly, RISC architecture uses less memory

space due to it reduced sets of instruction and therefore can accommodate more functions like memory

management unit. And lastly, it has shorter structure cycle due to the simple instruction set it possesses.

As such, it can utilize other developments of technology and therefore increasing it performance

between generations.

Paraphrase This Document

Need a fresh take? Get an instant paraphrase of this document with our AI Paraphraser

Running head: CISC and RISC Architecture 8

References

[1] L. B. Das, The x86 microprocessors : architecture and programming (8086 to Pentium), New Delhi,

India: Dorling Kindersley, 2010.

[2] A. P. Godse and D. A. Godse, Computer organization and architecture, Pune, India: Technical

Publications, 2010.

[3] K. Hwang and N. Jotwani, Advanced computer architecture : parallelism, scalability,

programmability, New Delhi, India: McGraw-Hill, 2011.

[4] E. Upton, J. Duntemann, R. Roberts, T. Mamtora and B. Everard, Learning computer architecture

with Raspberry Pi, Indianapolis, IN: Wiley, 2016.

[5] L. Null and J. Lobur, The essentials of computer organization and architecture, fourth edition,

Burlington, MA: Jones & Bartlett Learning, 2015.

References

[1] L. B. Das, The x86 microprocessors : architecture and programming (8086 to Pentium), New Delhi,

India: Dorling Kindersley, 2010.

[2] A. P. Godse and D. A. Godse, Computer organization and architecture, Pune, India: Technical

Publications, 2010.

[3] K. Hwang and N. Jotwani, Advanced computer architecture : parallelism, scalability,

programmability, New Delhi, India: McGraw-Hill, 2011.

[4] E. Upton, J. Duntemann, R. Roberts, T. Mamtora and B. Everard, Learning computer architecture

with Raspberry Pi, Indianapolis, IN: Wiley, 2016.

[5] L. Null and J. Lobur, The essentials of computer organization and architecture, fourth edition,

Burlington, MA: Jones & Bartlett Learning, 2015.

1 out of 8

Related Documents

Your All-in-One AI-Powered Toolkit for Academic Success.

+13062052269

info@desklib.com

Available 24*7 on WhatsApp / Email

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)

Unlock your academic potential

Copyright © 2020–2026 A2Z Services. All Rights Reserved. Developed and managed by ZUCOL.