COMP 300 Spring 2021 Midterm Exam: Data Path Design and RTL Programs

VerifiedAdded on 2021/07/07

|17

|2233

|257

Homework Assignment

AI Summary

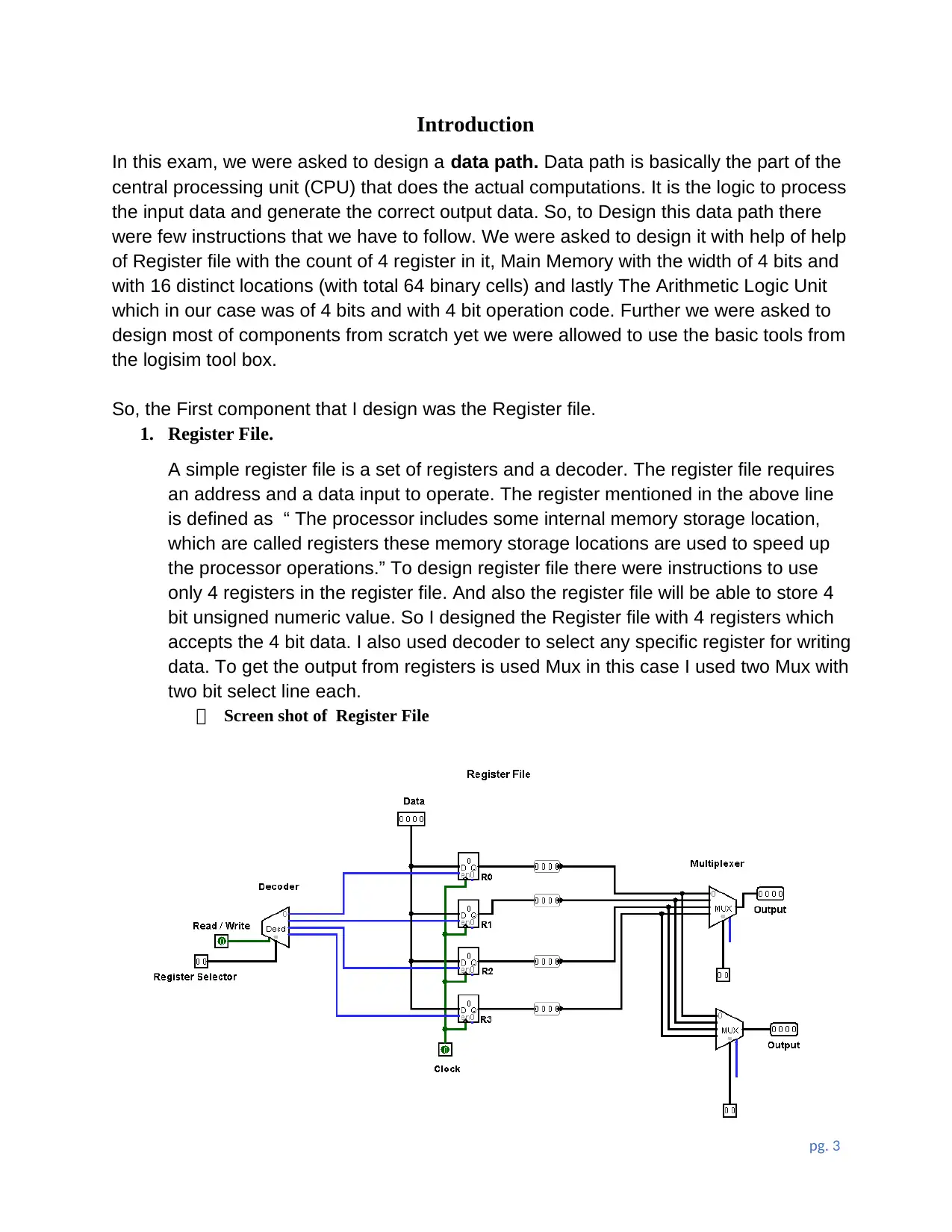

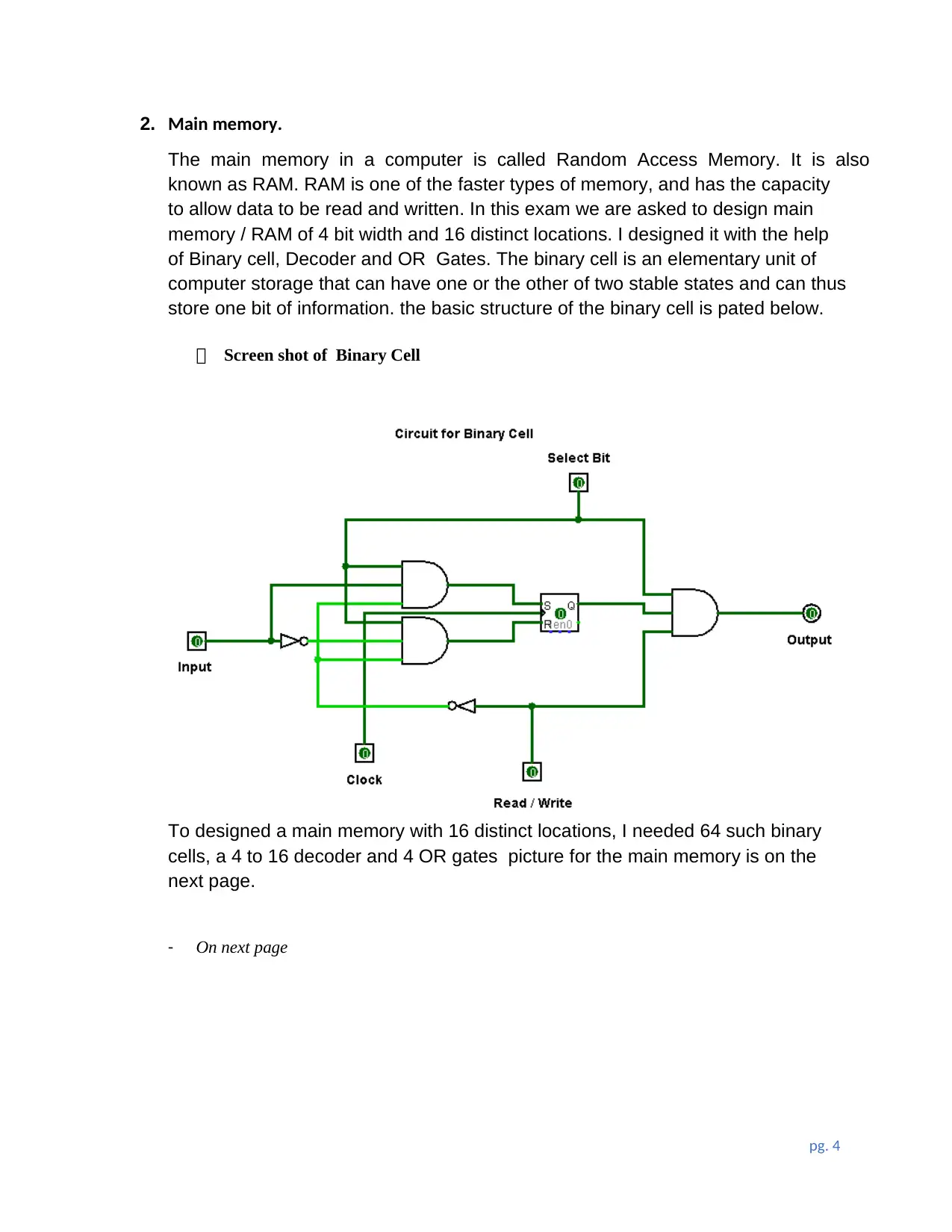

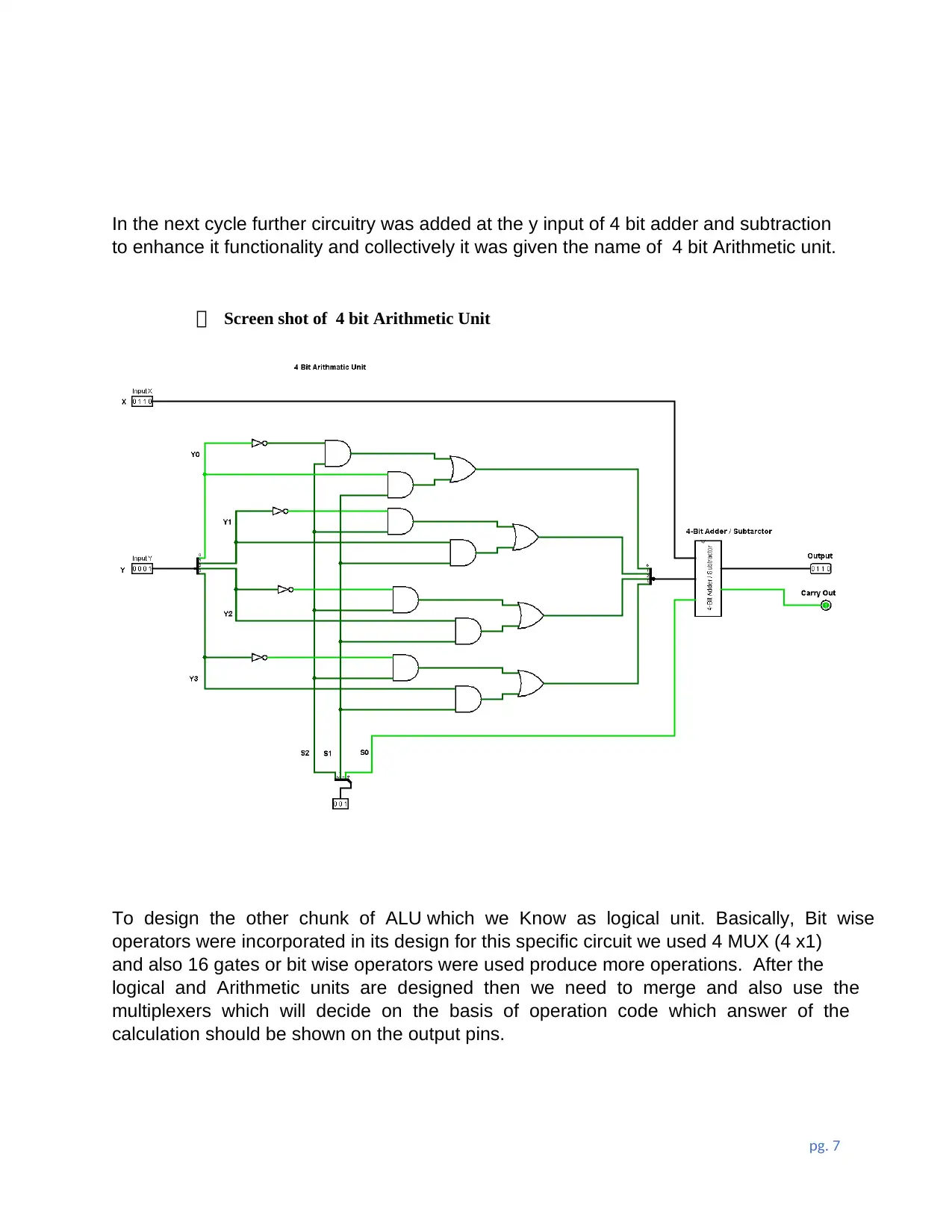

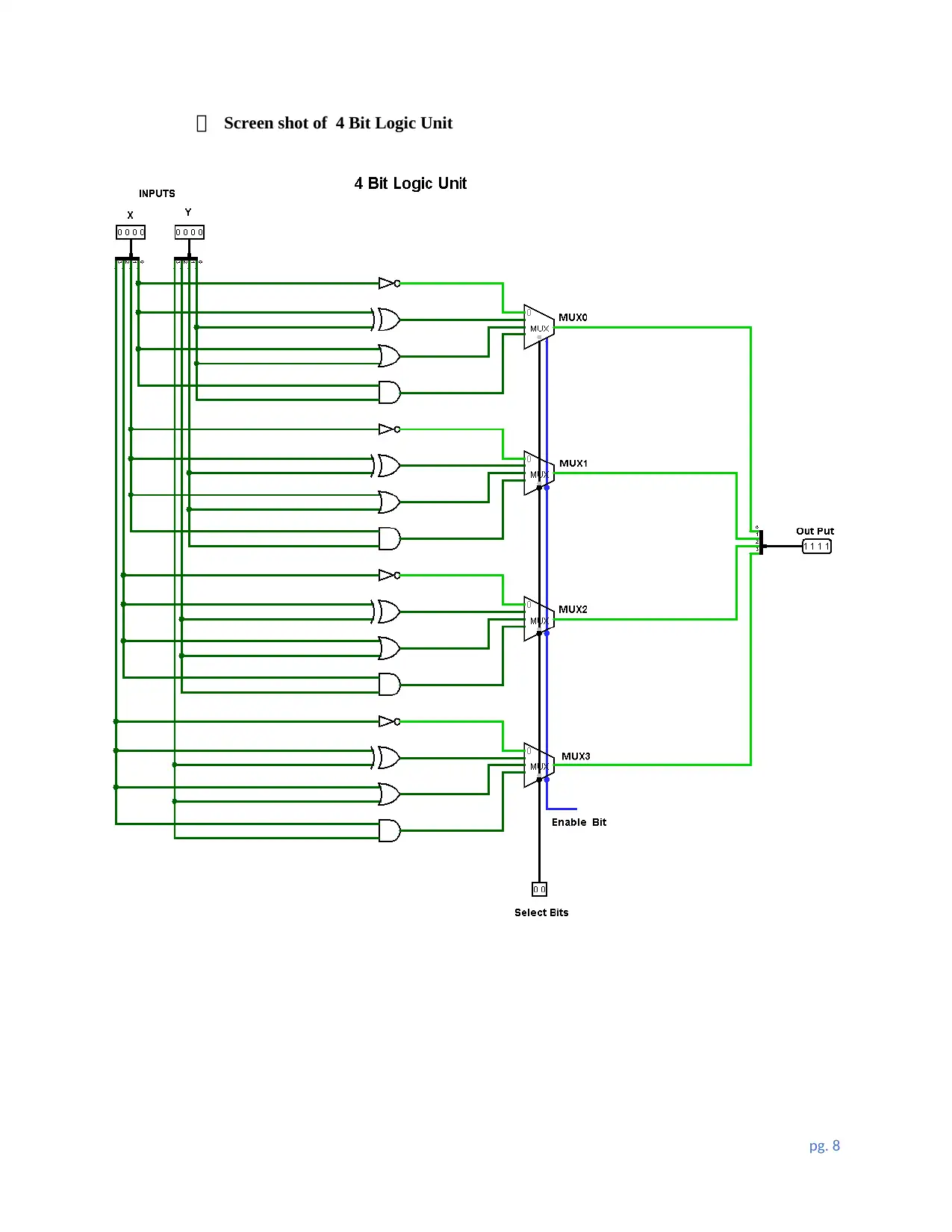

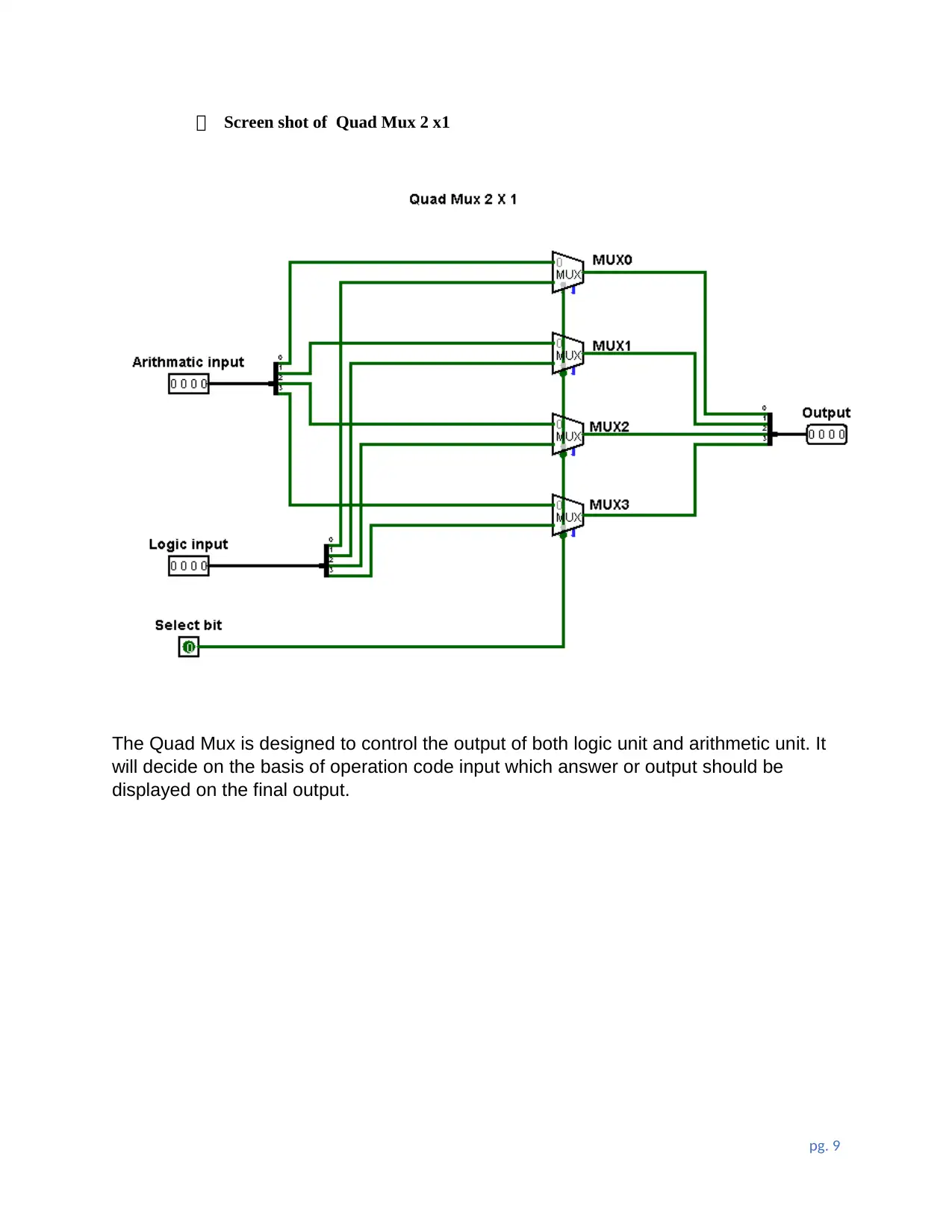

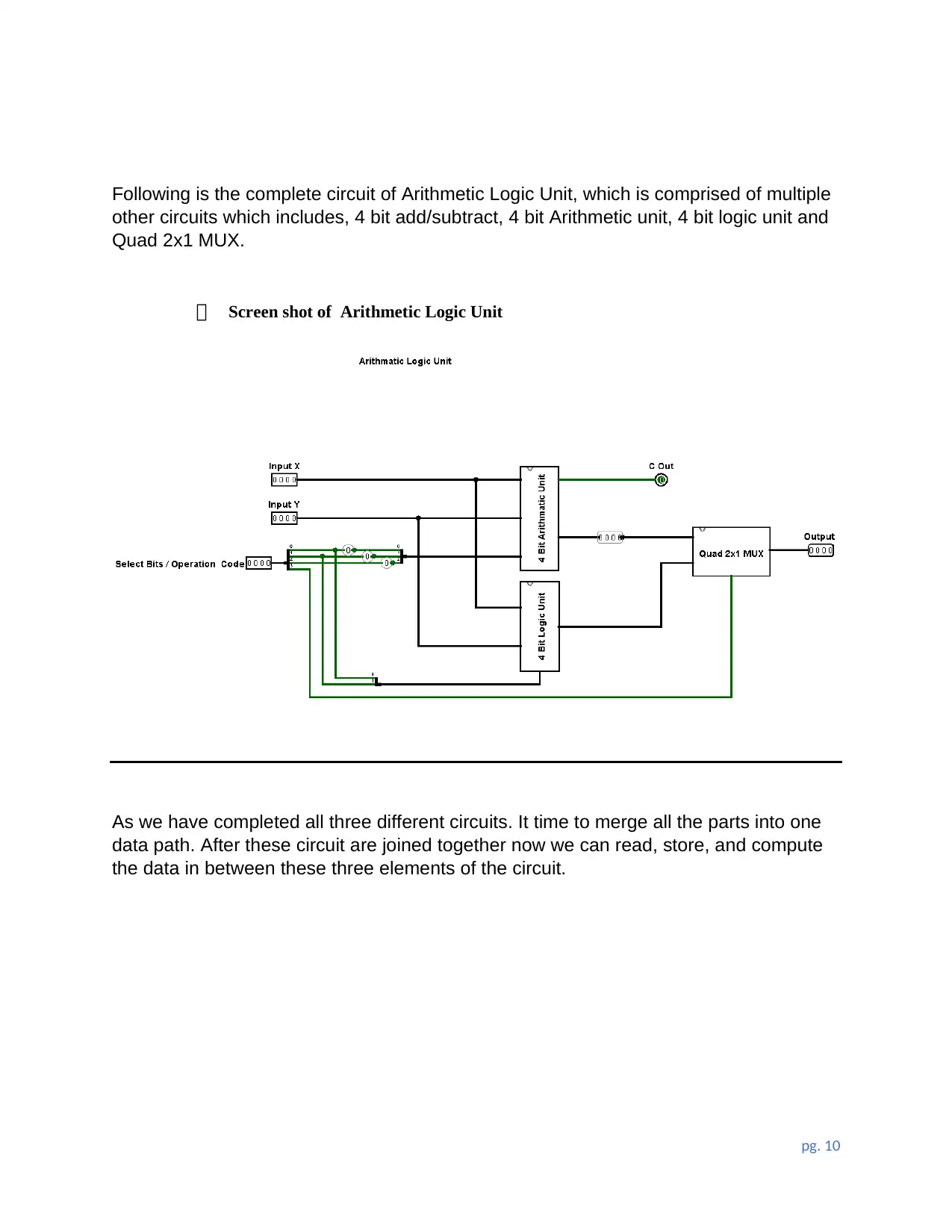

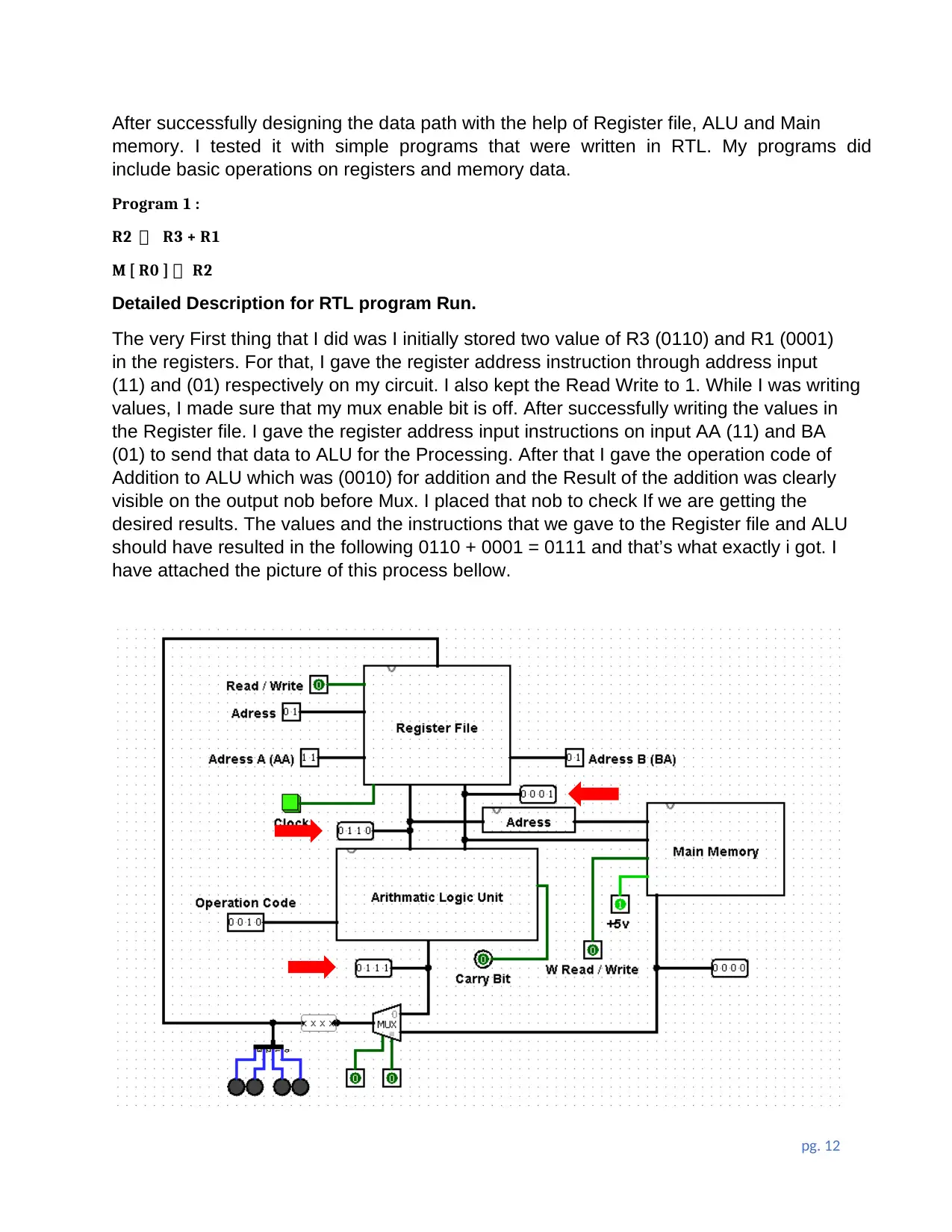

This document presents a solution to a midterm exam assignment from a Chartered University's COMP 300 course, focusing on data path design. The assignment required designing a data path consisting of a register file (4 registers), a 4-bit main memory (16 locations), and a 4-bit ALU with a 4-bit operation code. The solution details the design of each component from scratch, including the register file using decoders and multiplexers, the main memory using binary cells and decoders, and the ALU comprising arithmetic and logic units. The arithmetic unit includes a 4-bit adder/subtracter and a 4-bit arithmetic unit, while the logic unit incorporates bitwise operators. The solution merges these units and utilizes multiplexers to control the output based on the operation code. The student then tested the designed data path with two RTL programs, demonstrating operations on registers and memory data, and explaining the control signals used during the program runs. The document includes screenshots of each component and the RTL program runs, illustrating the step-by-step process of data storage, retrieval, and computation within the data path. The document also includes the components used such as decoders, registers, multiplexers, adders, and logic gates.

1 out of 17

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)