Computer Architecture Homework: Binary to Floating-Point Conversion

VerifiedAdded on 2020/03/02

|4

|724

|181

Homework Assignment

AI Summary

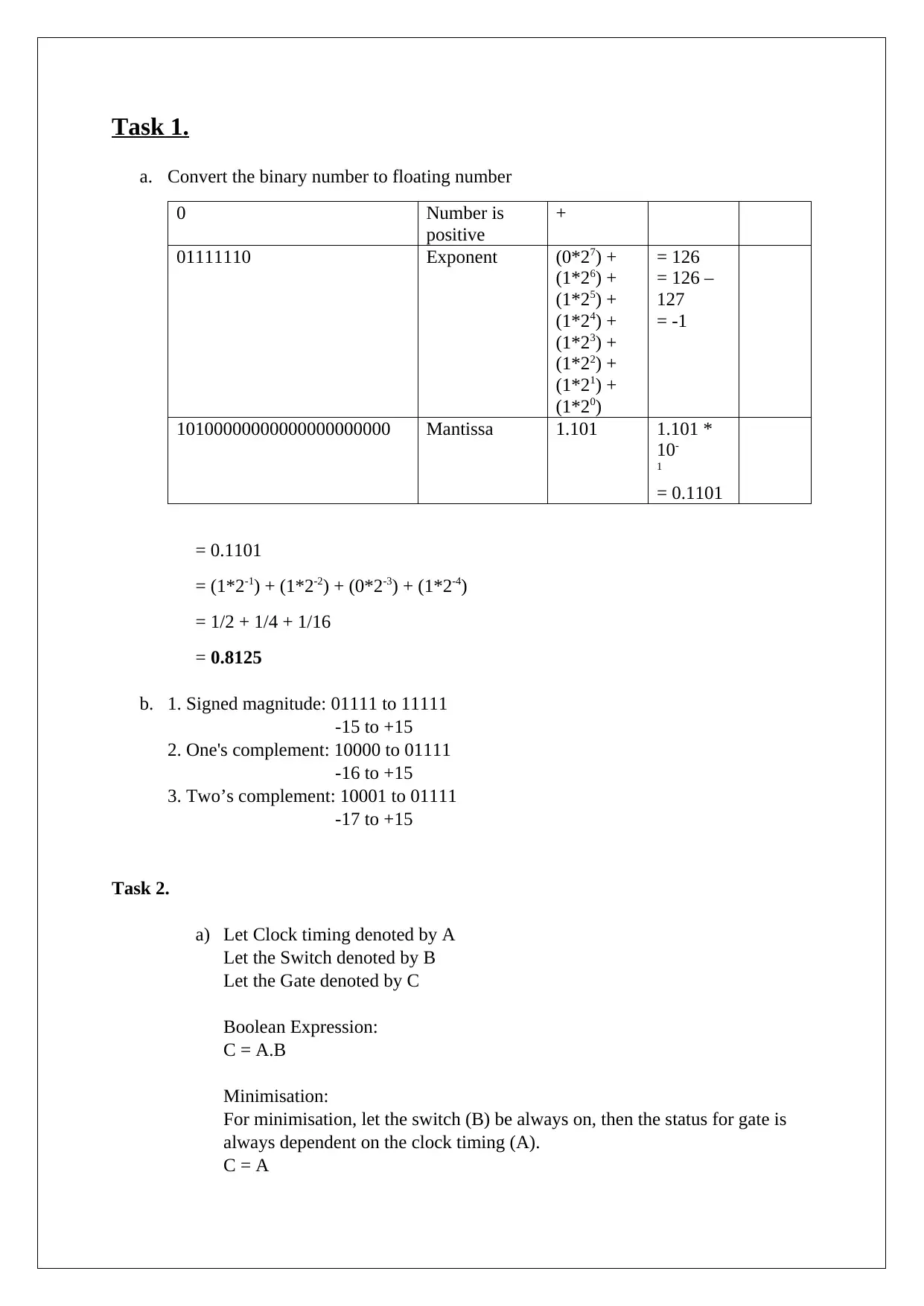

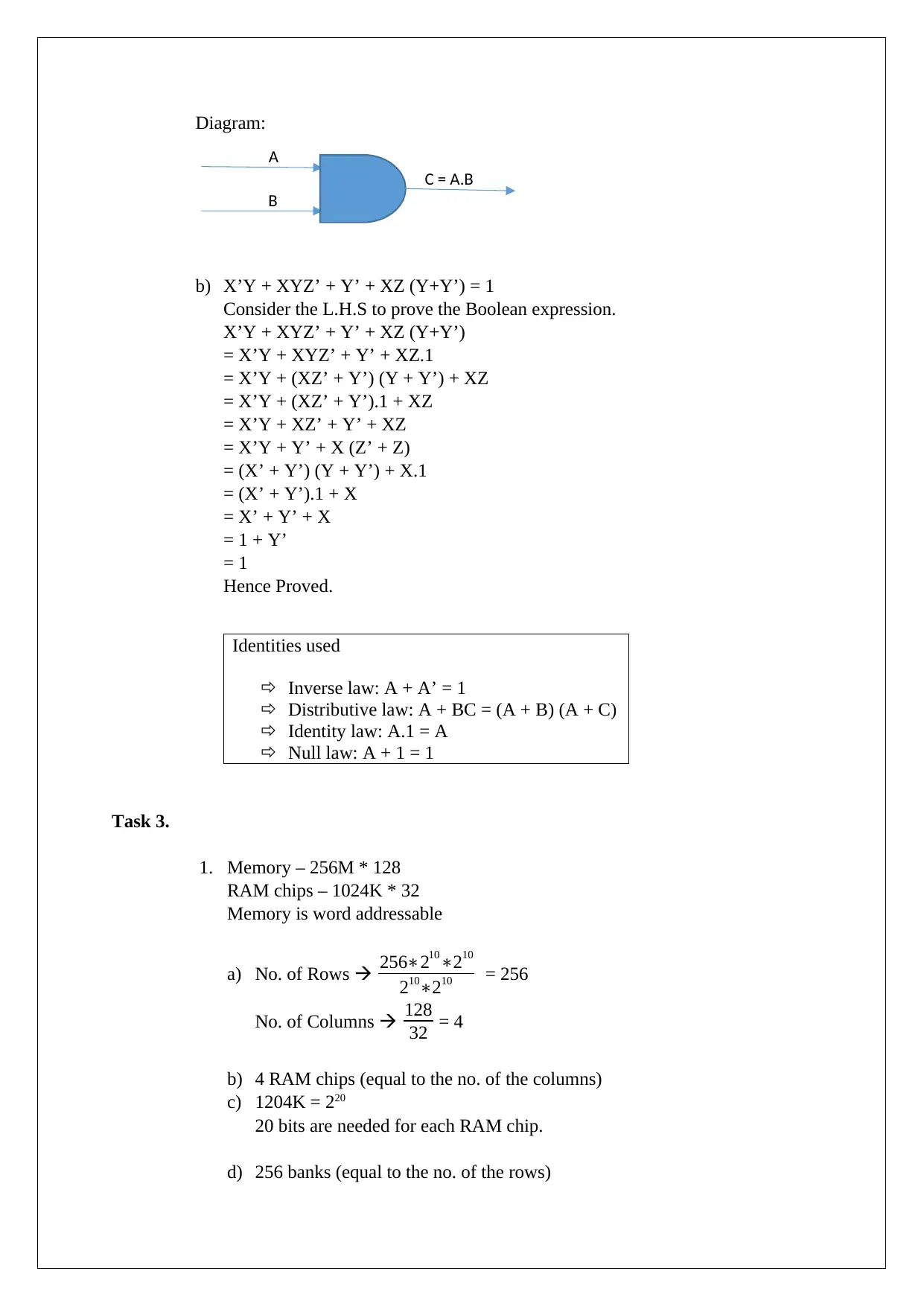

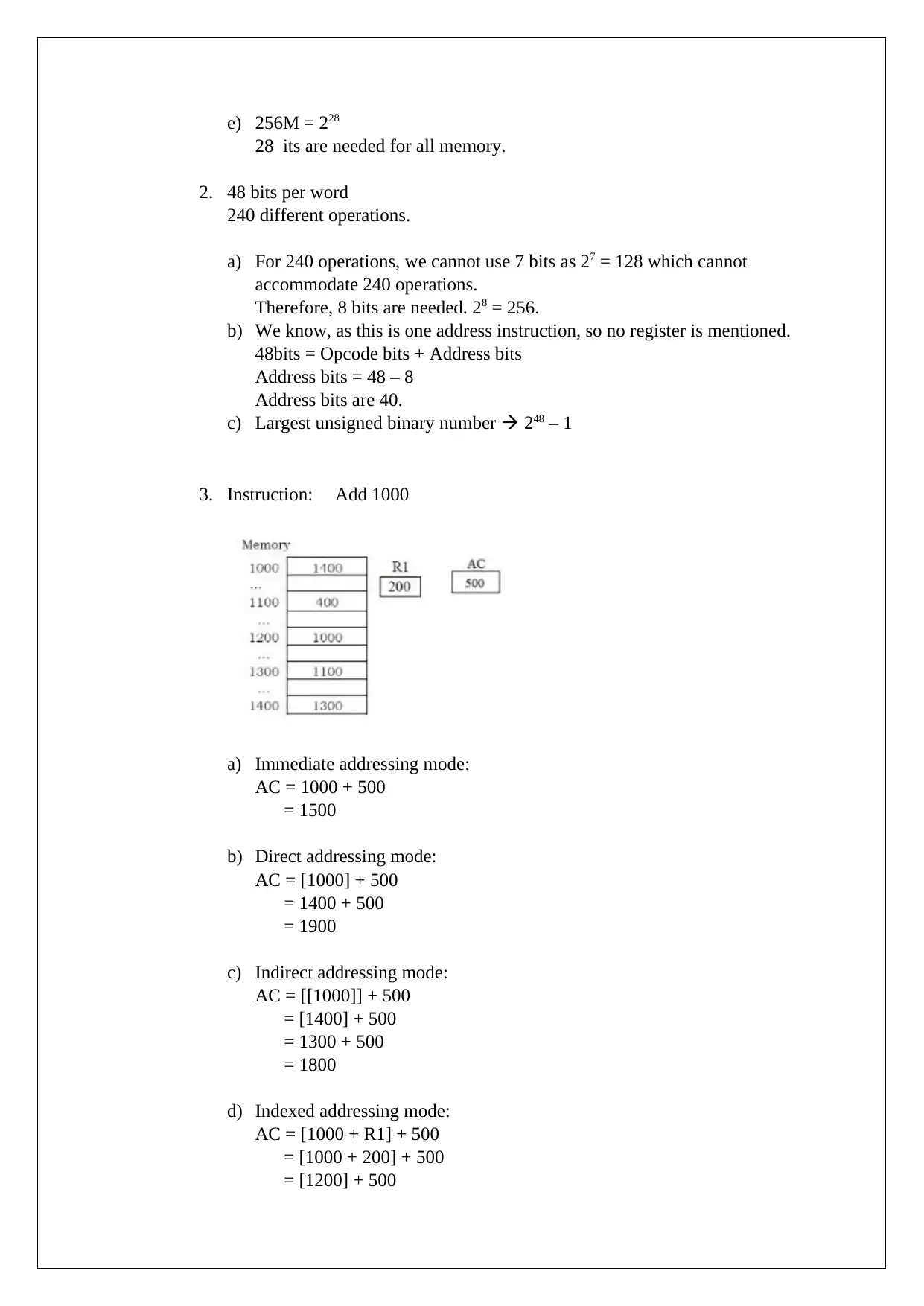

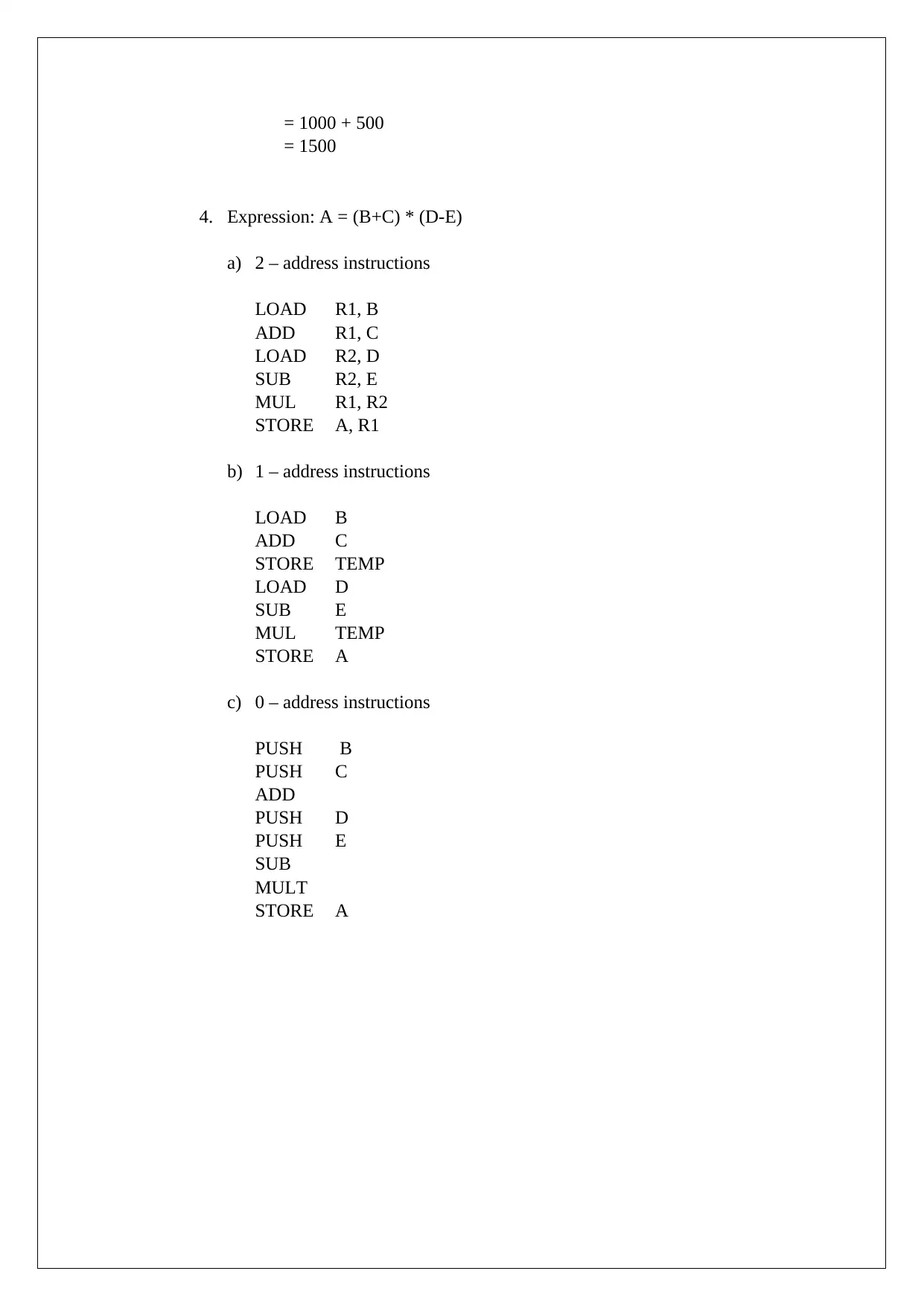

This assignment solution addresses three key areas within computer architecture. Task 1 involves converting a binary number to its floating-point representation, detailing the process of determining the sign, exponent, and mantissa, ultimately arriving at the decimal equivalent. Task 2 focuses on Boolean algebra, presenting a Boolean expression, its minimization, and a corresponding diagram, along with a proof using Boolean identities. The final task, Task 3, delves into memory organization, calculating the number of RAM chips required given specifications, determining the number of bits needed for various memory operations, and demonstrating the execution of instructions using different addressing modes (immediate, direct, indirect, and indexed), including the conversion of an expression into different instruction formats (two-address, one-address, and zero-address).

1 out of 4

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)