Computer Architecture: CPU Cache, Memory Design, and TLB Assignment

VerifiedAdded on 2022/10/19

|4

|299

|39

Homework Assignment

AI Summary

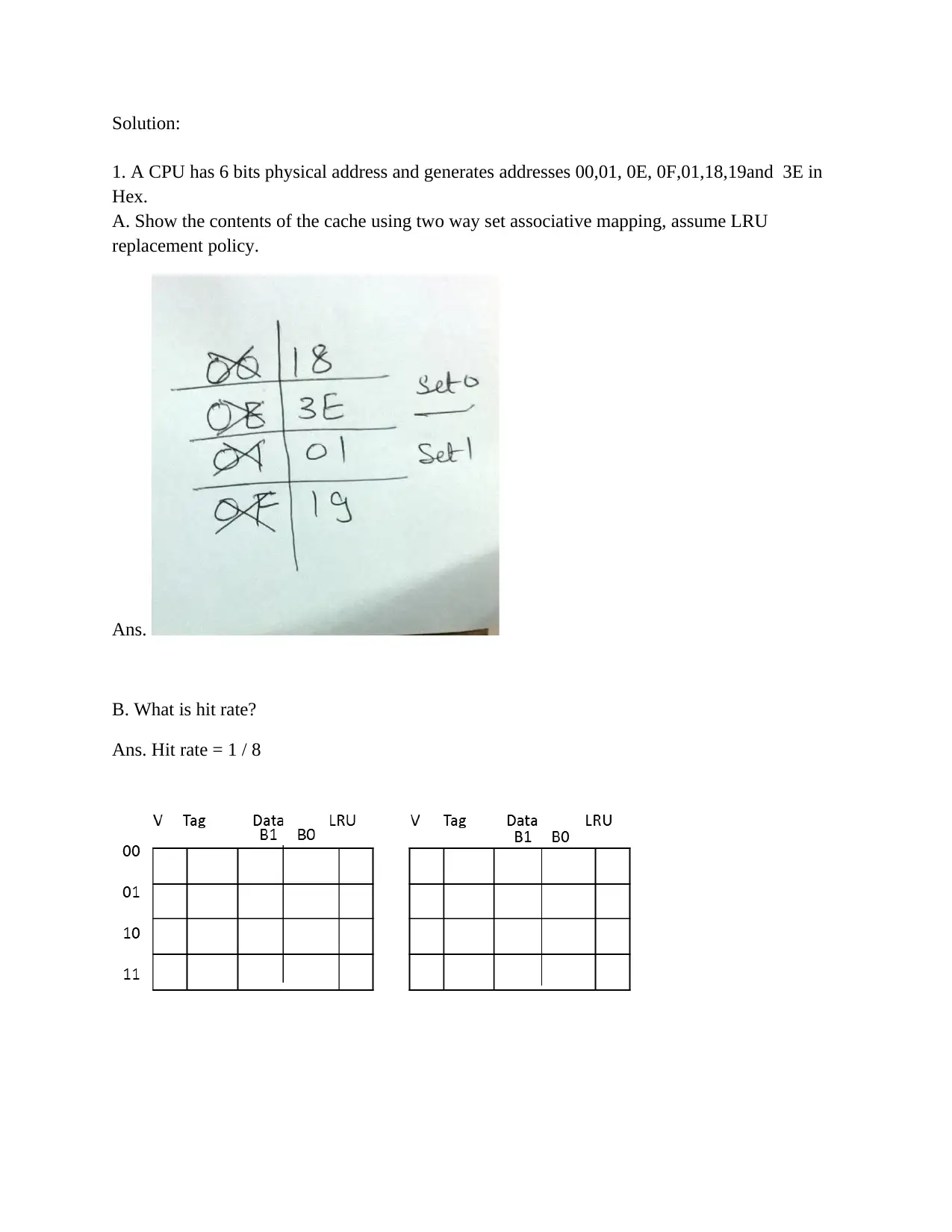

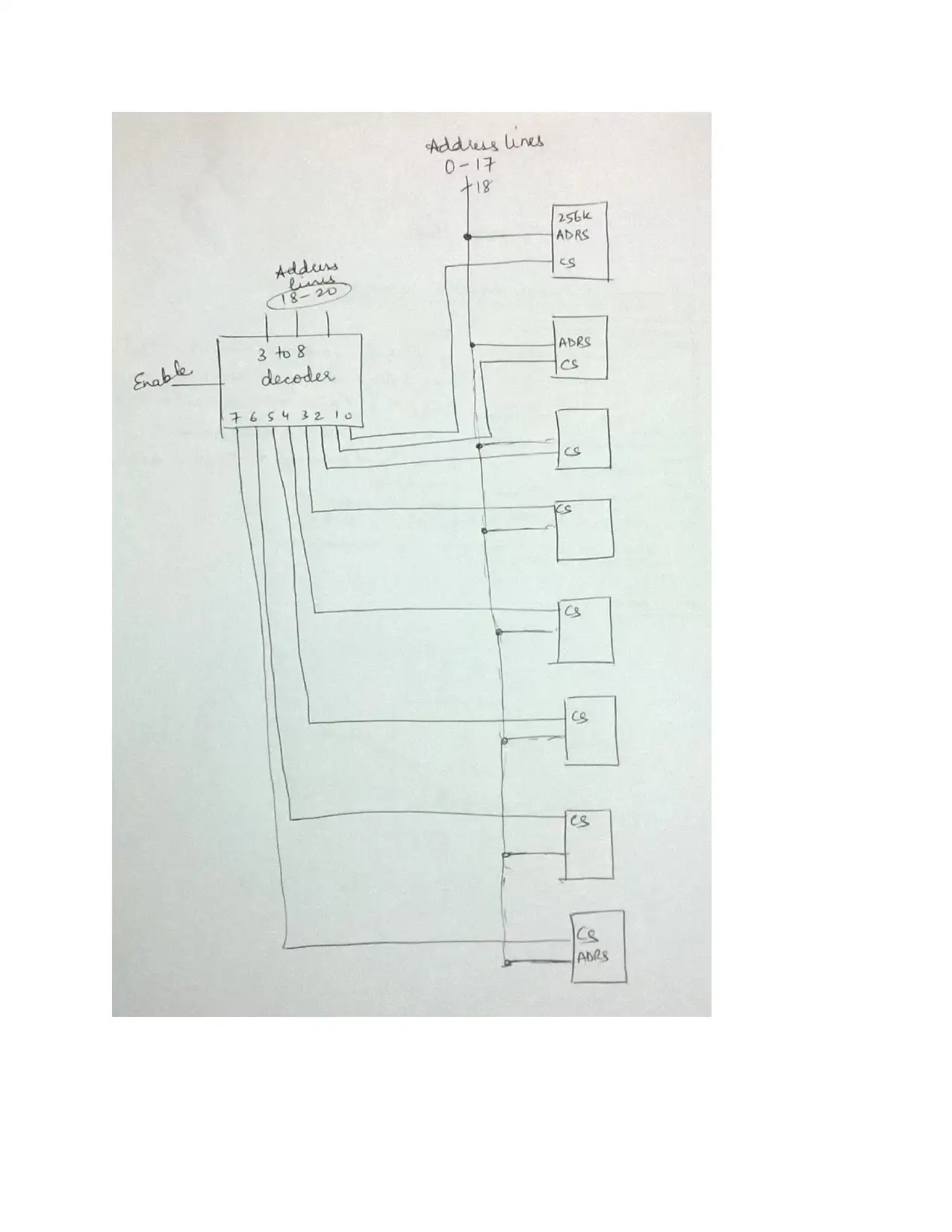

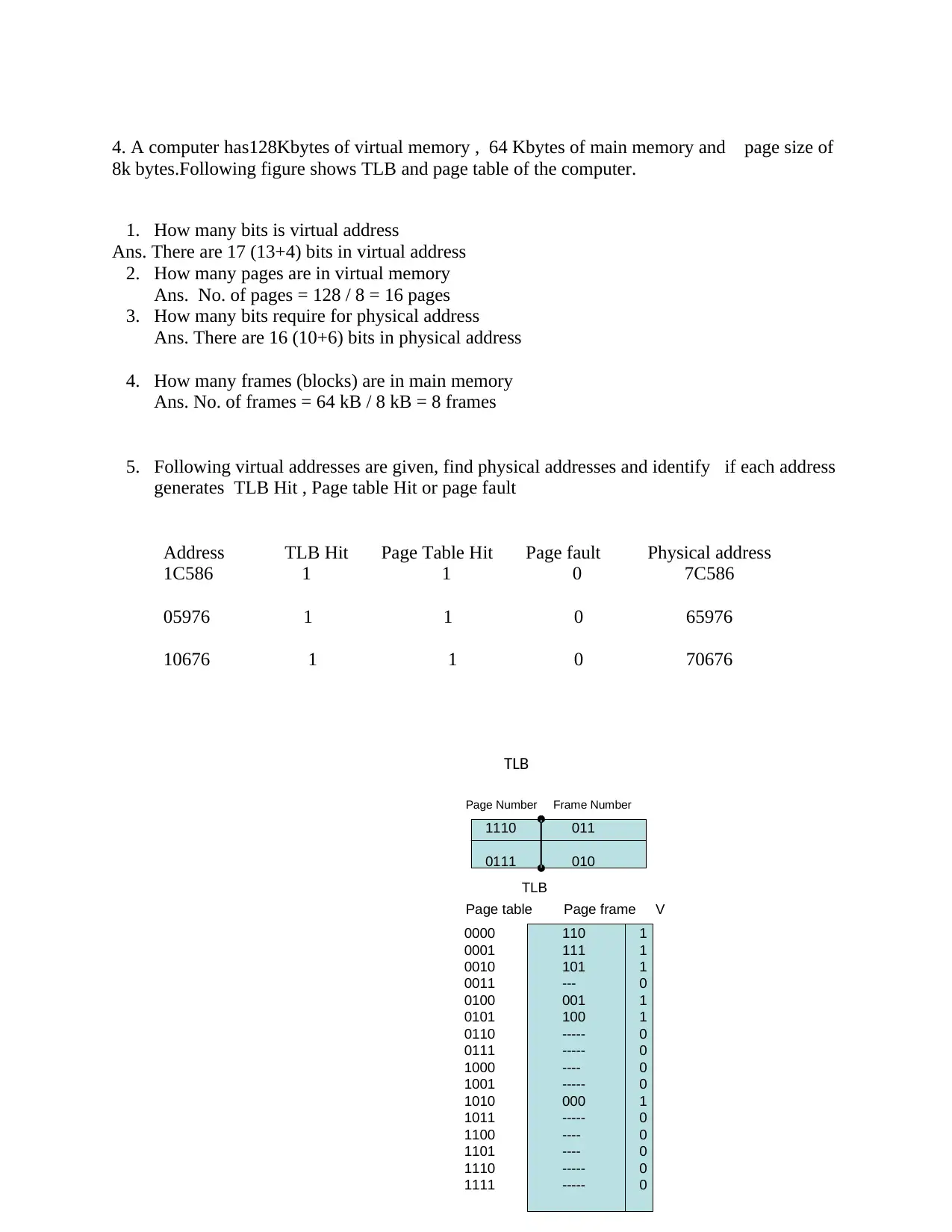

This assignment delves into several key aspects of computer architecture. It begins with a problem involving a CPU's physical address space and requires the student to demonstrate the contents of the cache using a two-way set associative mapping with an LRU replacement policy and determine the hit rate. Next, the assignment involves designing a memory module using specific memory ICs, calculating the number of ICs needed, the number of address lines, and the size of the decoder, culminating in a memory diagram. Finally, the assignment presents a scenario involving virtual memory, requiring the student to determine the number of bits in the virtual address, the number of pages, the number of bits required for the physical address, and the number of frames. The student is then tasked with calculating physical addresses, and identifying whether each address generates a TLB hit, a page table hit, or a page fault.

1 out of 4

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)