Computer Architecture and Organization I CMPE 263 Homework 1

VerifiedAdded on 2022/08/19

|10

|899

|31

Homework Assignment

AI Summary

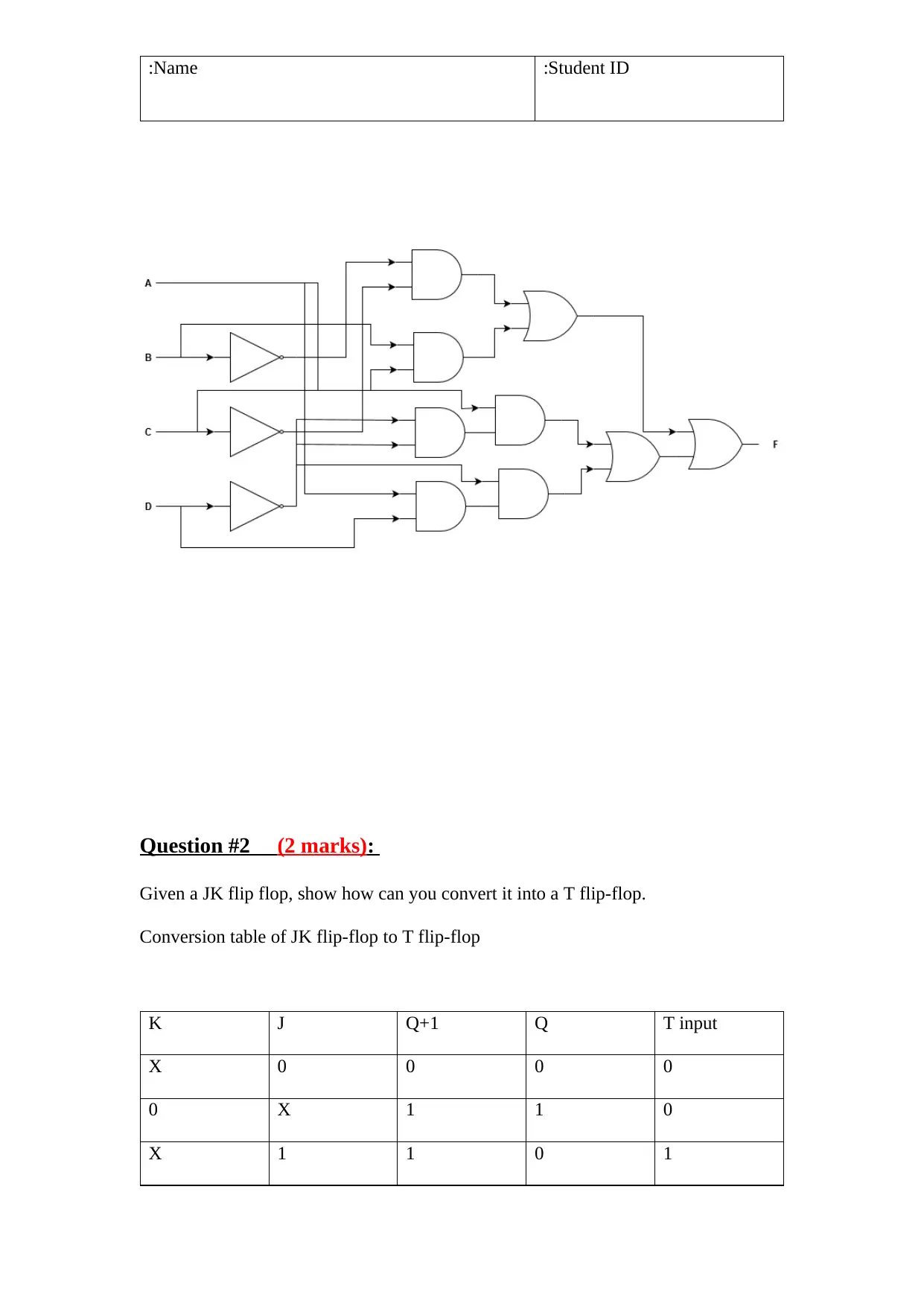

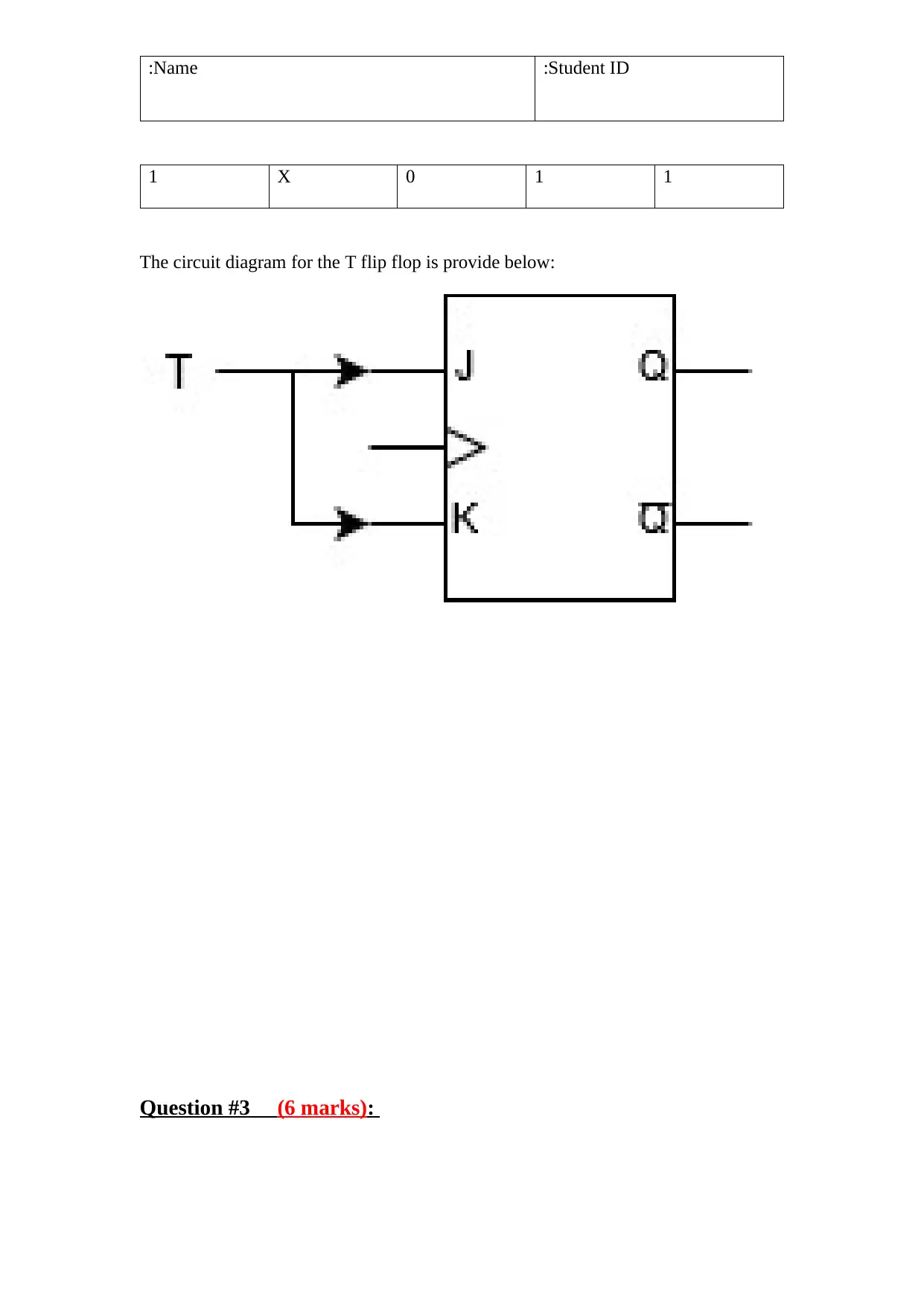

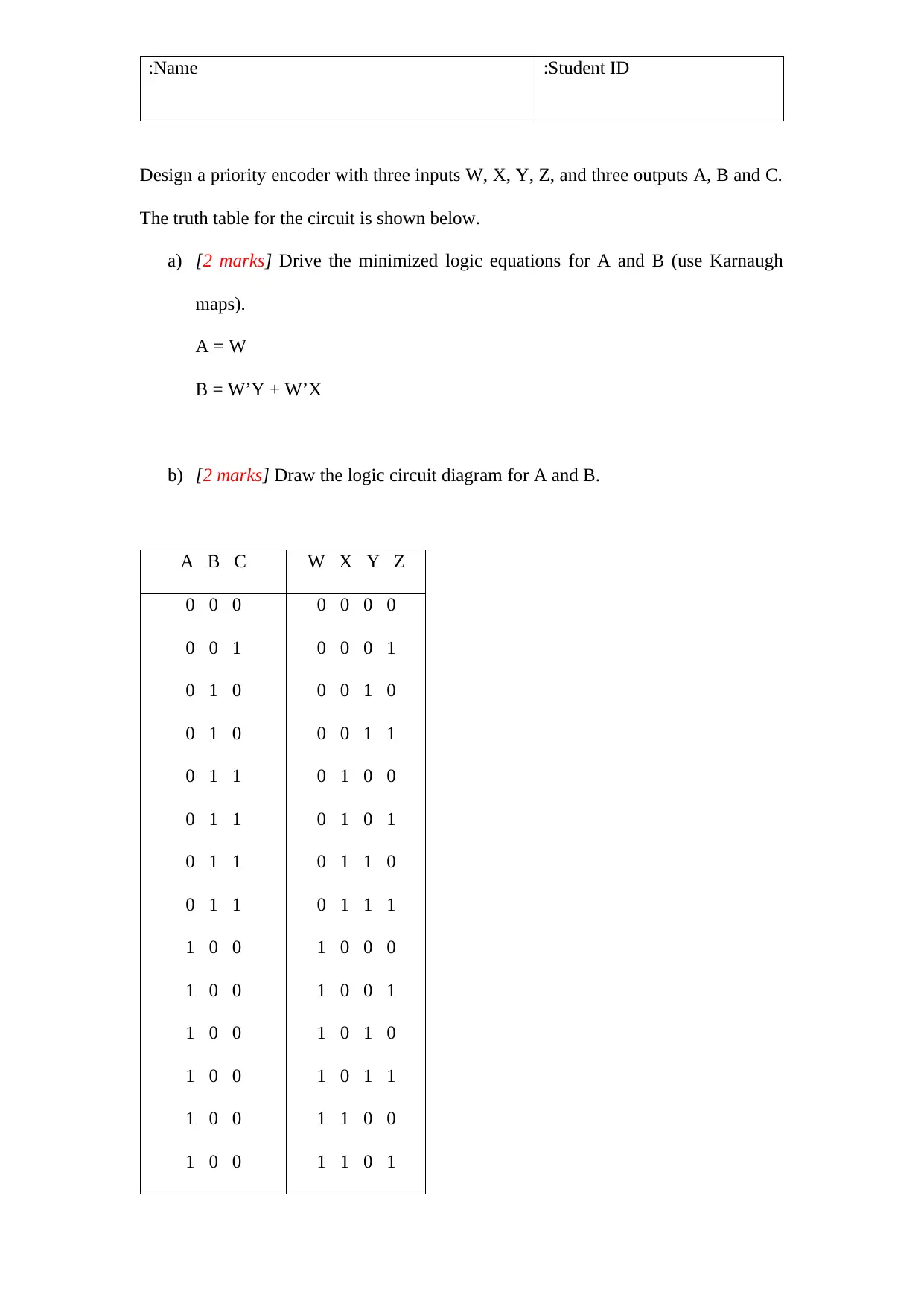

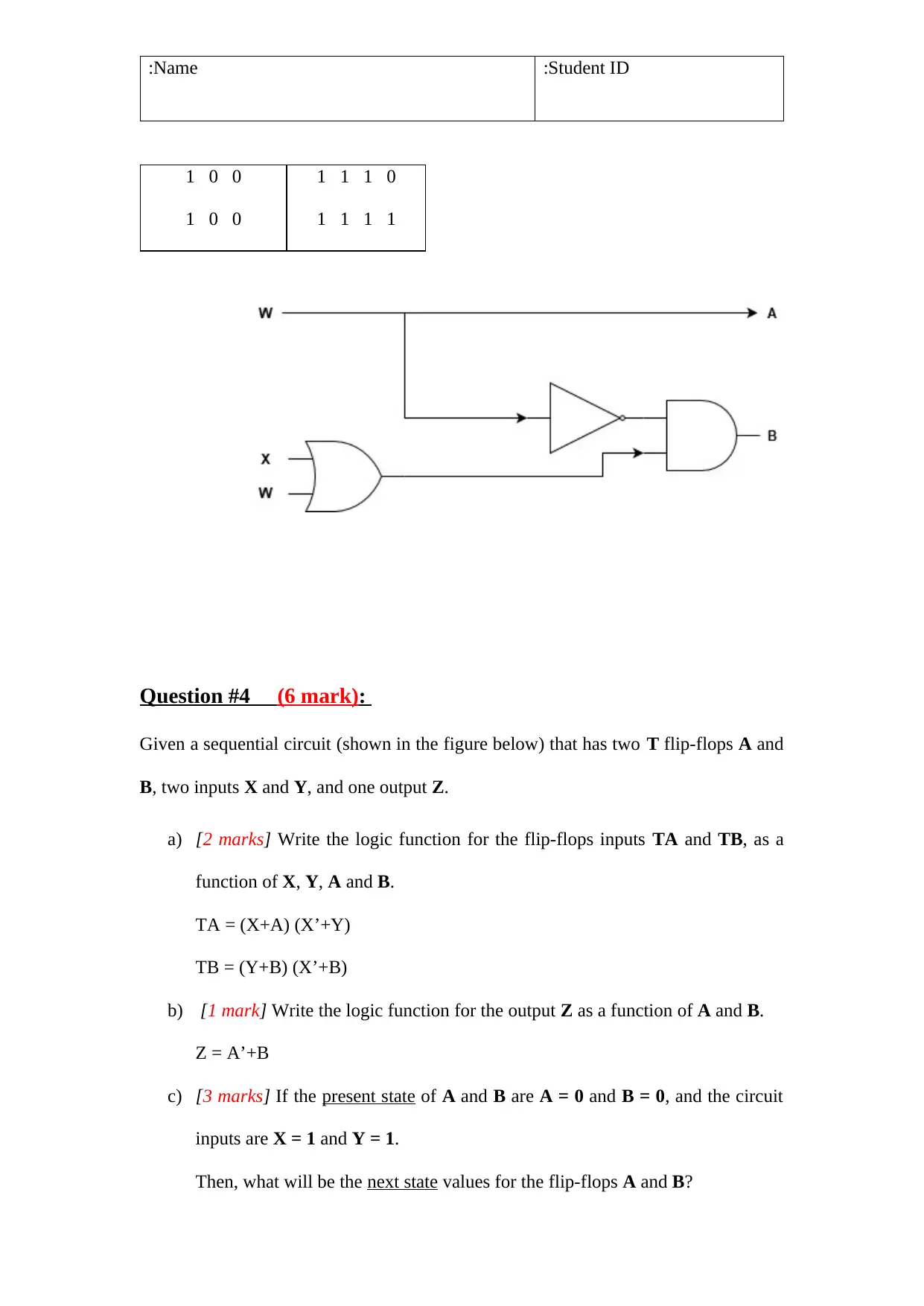

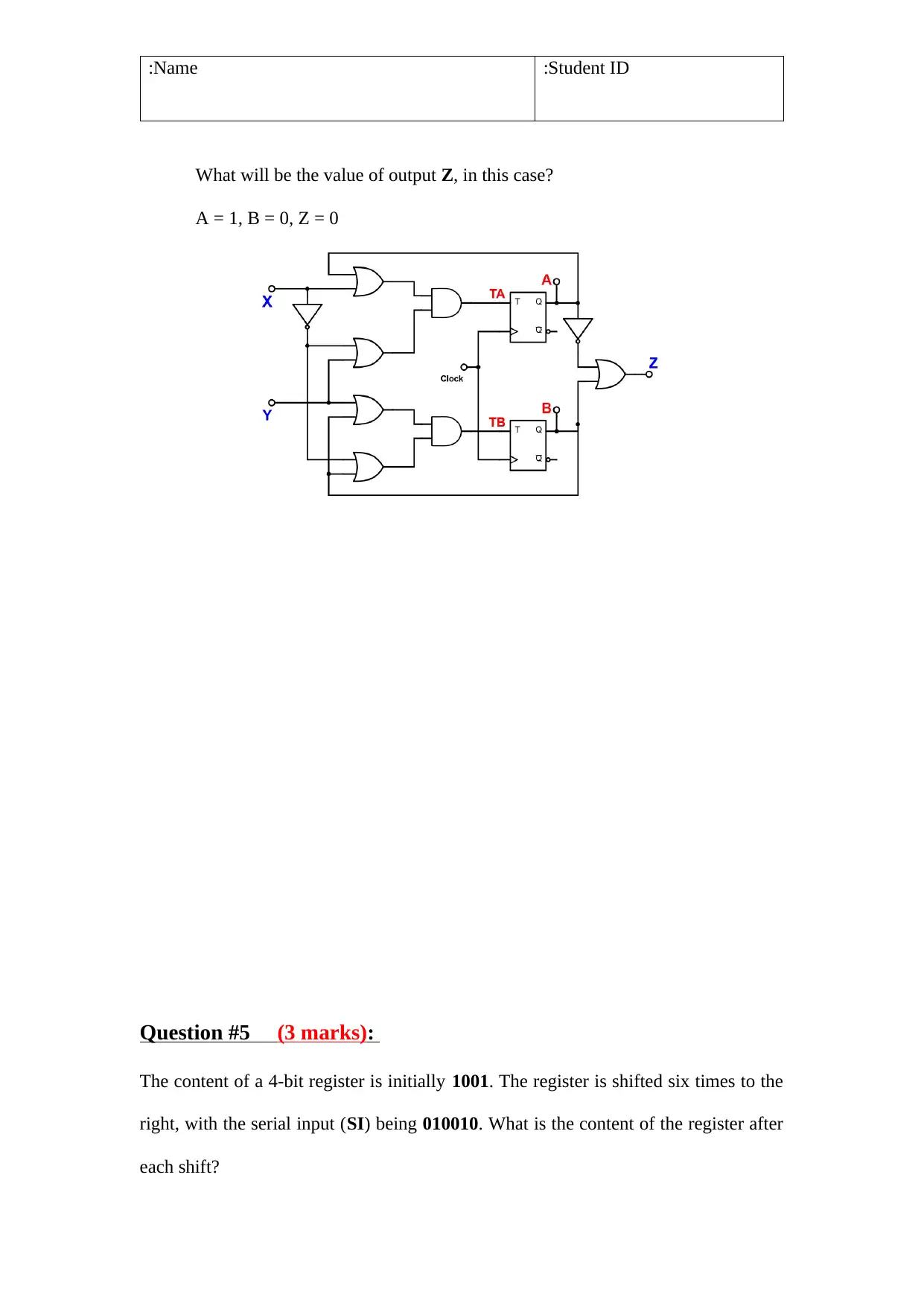

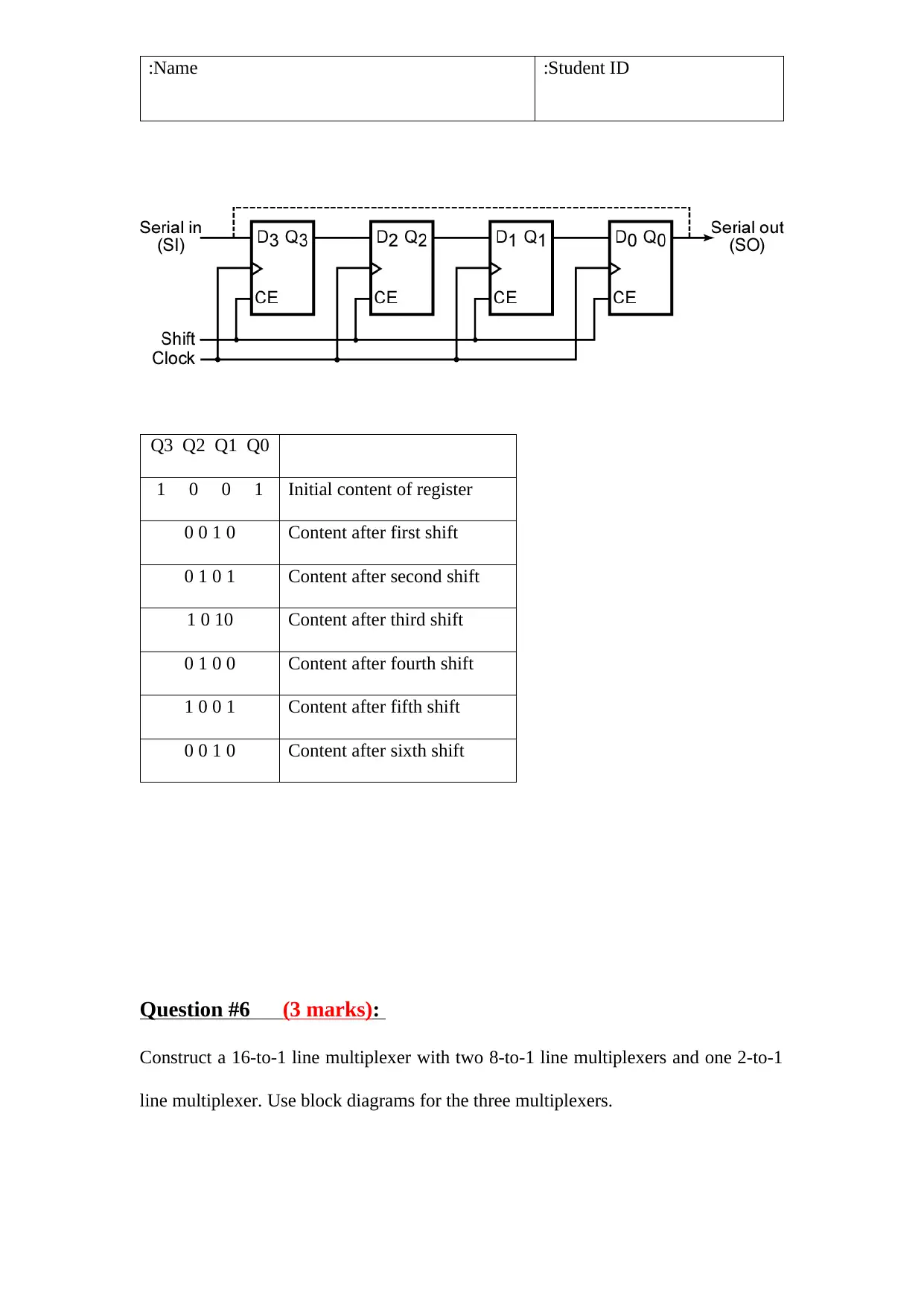

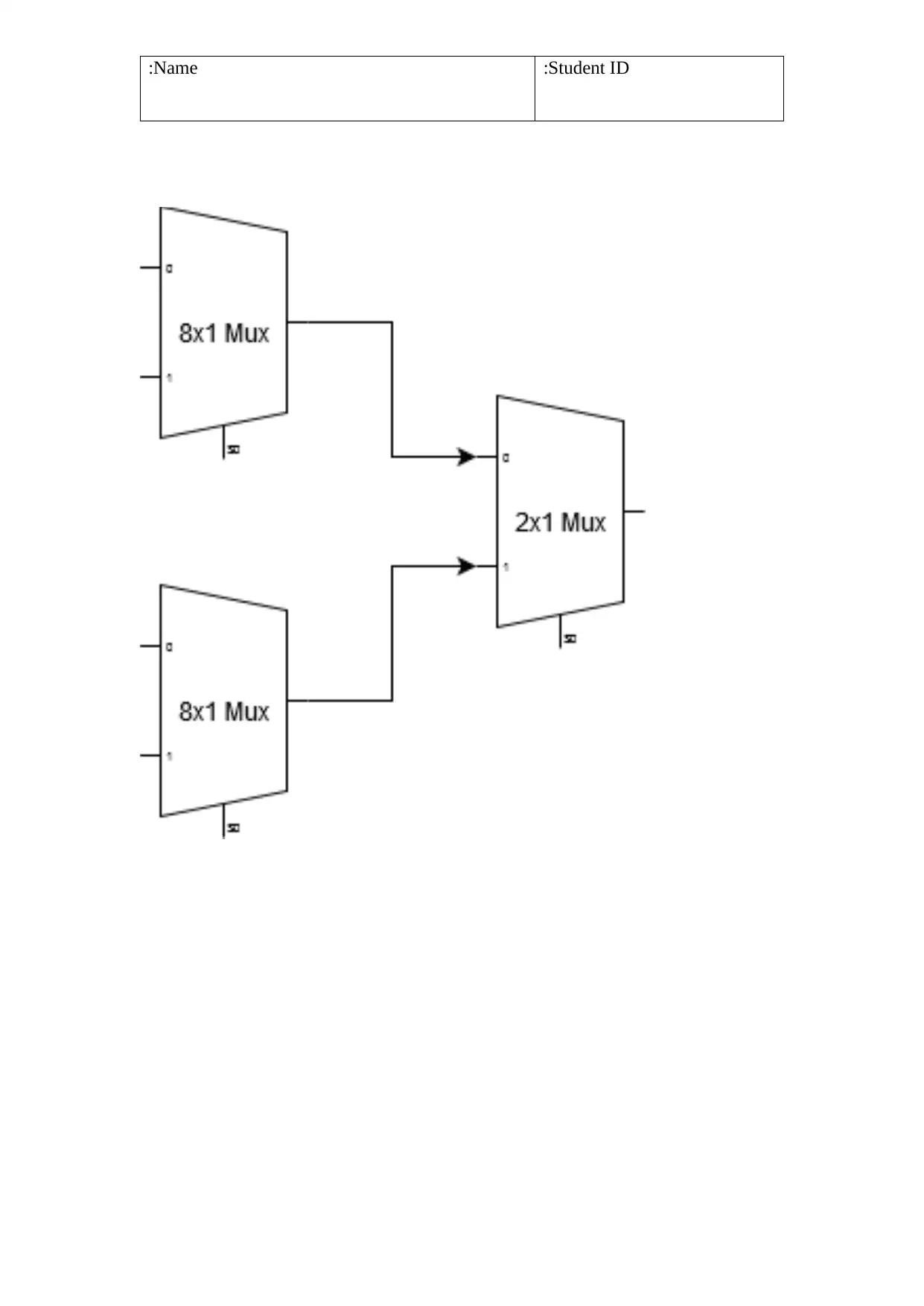

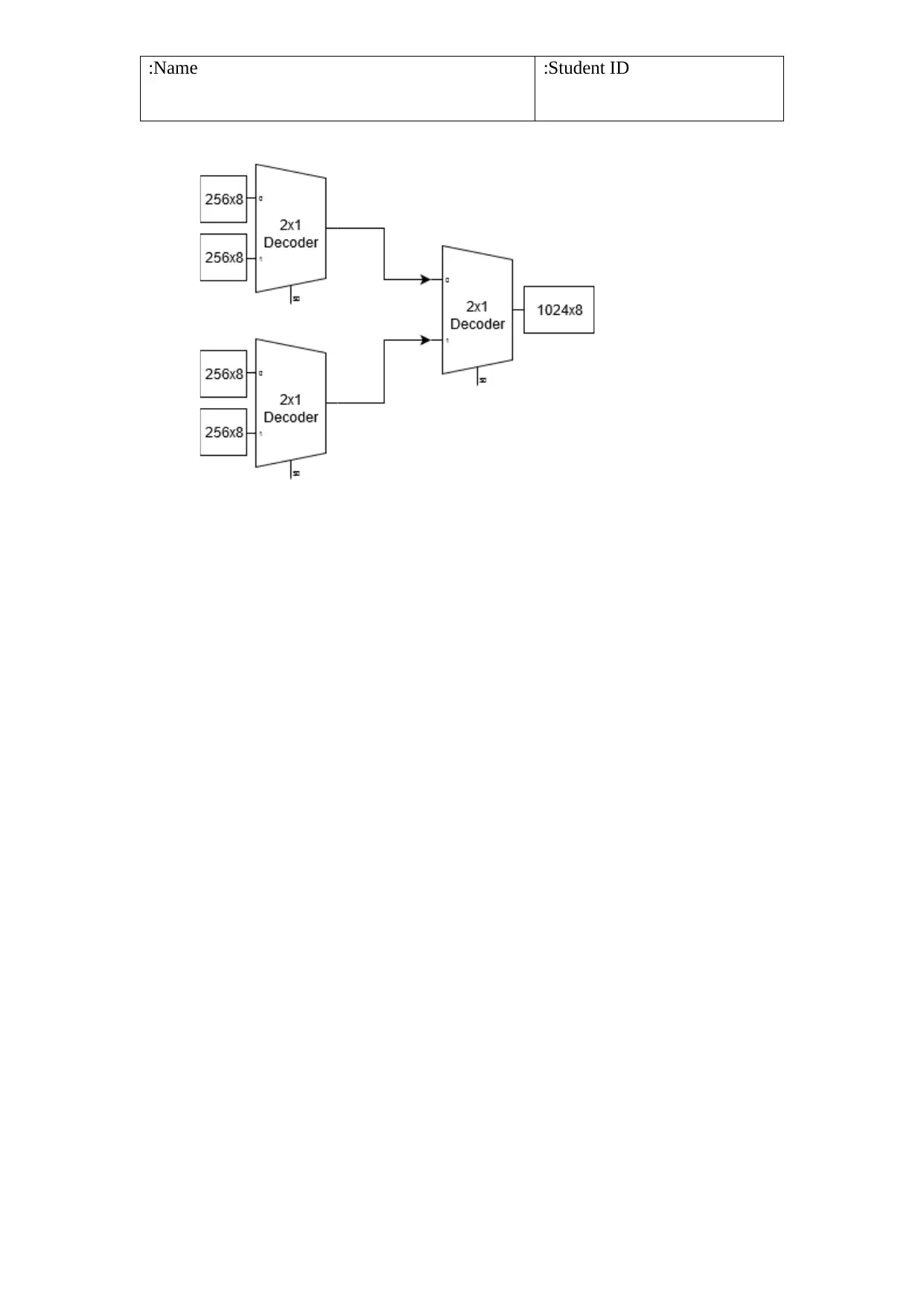

This document provides a comprehensive solution to Homework 1 for the Computer Architecture and Organization I (CMPE 263) course. The assignment covers fundamental concepts in digital logic and circuit design. The solution includes the simplification of Boolean functions using Karnaugh maps and the design of logic diagrams with AND-OR gates. It also details the conversion of a JK flip-flop to a T flip-flop, and the design of a priority encoder. The solution further addresses sequential circuits, including writing logic functions and determining the next state of flip-flops. Additionally, the assignment involves problems related to shift registers, multiplexer construction, and ROM memory design, including calculating the number of chips, address lines, and decoder size required for memory implementation.

1 out of 10

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)