Computer Organization and Architecture: Logic Circuit Analysis Report

VerifiedAdded on 2022/08/21

|4

|725

|15

Report

AI Summary

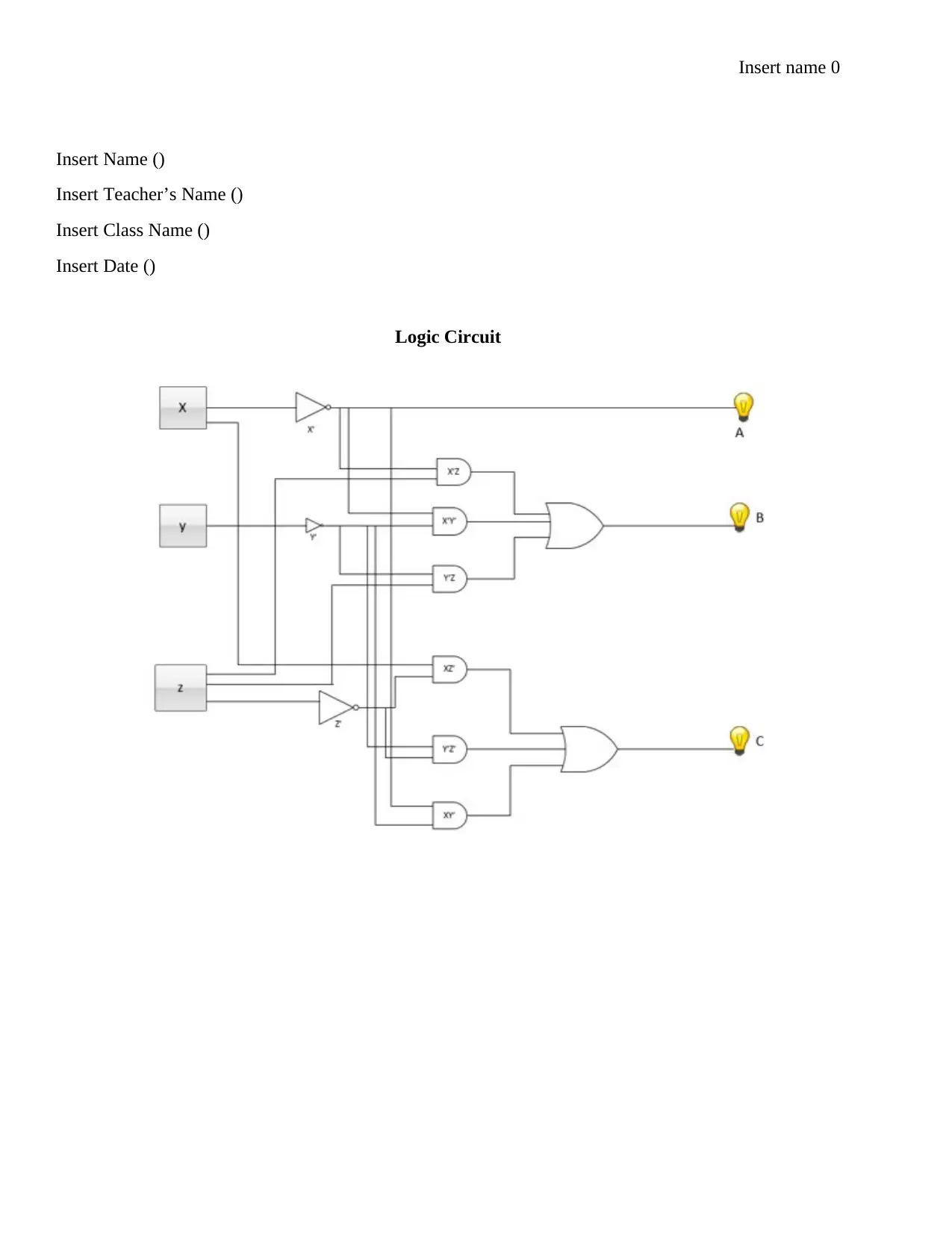

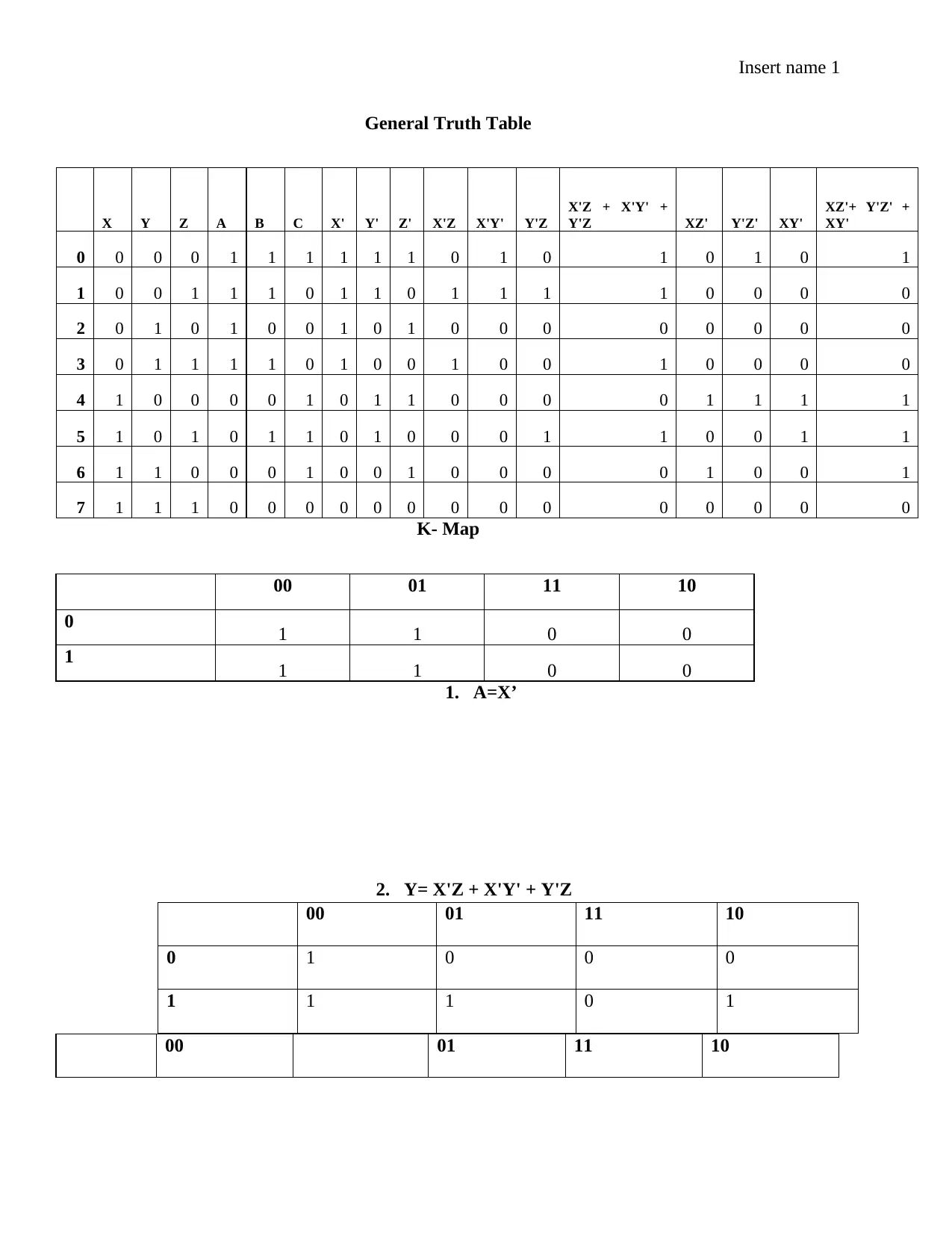

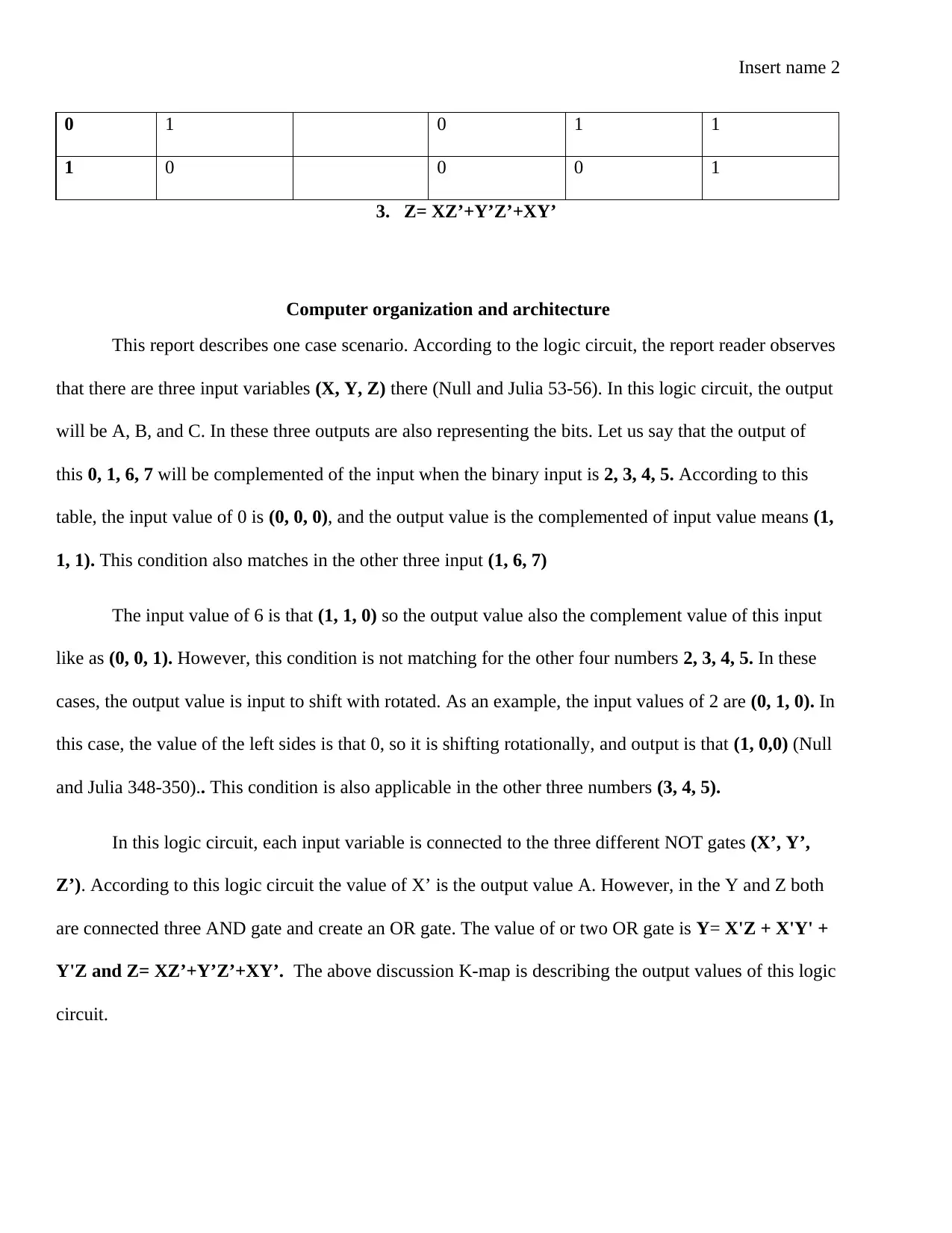

This report provides an analysis of a logic circuit within the context of computer organization and architecture. It examines a circuit with three input variables (X, Y, Z) and three output variables (A, B, C). The report details the relationship between inputs and outputs, highlighting how specific input combinations result in complemented or rotated outputs based on the provided truth table. The analysis includes the application of NOT gates, AND gates, and OR gates to determine the output values. The report also references K-maps to represent the output values of the logic circuit. The report refers to a source to support the analysis of the logic circuit.

1 out of 4

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)