Computer Organization and Architecture ITC 544 Assignment Solution

VerifiedAdded on 2019/10/30

|6

|494

|315

Homework Assignment

AI Summary

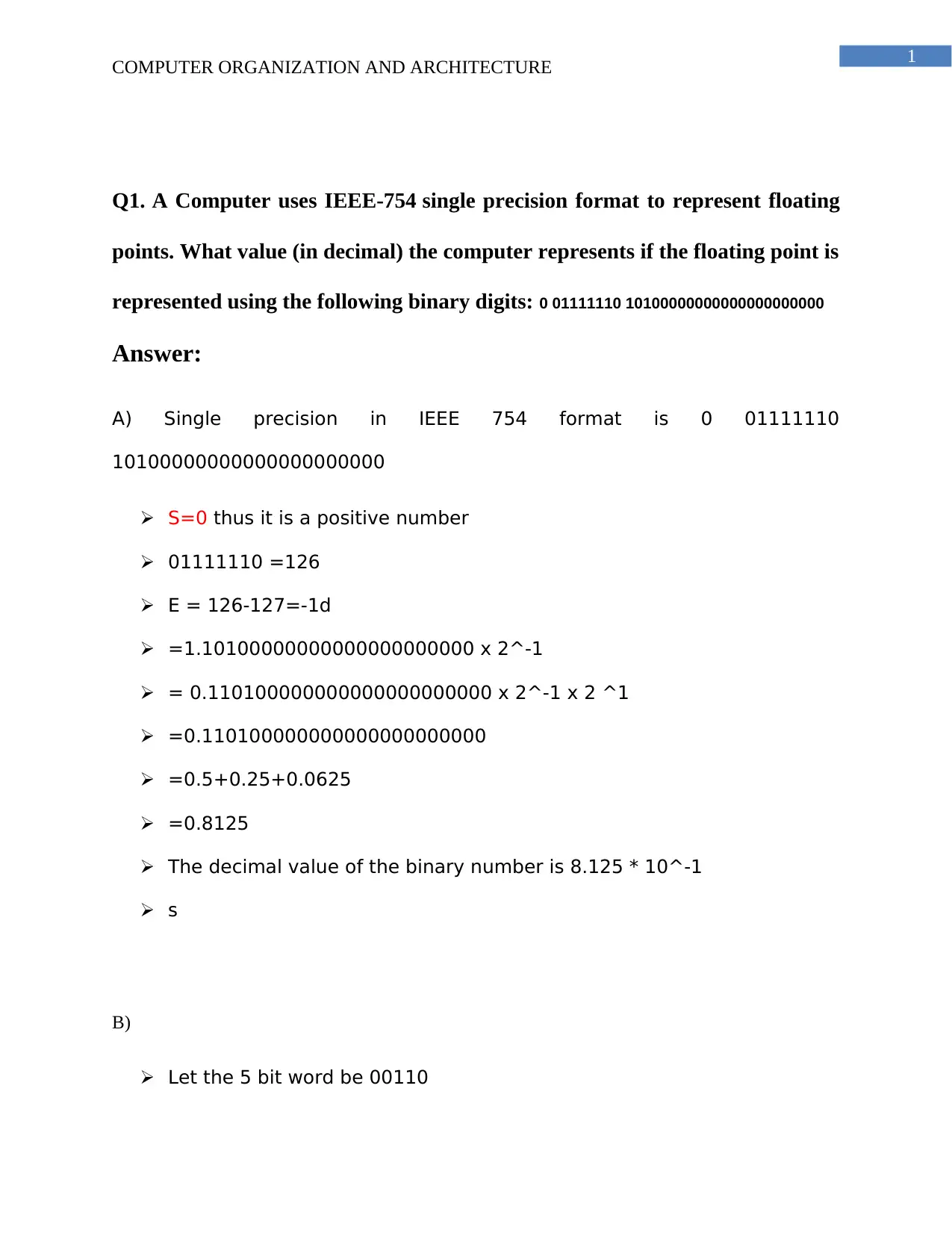

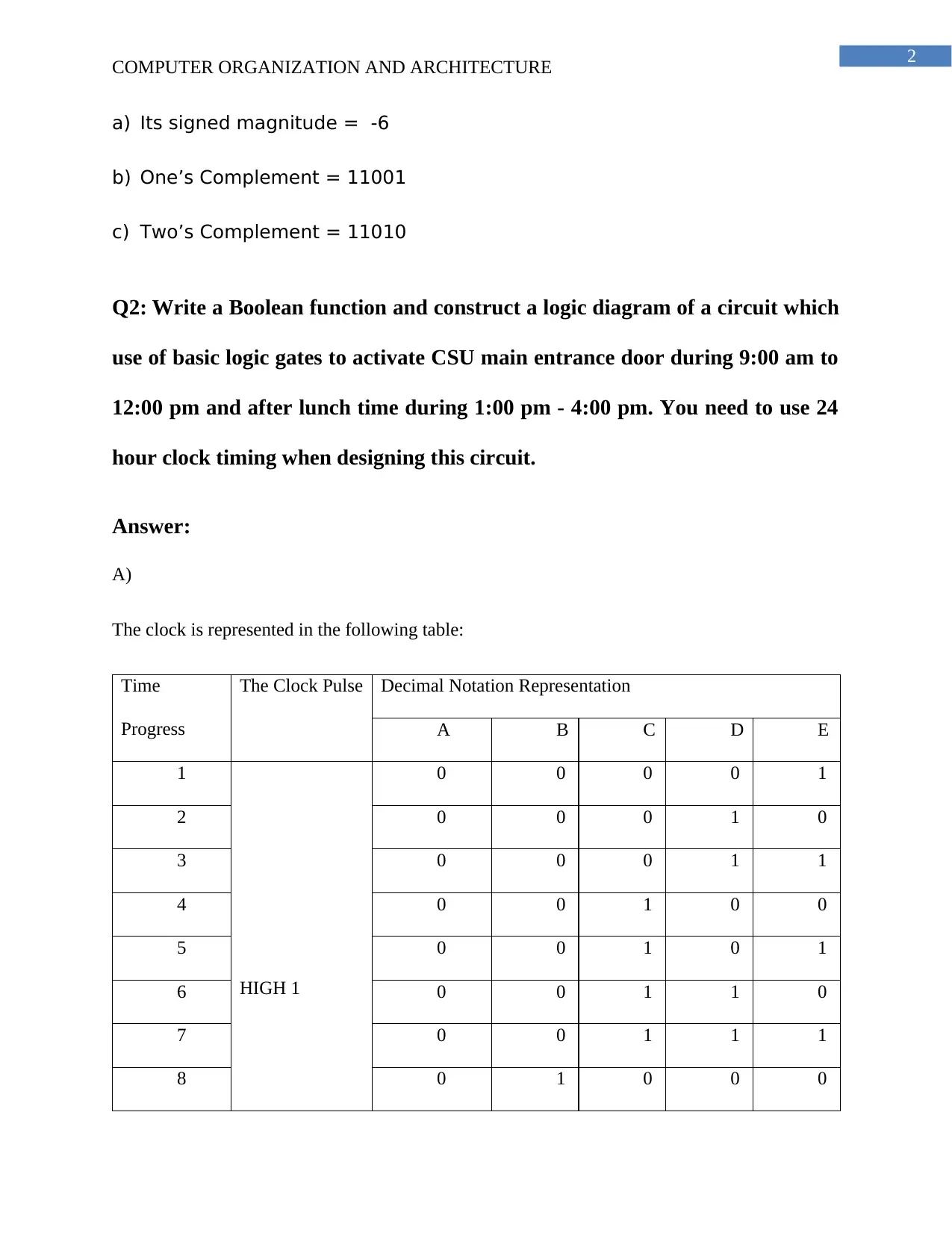

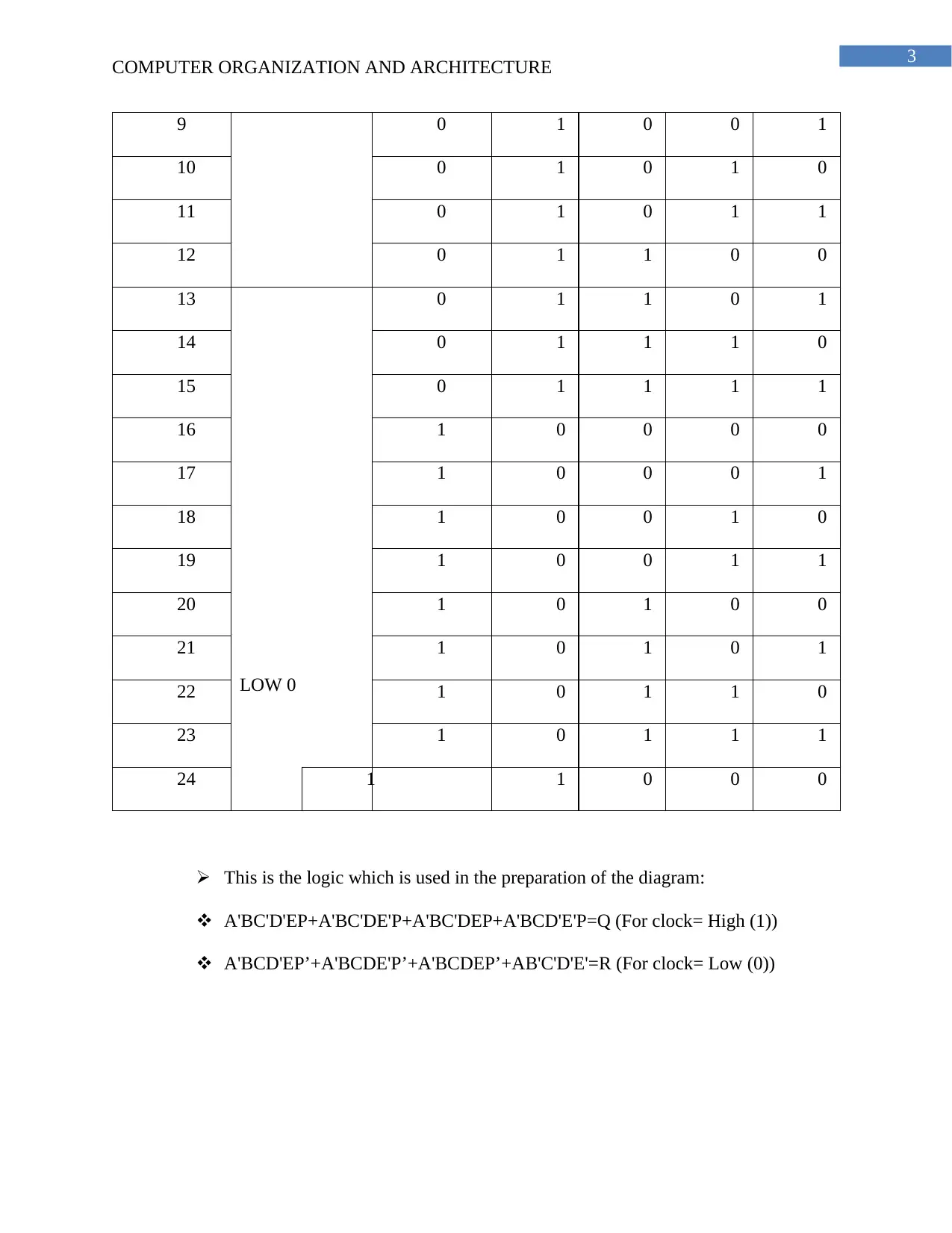

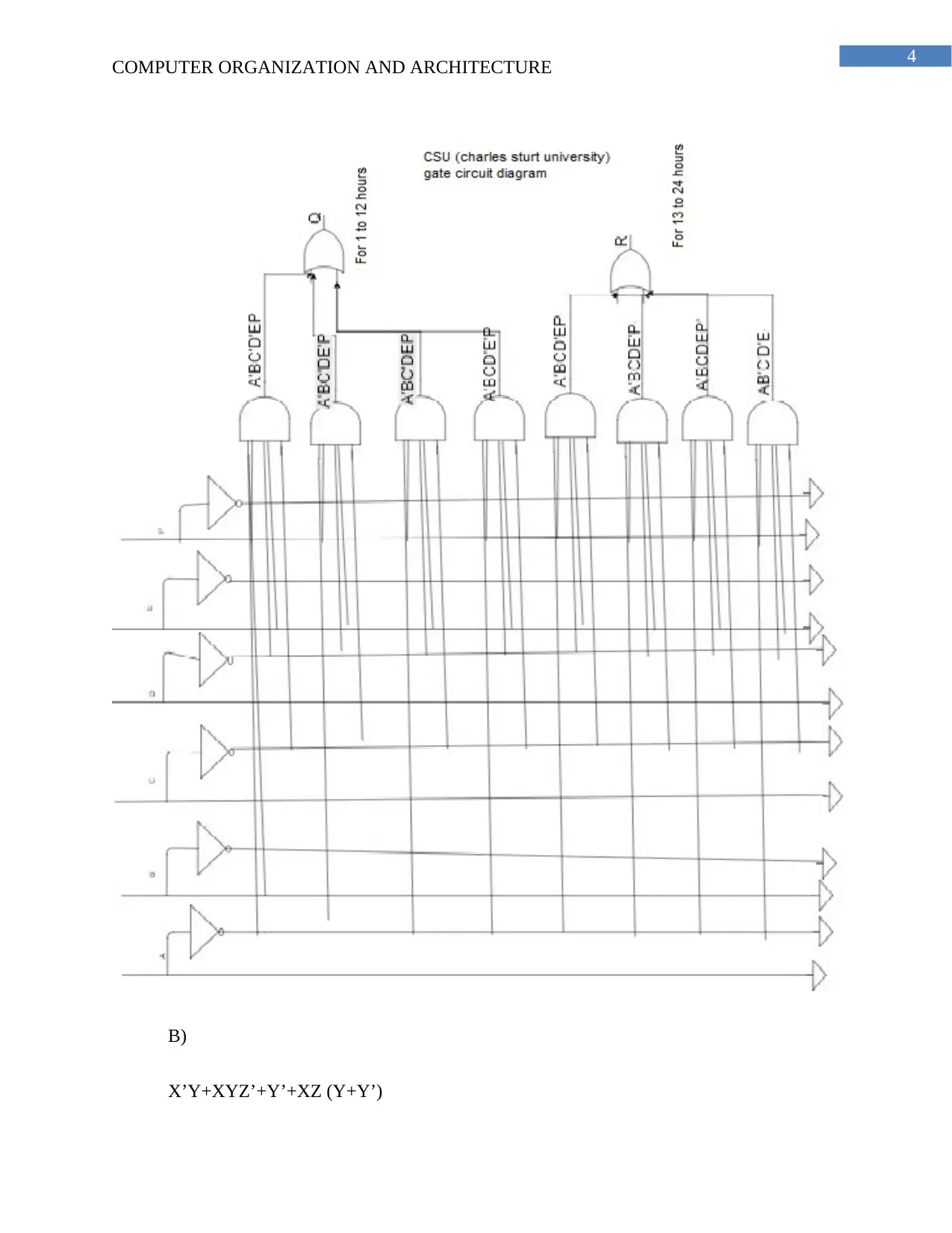

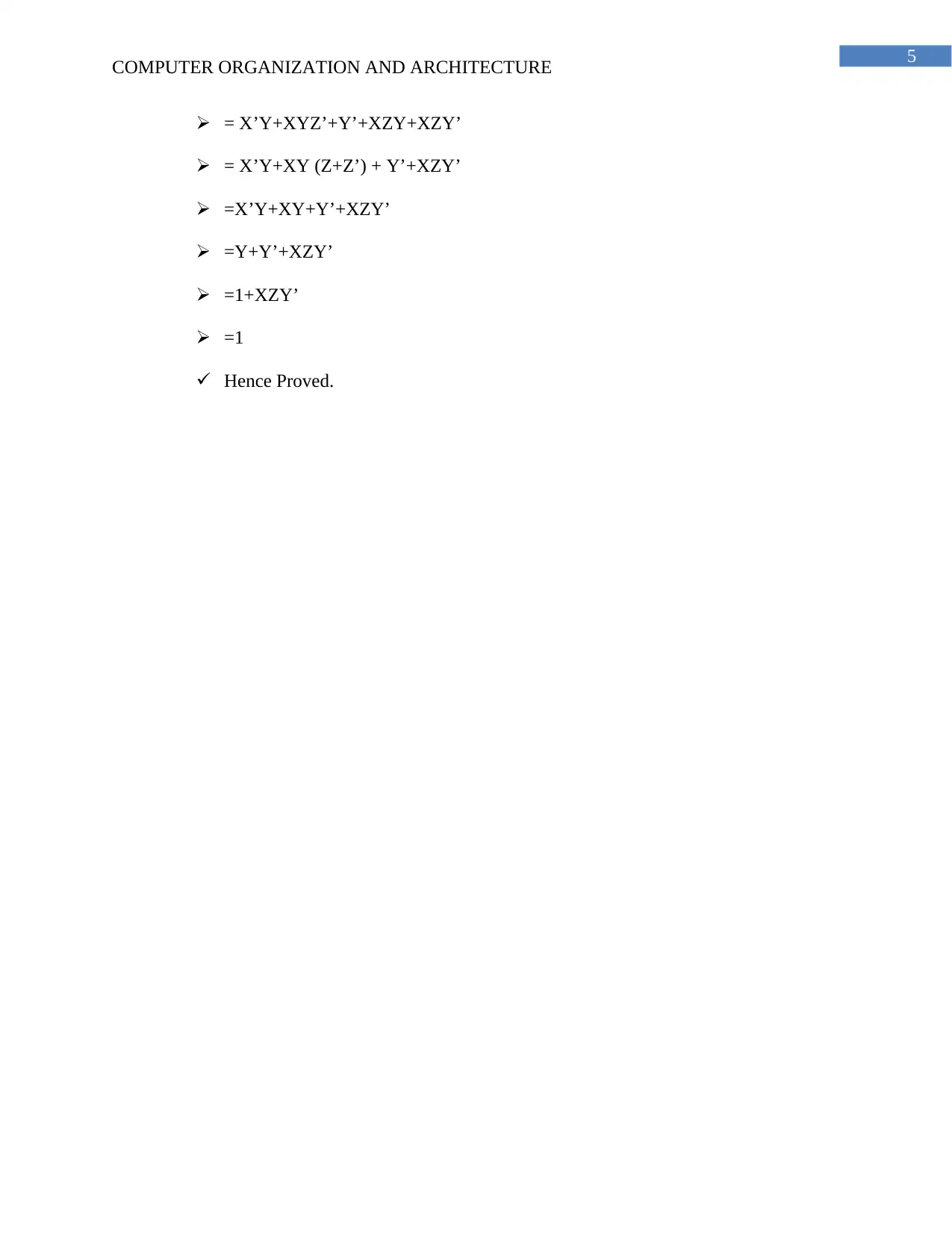

This document presents a comprehensive solution to a computer organization and architecture assignment. The assignment covers two main problems: the first involves understanding and converting floating-point numbers in IEEE-754 single-precision format to decimal values, and the second requires designing a digital logic circuit using Boolean functions and logic gates to control the CSU main entrance door's access during specific time intervals (9:00 am to 12:00 pm and 1:00 pm to 4:00 pm) using a 24-hour clock. The solution includes detailed calculations for the floating-point conversion and a step-by-step approach to developing the logic circuit, including a truth table and a simplified Boolean expression.

1 out of 6

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)