Computer Organization and Architecture (ITC544) Assignment Solution

VerifiedAdded on 2020/05/16

|6

|806

|217

Homework Assignment

AI Summary

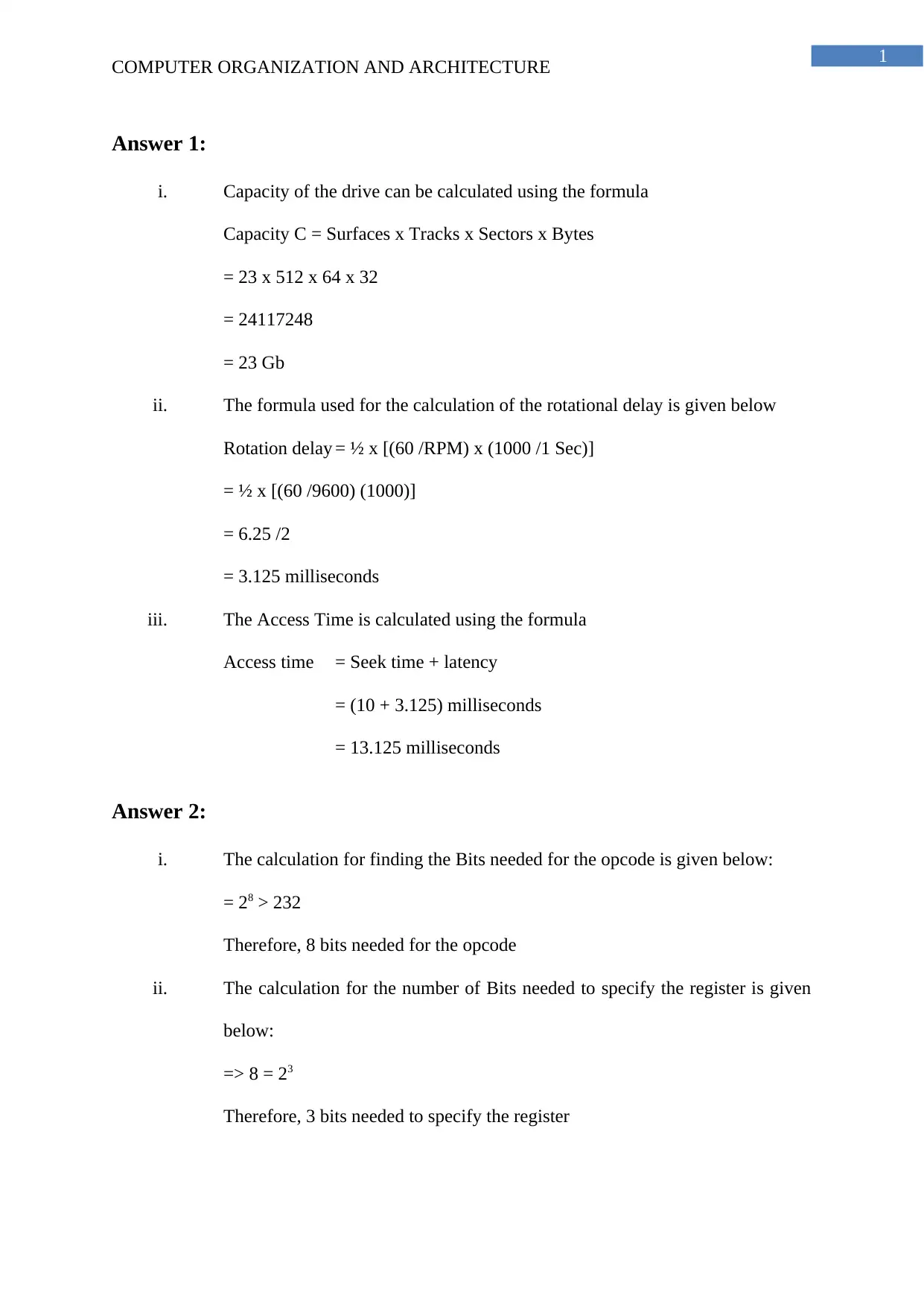

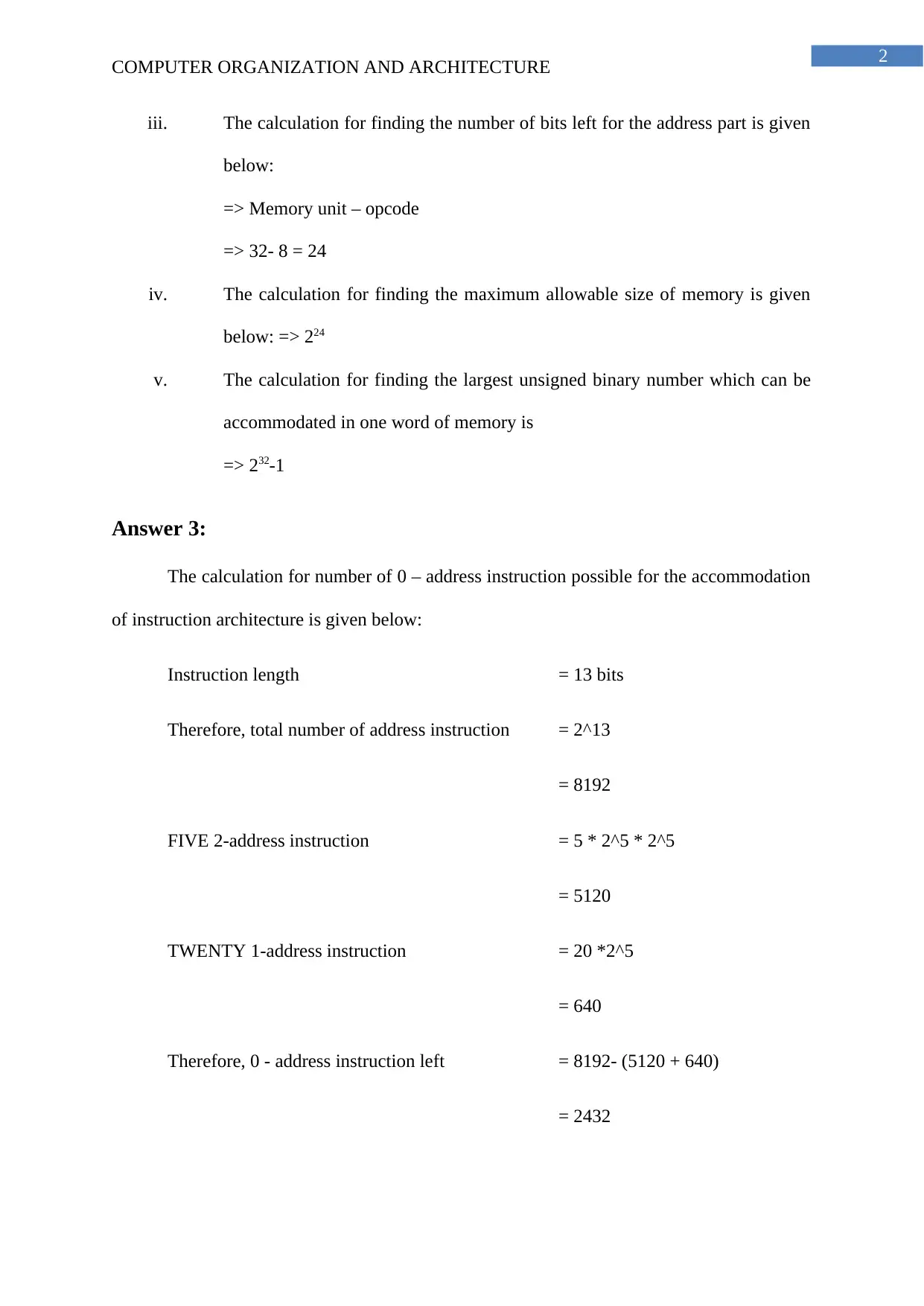

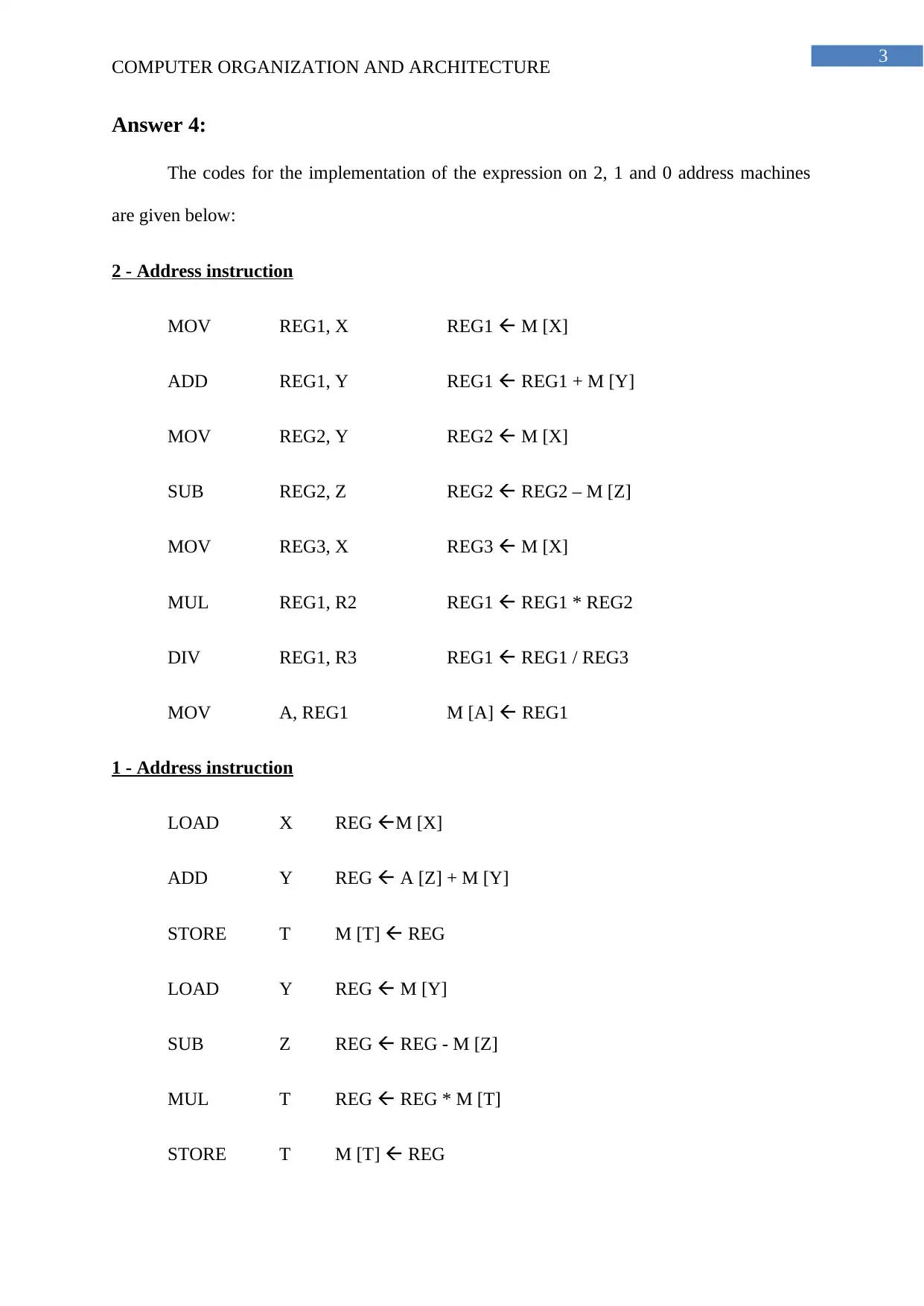

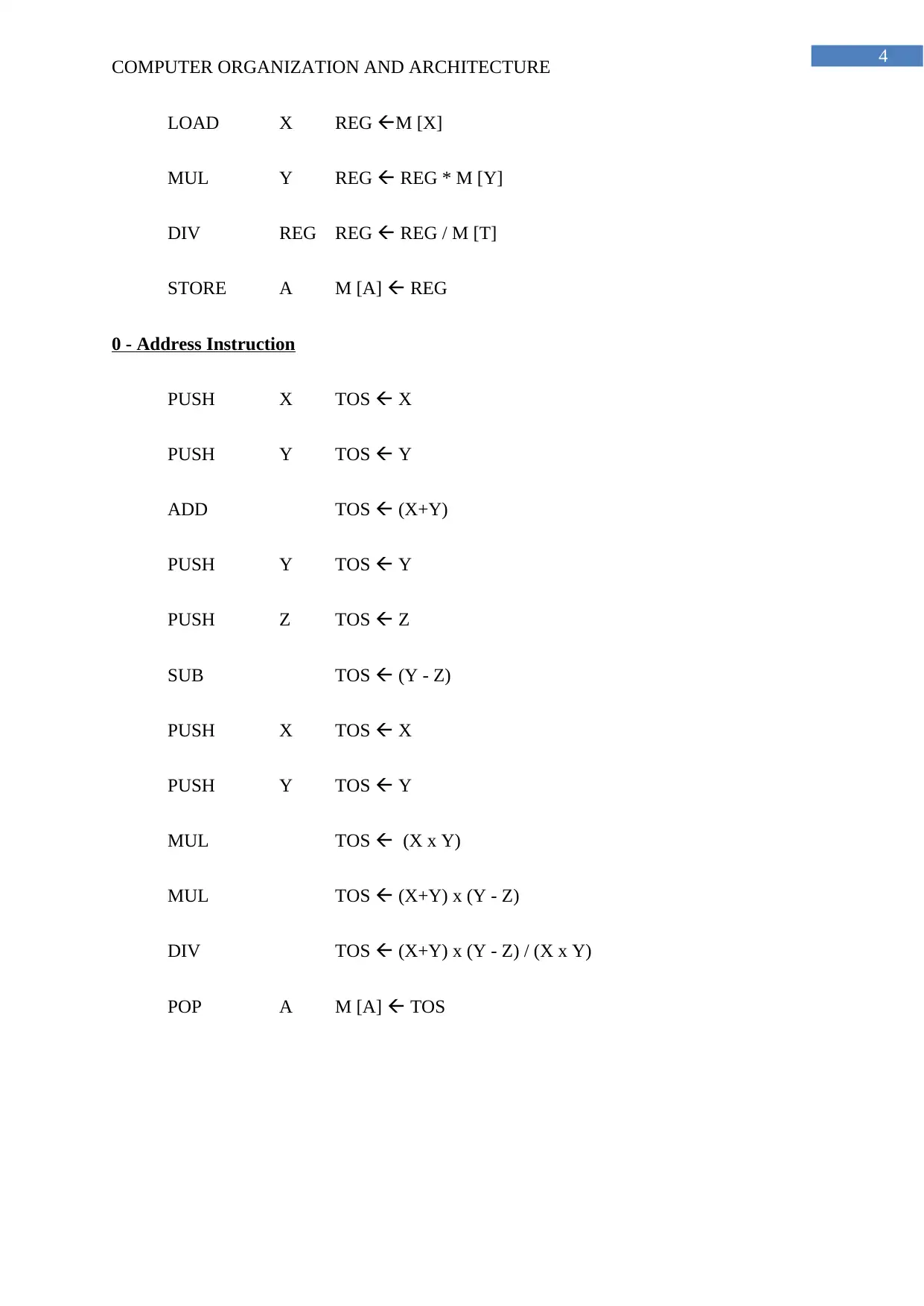

This document presents a comprehensive solution to a Computer Organization and Architecture (COA) assignment, covering several key areas. It begins with calculations for disk drive capacity, rotational delay, and access time. The solution then delves into instruction set architecture, determining the number of bits required for opcodes, registers, and memory addressing, along with calculating the maximum memory size and the largest unsigned binary number that can be stored in a memory word. The assignment further explores instruction formats, specifically calculating the number of zero-address instructions possible. Finally, the solution provides assembly language code implementations for a given expression on 2-address, 1-address, and 0-address machines. The solution includes a bibliography of relevant academic sources.

1 out of 6

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)