ITC544 Computer Organization Assignment - Number Systems and Logic

VerifiedAdded on 2021/04/21

|7

|646

|46

Homework Assignment

AI Summary

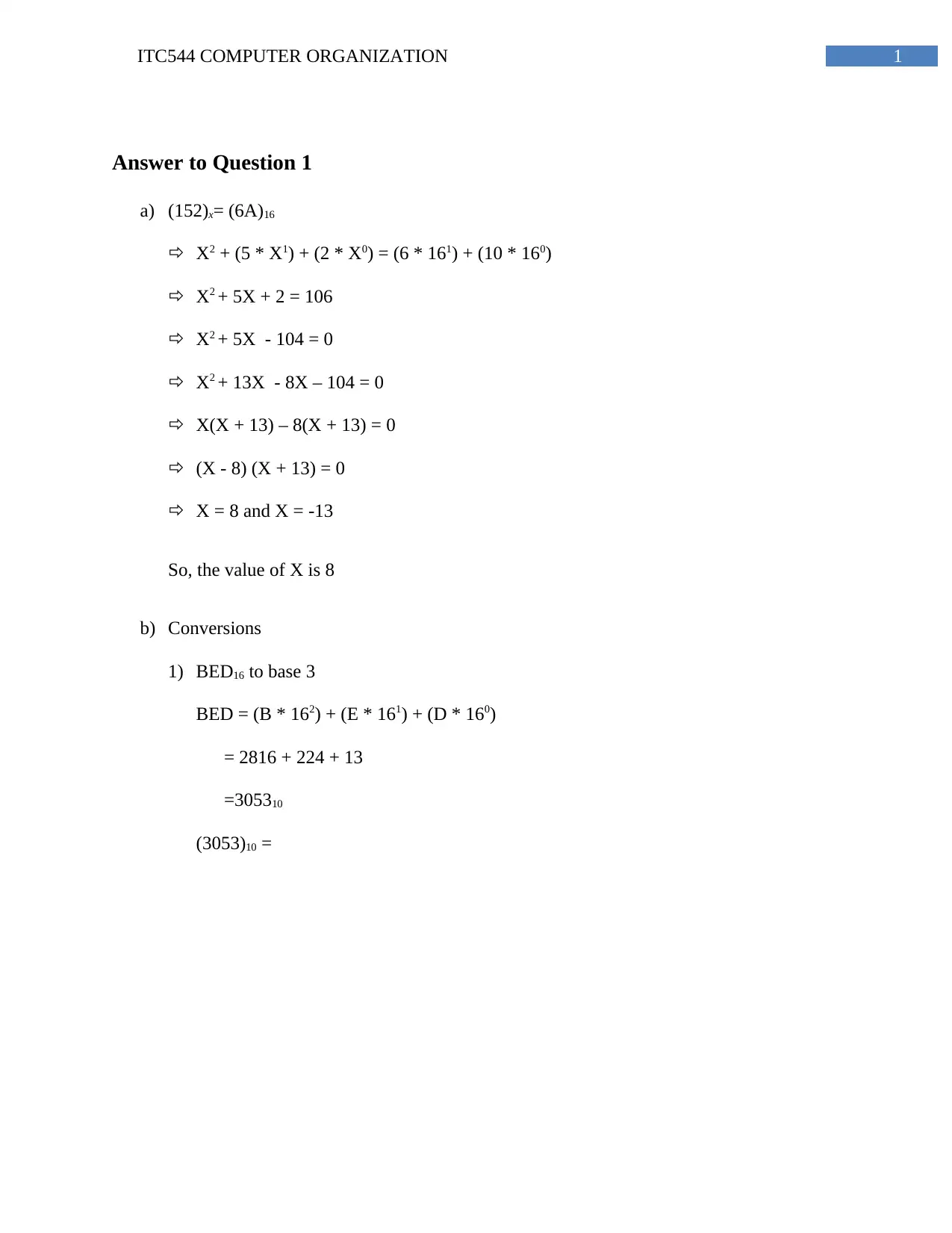

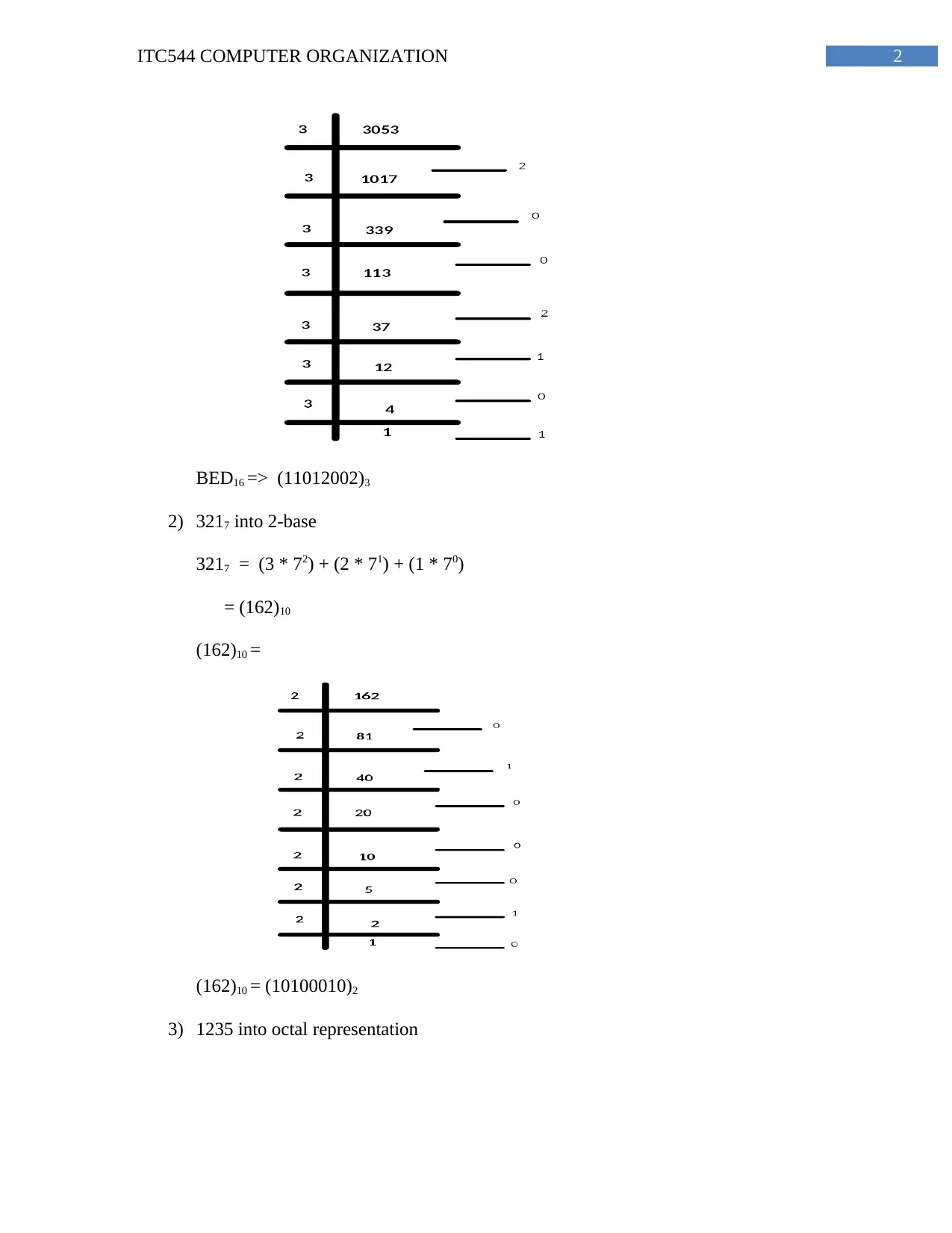

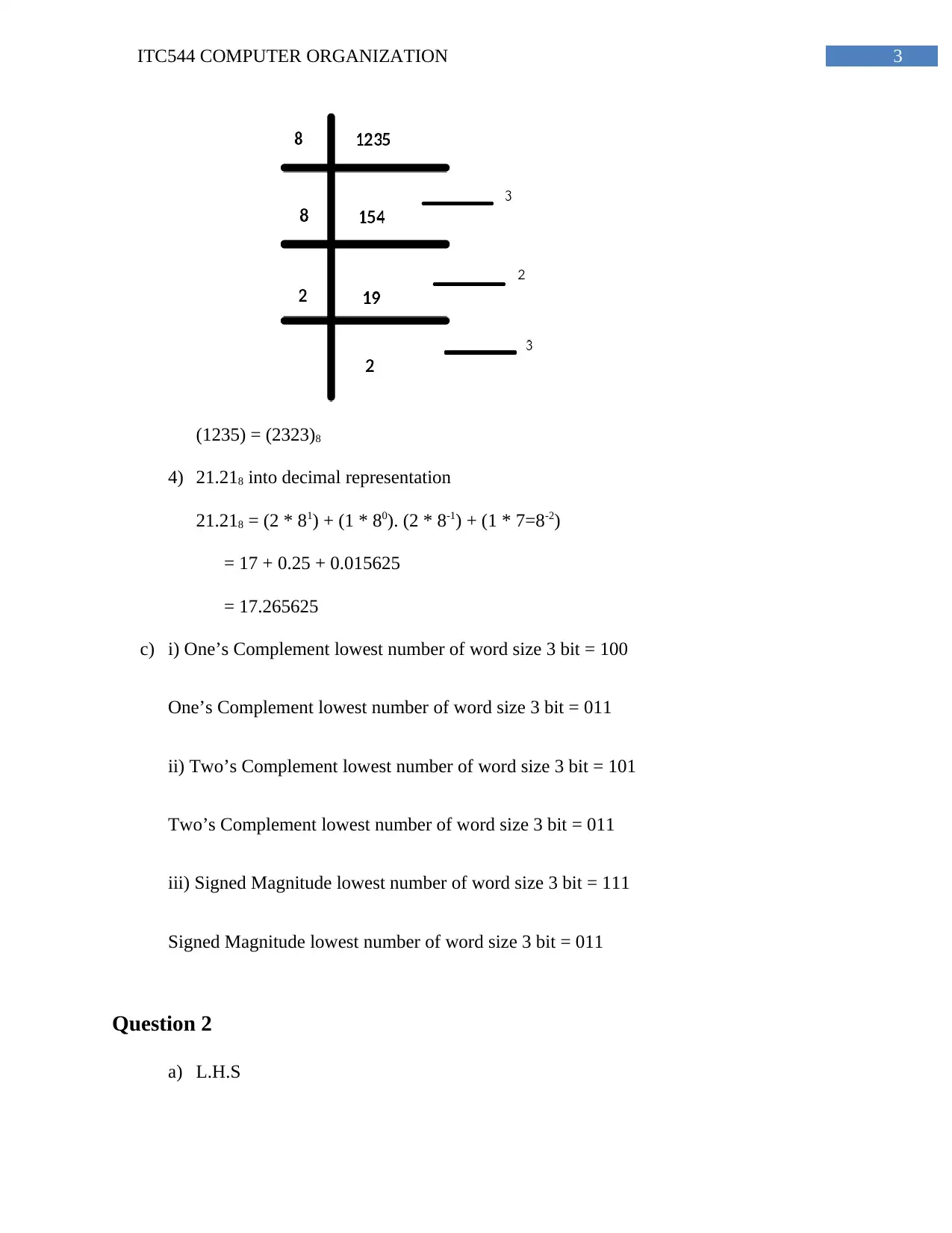

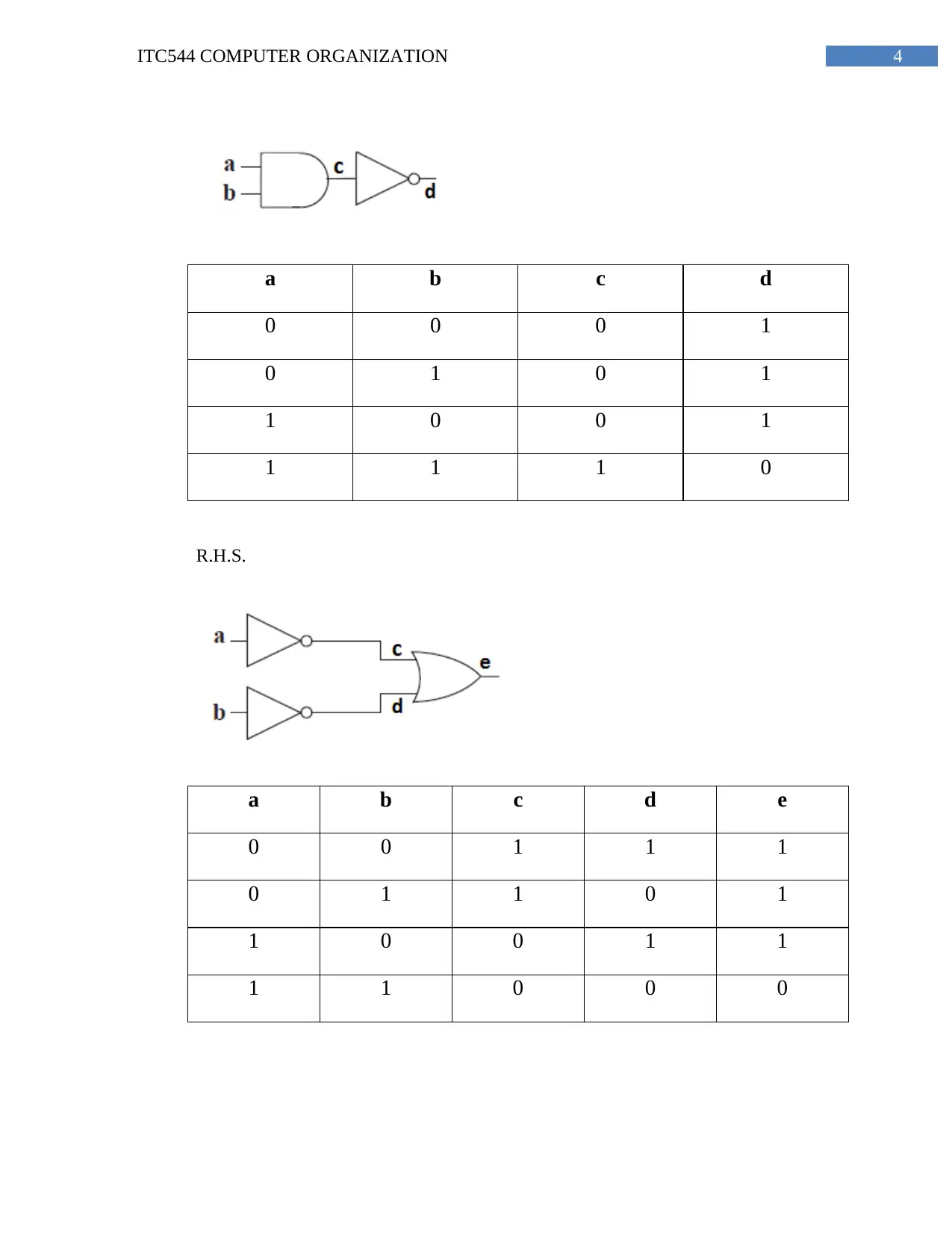

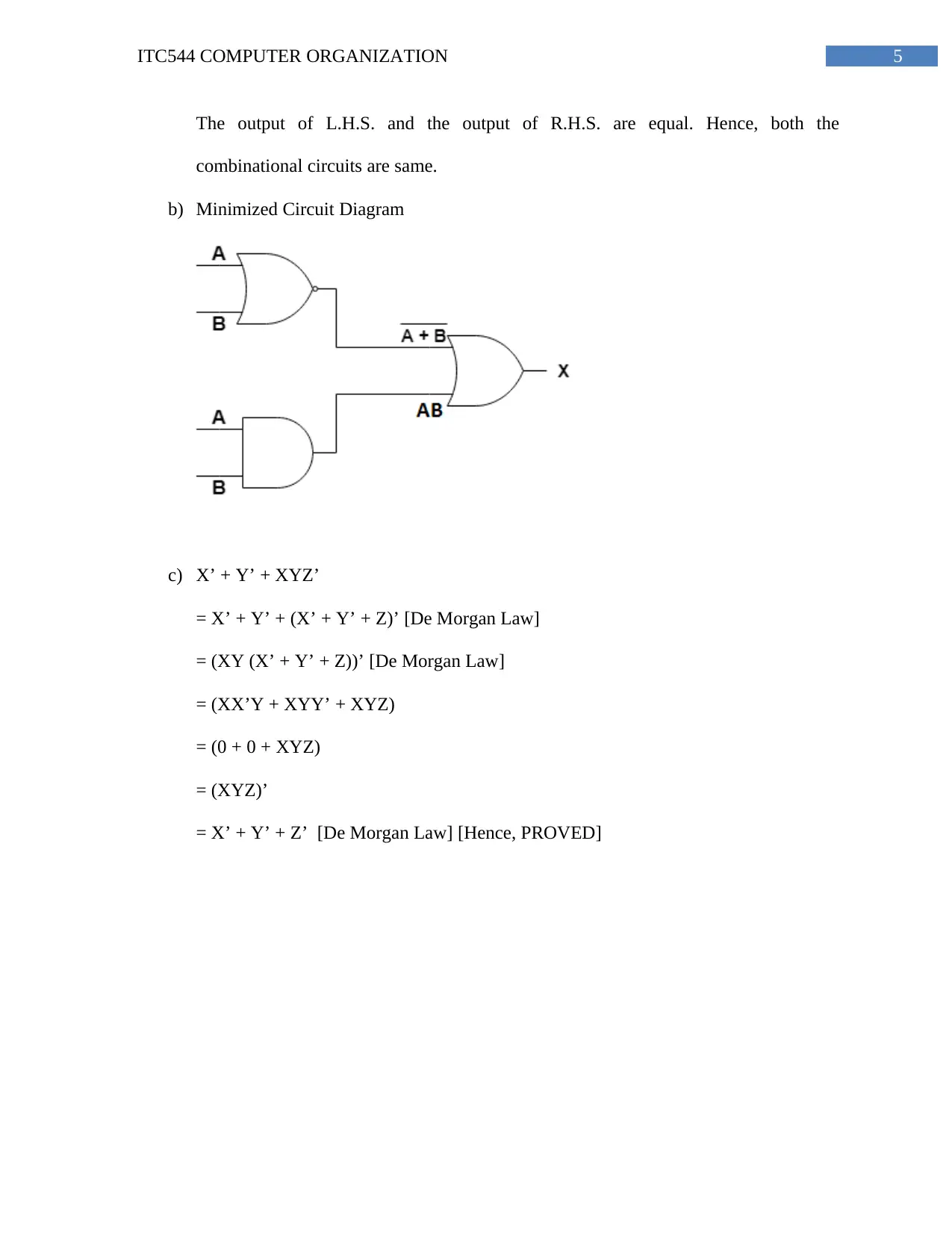

This document presents a comprehensive solution to an ITC544 Computer Organization assignment. The solution addresses several key concepts, including number system conversions between different bases (binary, hexadecimal, octal, and decimal). The student demonstrates proficiency in converting numbers between these bases, providing detailed steps for each conversion. Furthermore, the assignment explores logic circuits, comparing the outputs of two combinational circuits to prove their equivalence. The student also simplifies a logic expression using De Morgan's Law, providing a step-by-step proof. The assignment concludes with a bibliography of relevant academic sources. This solution showcases a strong understanding of fundamental computer organization principles and problem-solving abilities. The assignment is available on Desklib, a platform offering AI-powered study tools for students.

1 out of 7

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)