Computer Organization and Architecture - Assignment 1 - ITC544

VerifiedAdded on 2019/11/12

|5

|401

|222

Homework Assignment

AI Summary

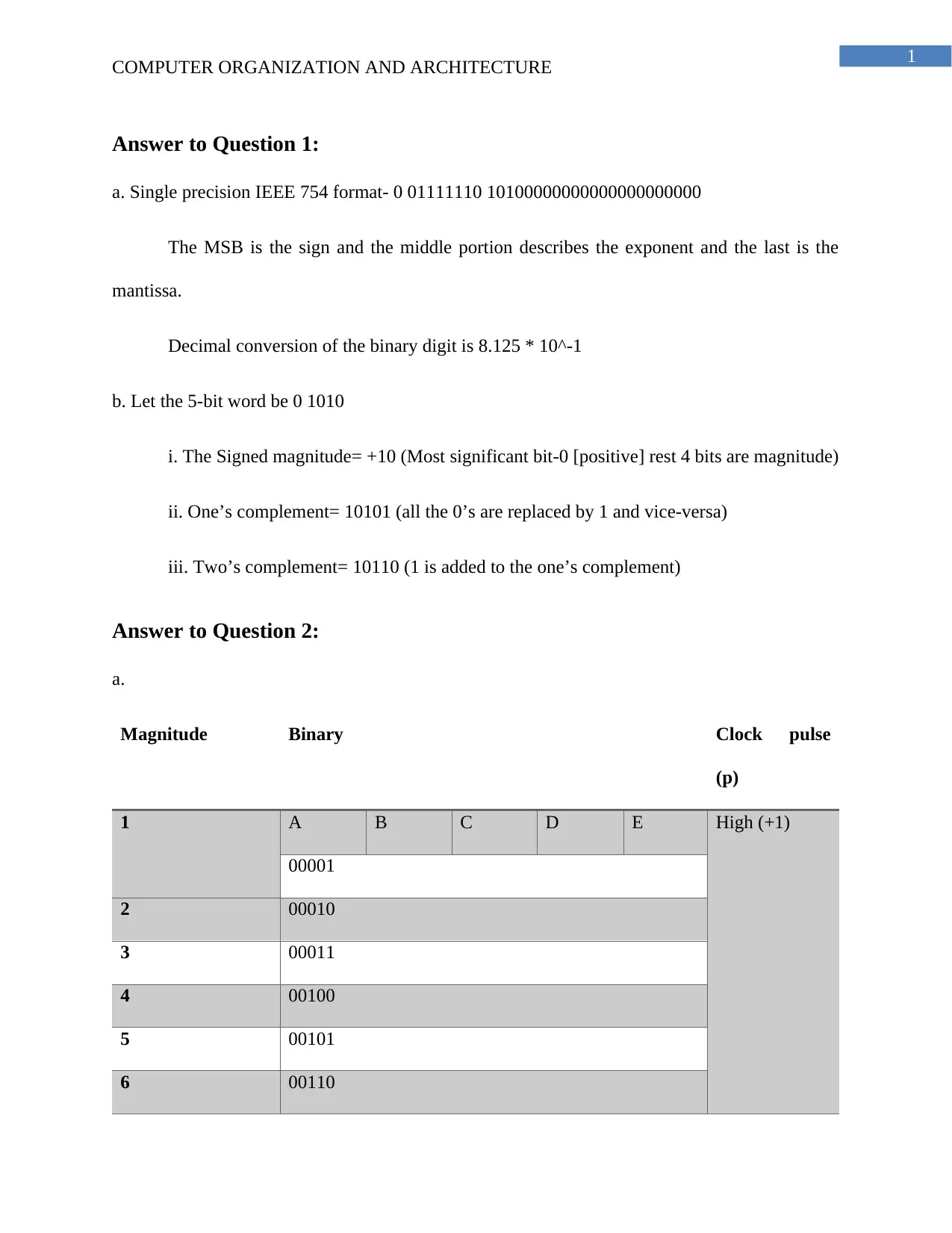

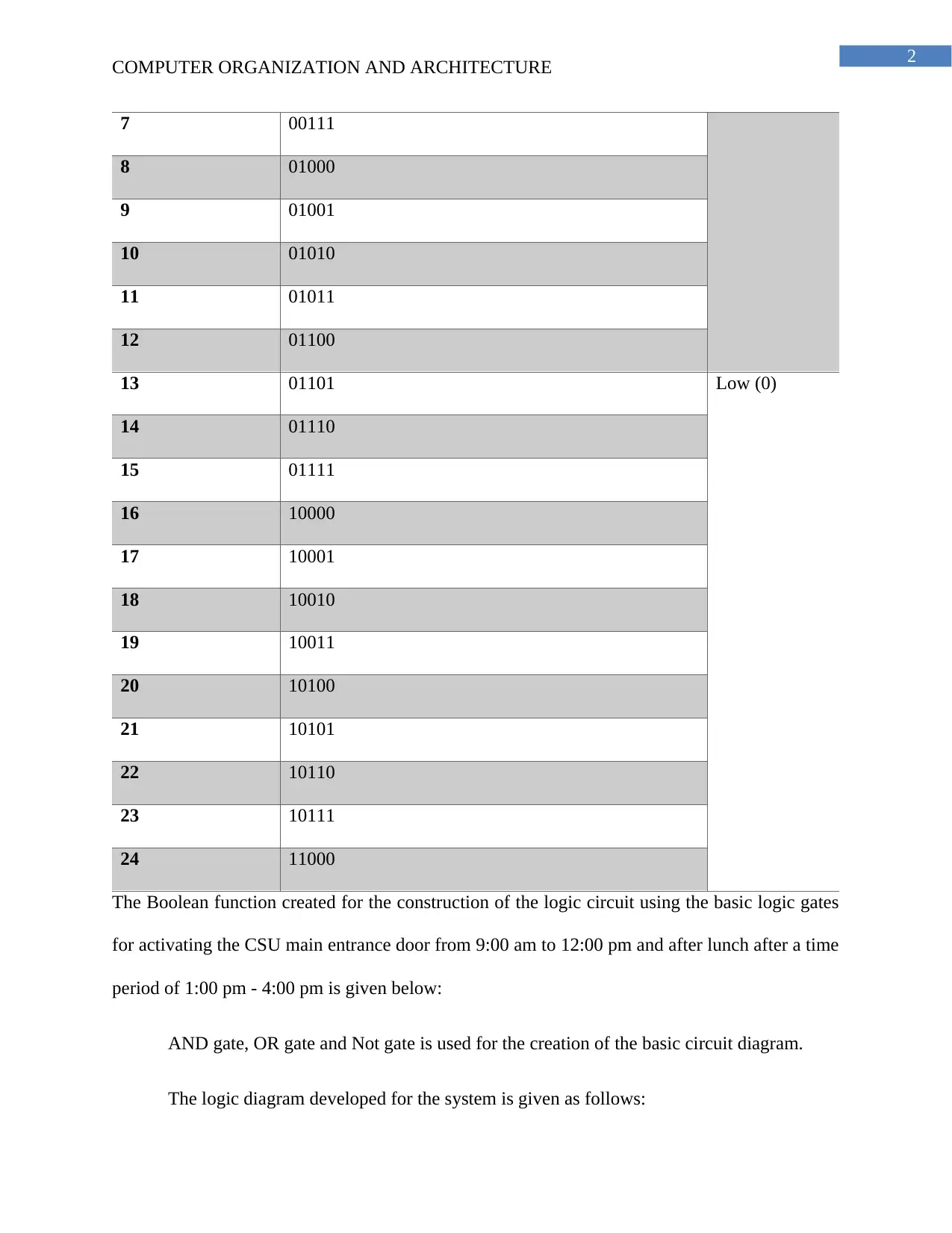

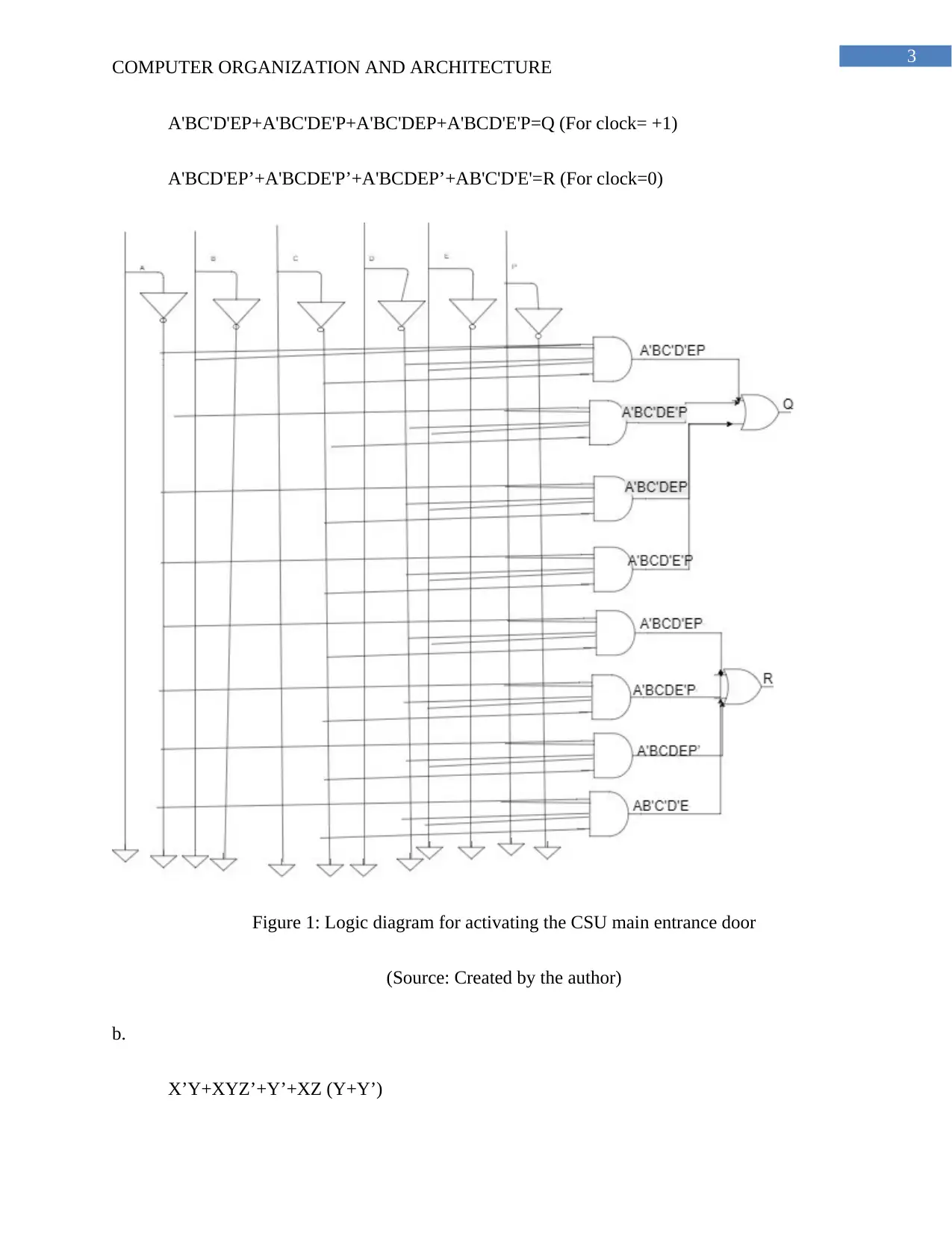

This document presents a solution to a computer organization and architecture assignment (ITC544). The assignment addresses several key concepts, including data representation using IEEE 754 single-precision format and binary conversions. It covers the representation of numbers in signed magnitude, one's complement, and two's complement forms. Furthermore, the assignment includes a practical application of logic circuits, demonstrating how AND, OR, and NOT gates can be used to create a system for controlling the CSU main entrance door. The solution provides a Boolean function and a logic diagram to illustrate the circuit design. Finally, the document includes a proof of a Boolean expression using algebraic manipulation. This resource is designed to help students understand and solve similar problems in computer organization and architecture.

1 out of 5

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)