Data Logic Representation: Number Conversion and Circuit Proof

VerifiedAdded on 2023/06/12

|8

|933

|160

Homework Assignment

AI Summary

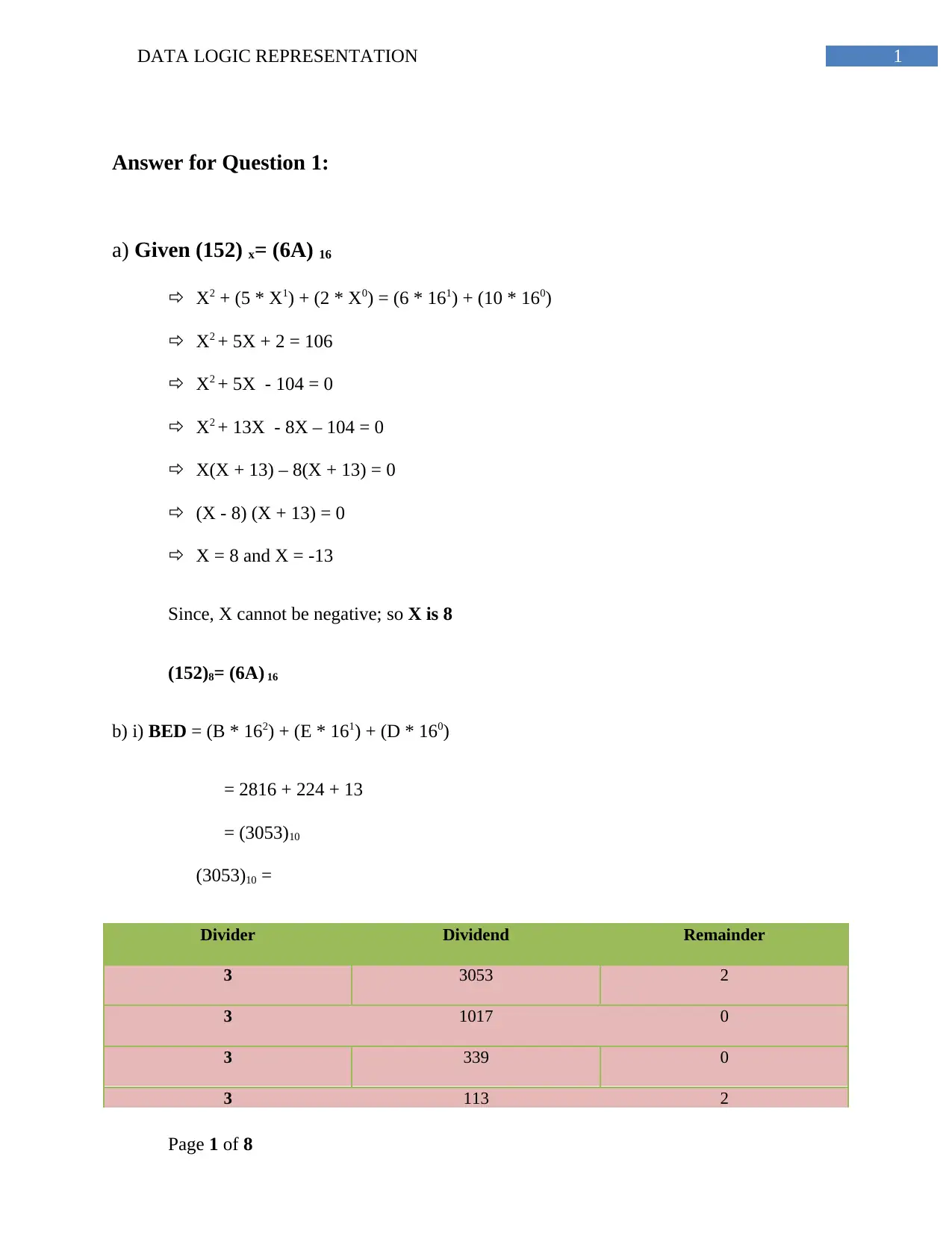

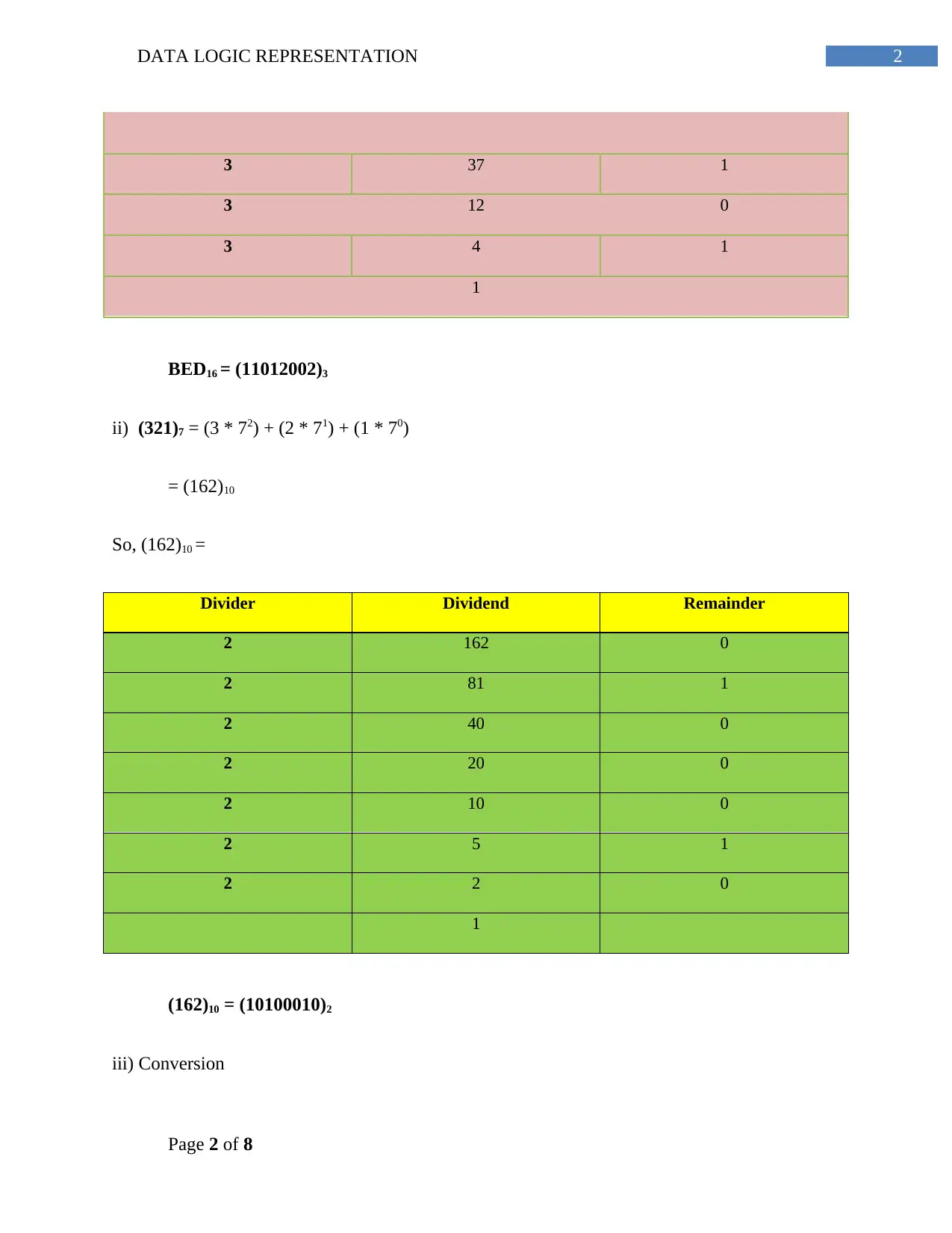

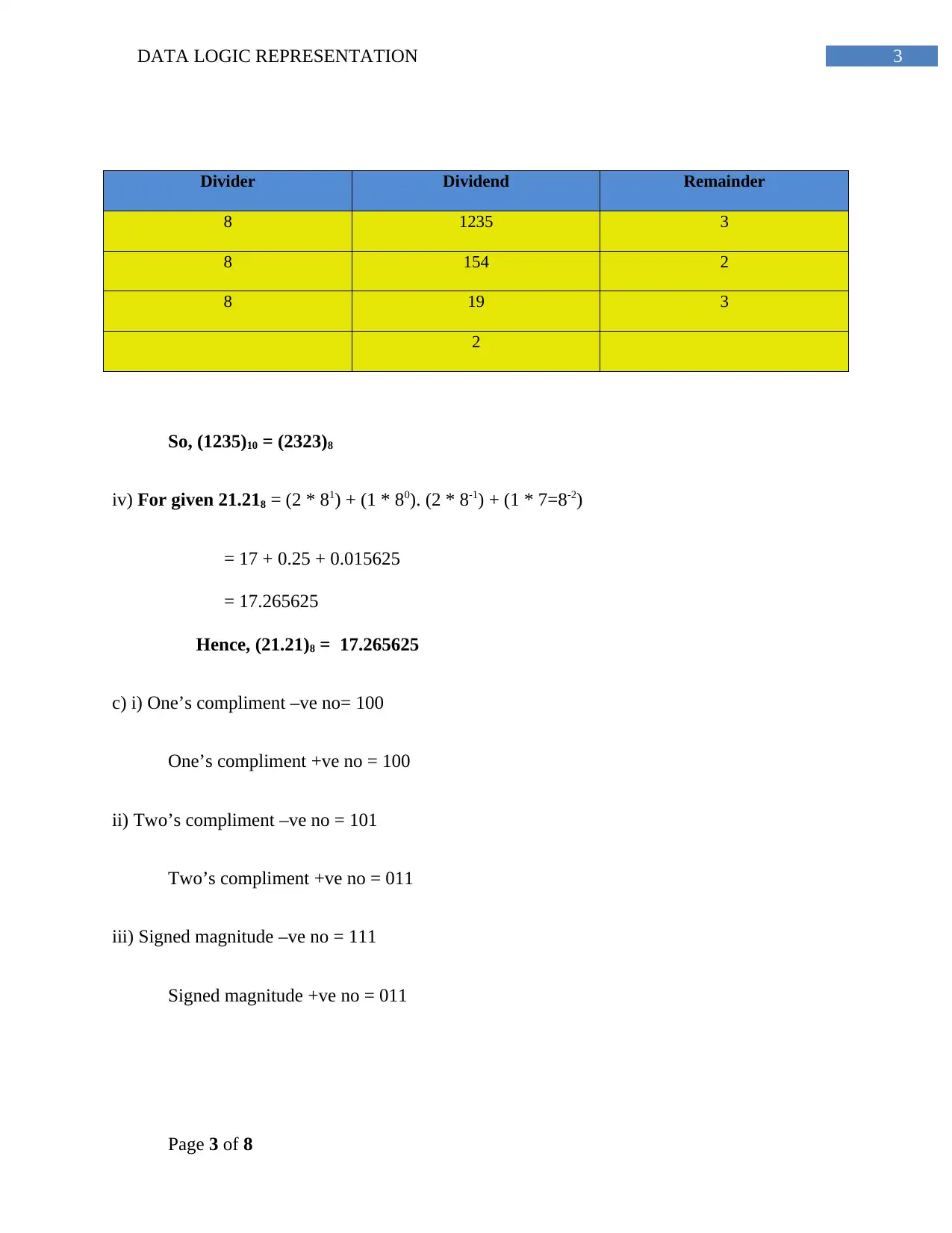

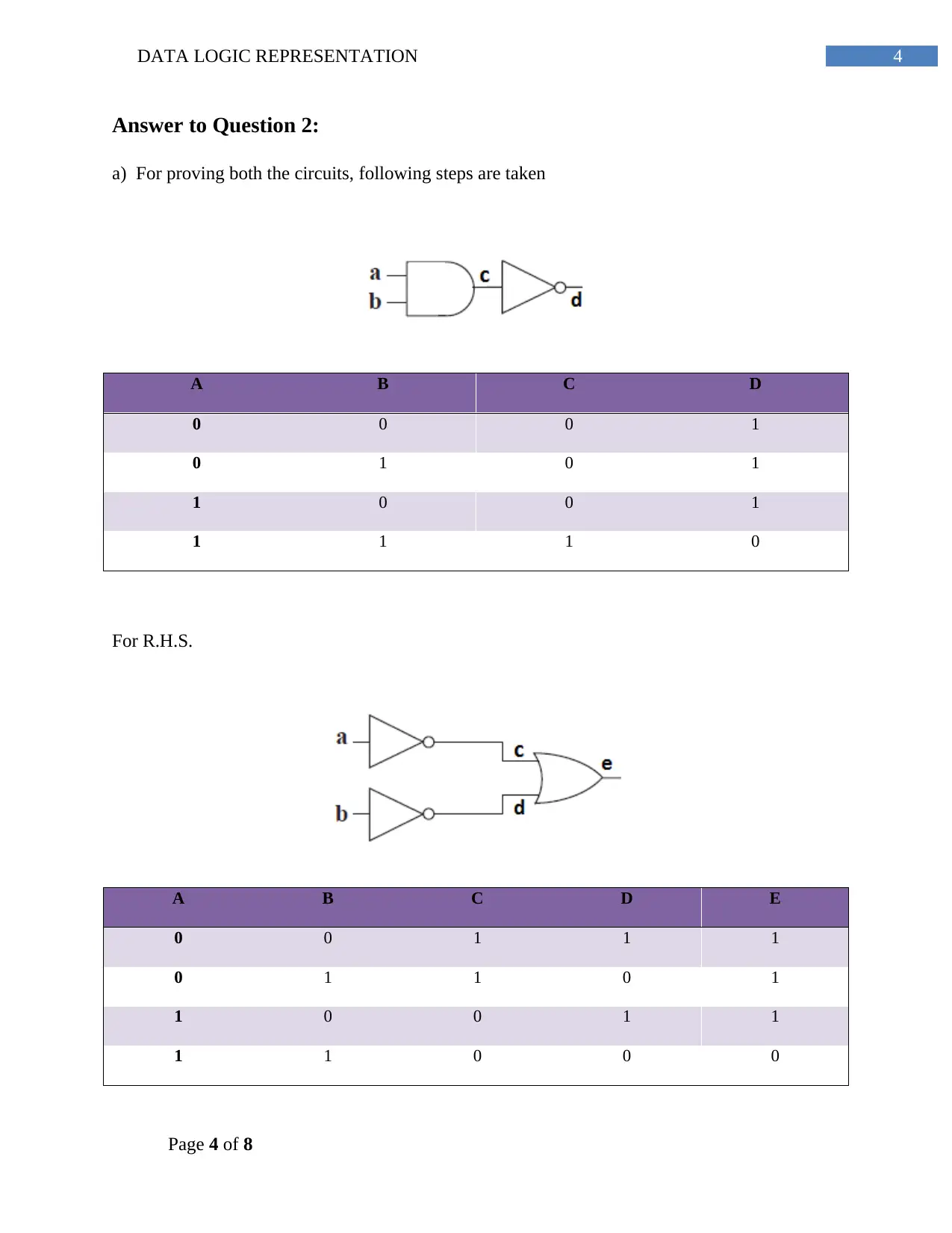

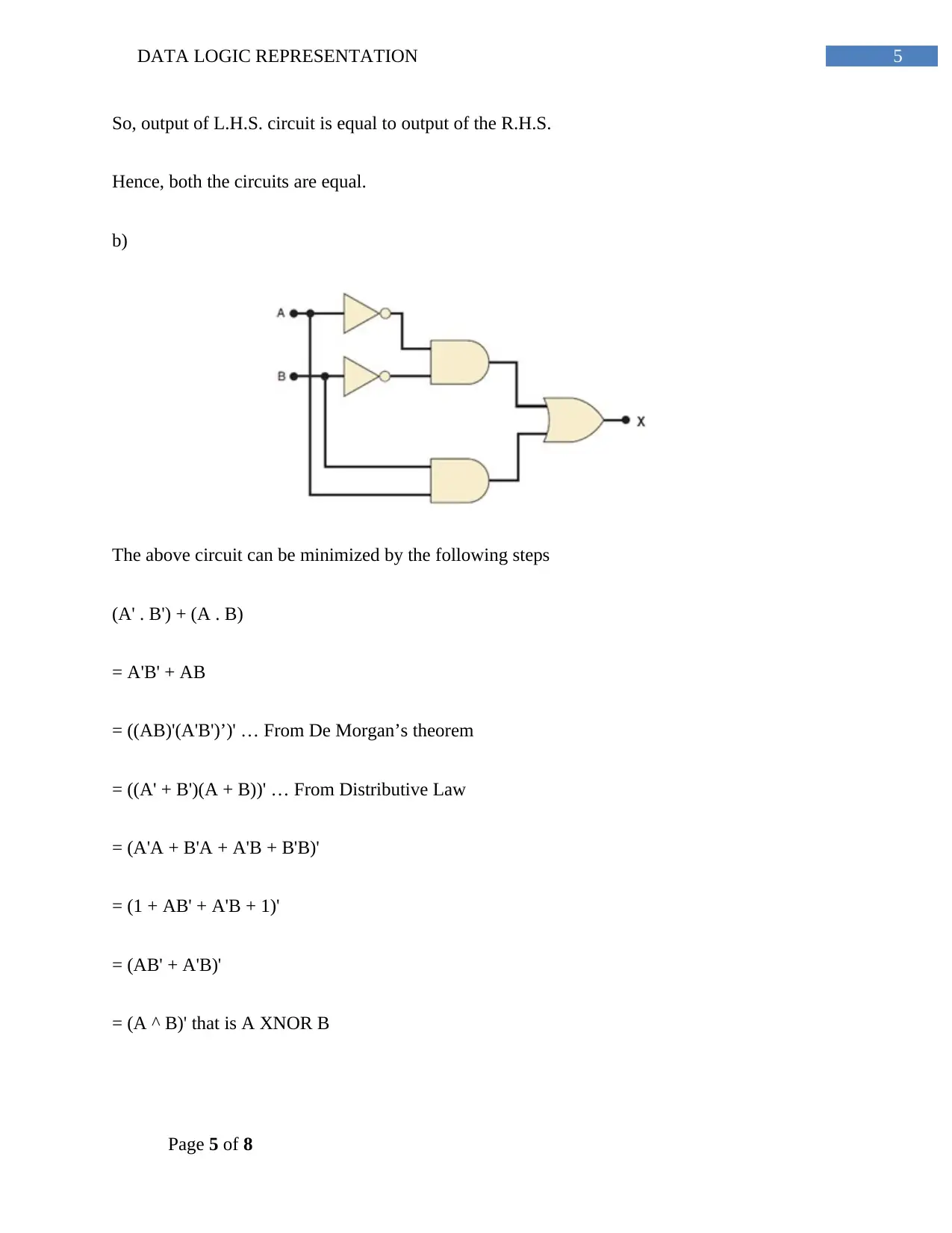

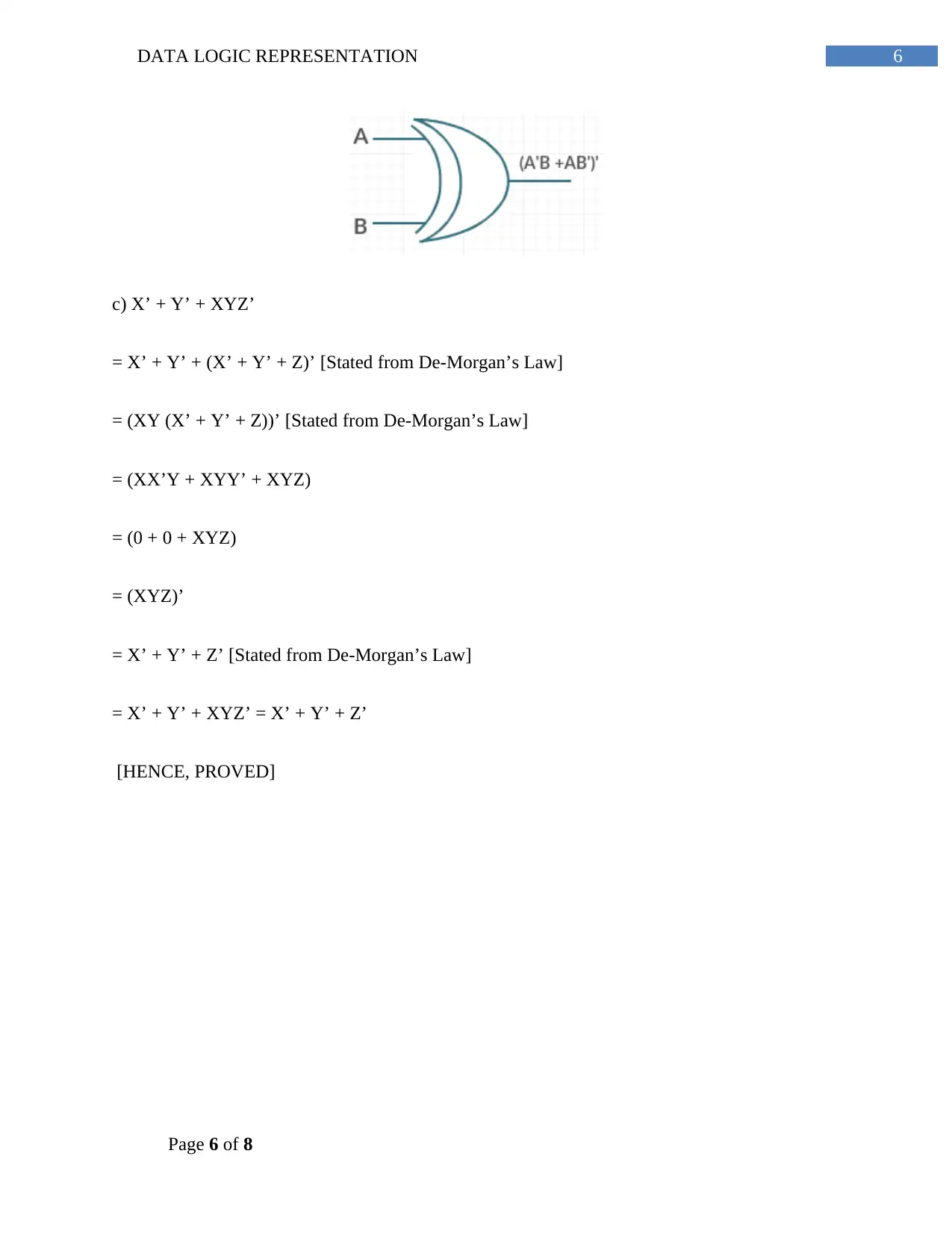

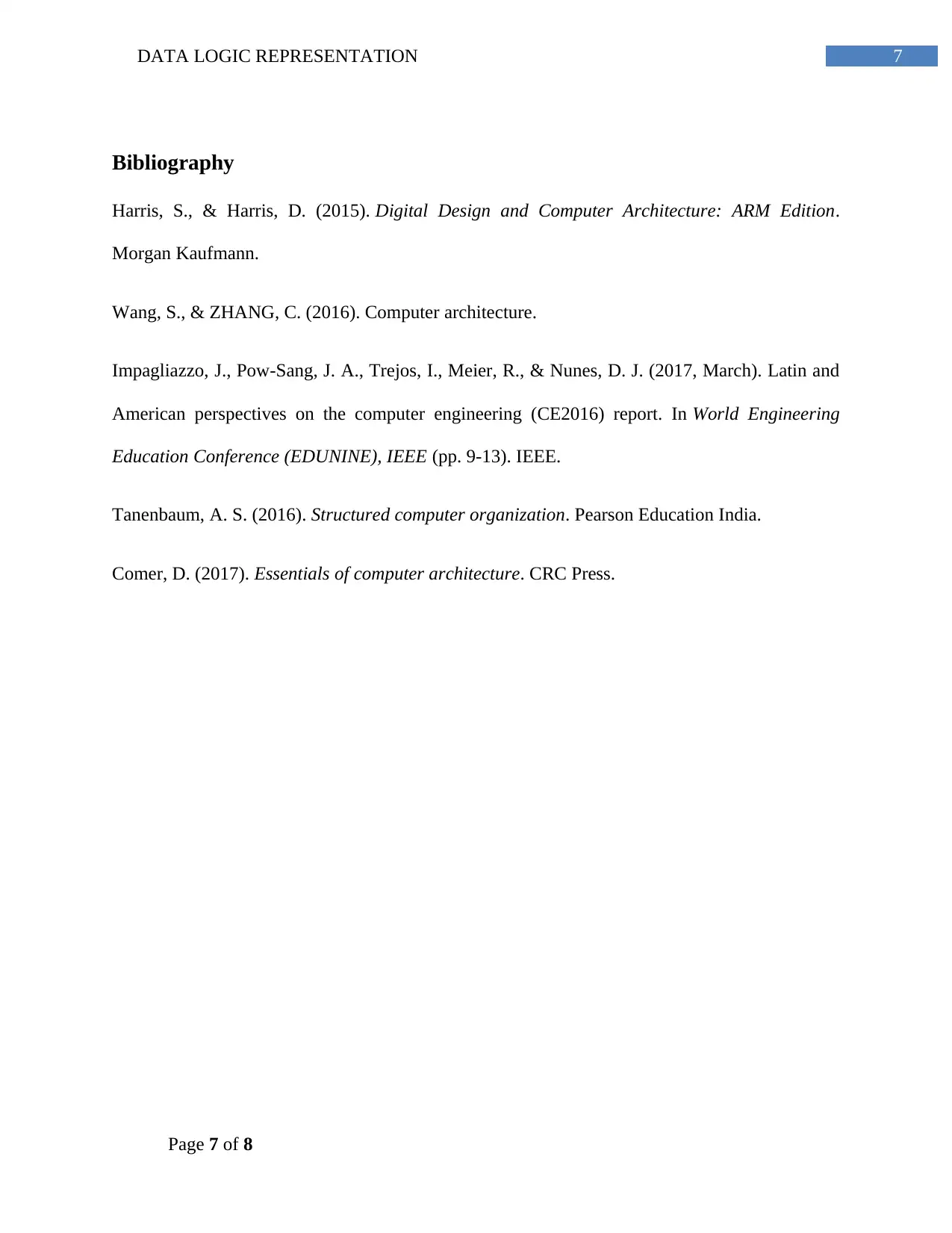

This assignment solution delves into the fundamental concepts of data logic representation, addressing key areas such as number system conversions and logic gate equivalency. The solution begins by determining the base 'x' for a given equation involving hexadecimal and an unknown base. It then performs conversions between different number systems, including hexadecimal to base-3, base-7 to binary, decimal to octal, and base-8 to decimal. The assignment further explores the representation of positive and negative numbers using one's complement, two's complement, and signed magnitude methods within a 3-bit computer. Additionally, the solution provides a proof of equivalence for two combinational circuits and demonstrates the minimization of a logic circuit using Boolean algebra and De Morgan's laws. The document concludes by proving a Boolean algebra expression. Desklib offers a wealth of similar solved assignments and resources for students.

1 out of 8

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)