University Data Representation, Boolean Algebra and Circuit Design

VerifiedAdded on 2020/05/28

|5

|711

|143

Homework Assignment

AI Summary

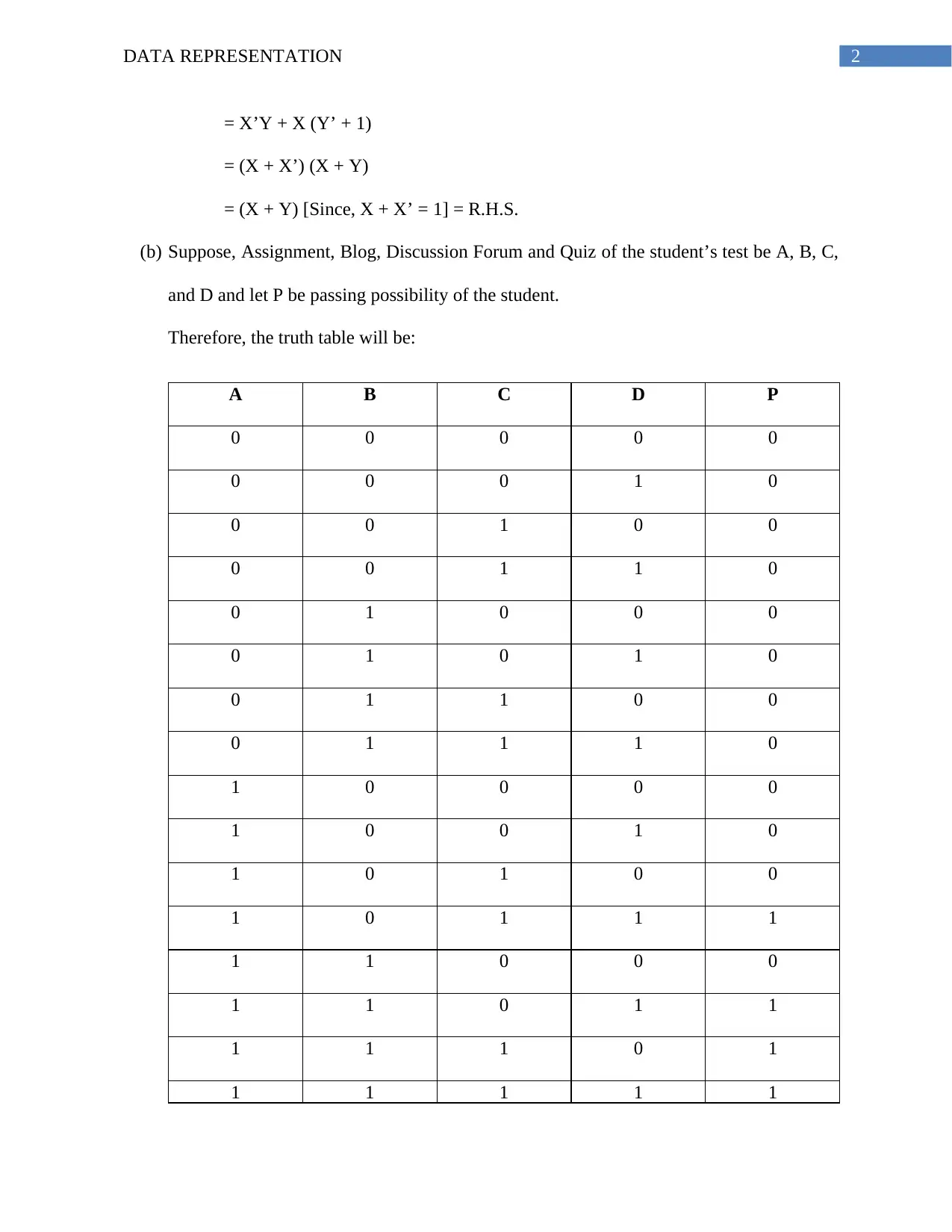

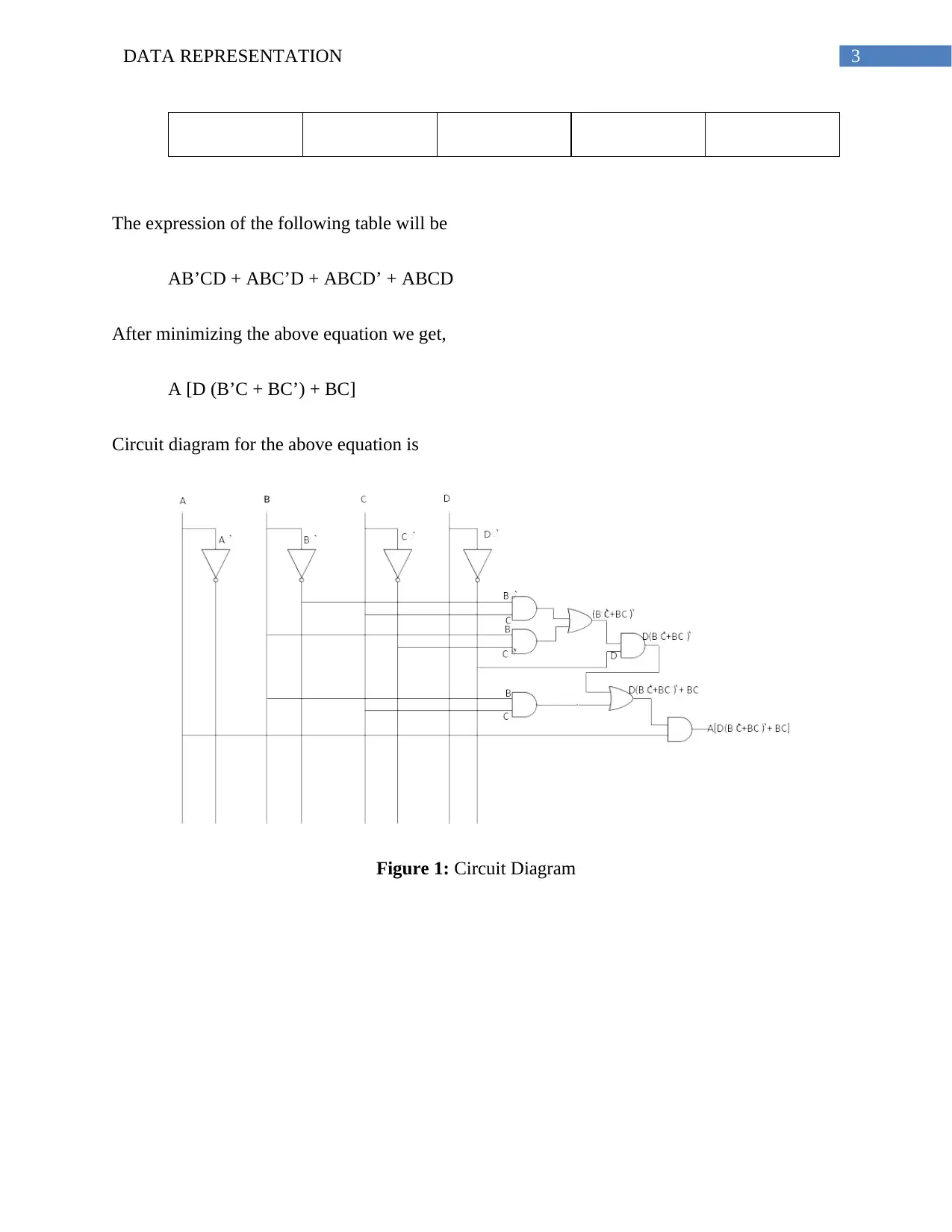

This assignment solution covers fundamental concepts in data representation and digital logic. It begins with an analysis of number systems, including one's complement, two's complement, signed magnitude, and unsigned magnitude representations, along with conversions between binary, octal, decimal, and hexadecimal systems. The solution then delves into Boolean algebra, simplifying and proving logical expressions using distributive laws and truth tables. Furthermore, it includes a truth table analysis for a scenario involving assignments, blogs, discussion forums, and quizzes, leading to the derivation of a minimized Boolean expression and the corresponding circuit diagram. The assignment concludes with a bibliography of relevant sources, including academic publications on digital logic, computer design, and related topics. This resource provides a comprehensive understanding of data representation and logic design principles.

1 out of 5

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)