Assignment 1 - ITC544: Data Representation and Digital Logic Analysis

VerifiedAdded on 2020/02/24

|3

|656

|91

Homework Assignment

AI Summary

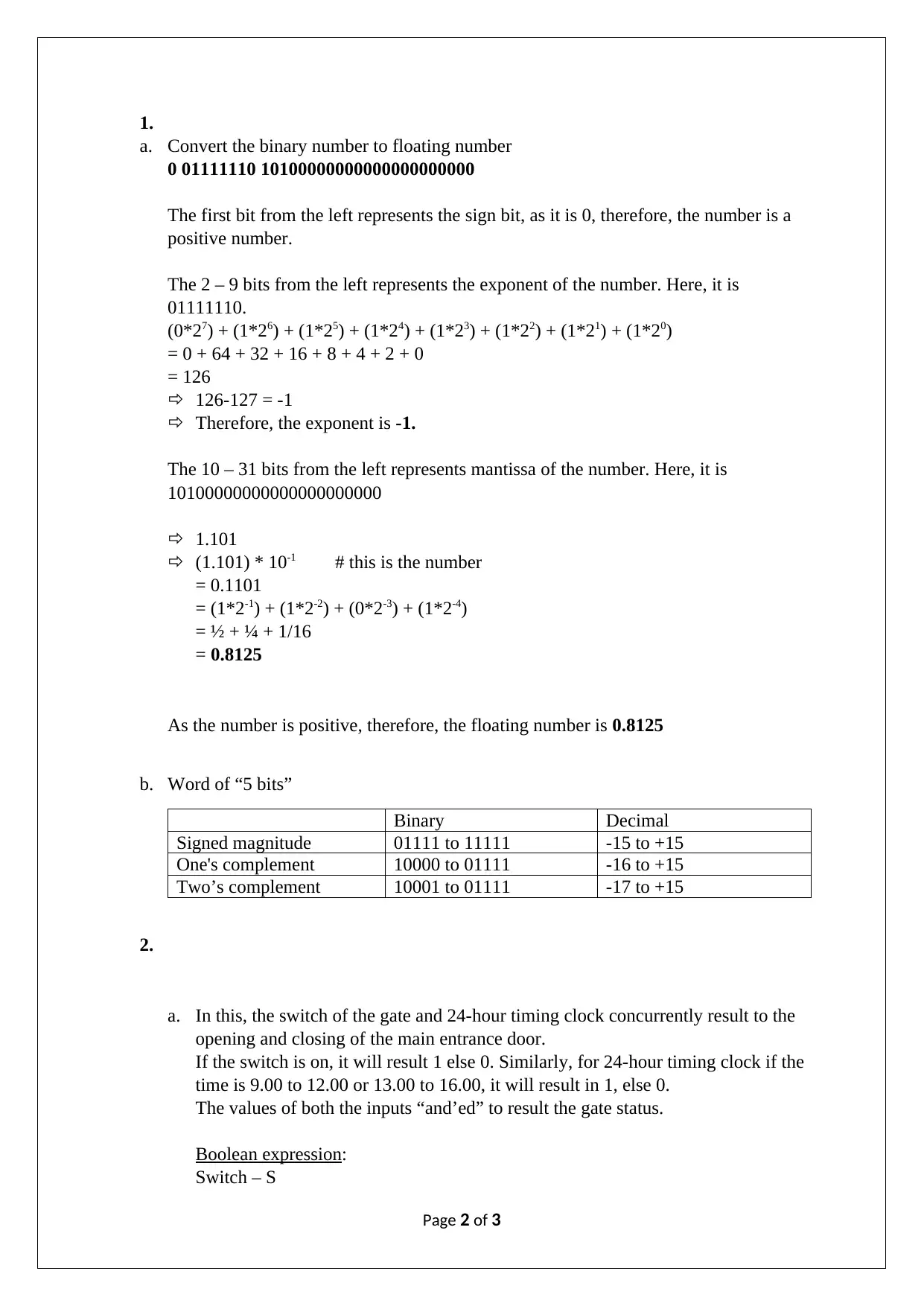

This document presents a complete solution to Assignment 1 for ITC544, focusing on data representation and digital logic. The solution includes the conversion of a binary number to a floating-point number, detailing the steps and calculations involved. It also addresses the analysis of a 5-bit word, exploring signed magnitude, one's complement, and two's complement representations. Furthermore, the assignment tackles a practical application involving a gate control system, defining the boolean expression, minimization, and a diagram for the system. Finally, the document provides a proof of a boolean expression using identities. This comprehensive solution helps students understand and solve complex problems in data representation and digital logic.

1 out of 3

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)