EE Project: Digital Alarm Clock Design and Implementation

VerifiedAdded on 2021/09/22

|4

|369

|90

Project

AI Summary

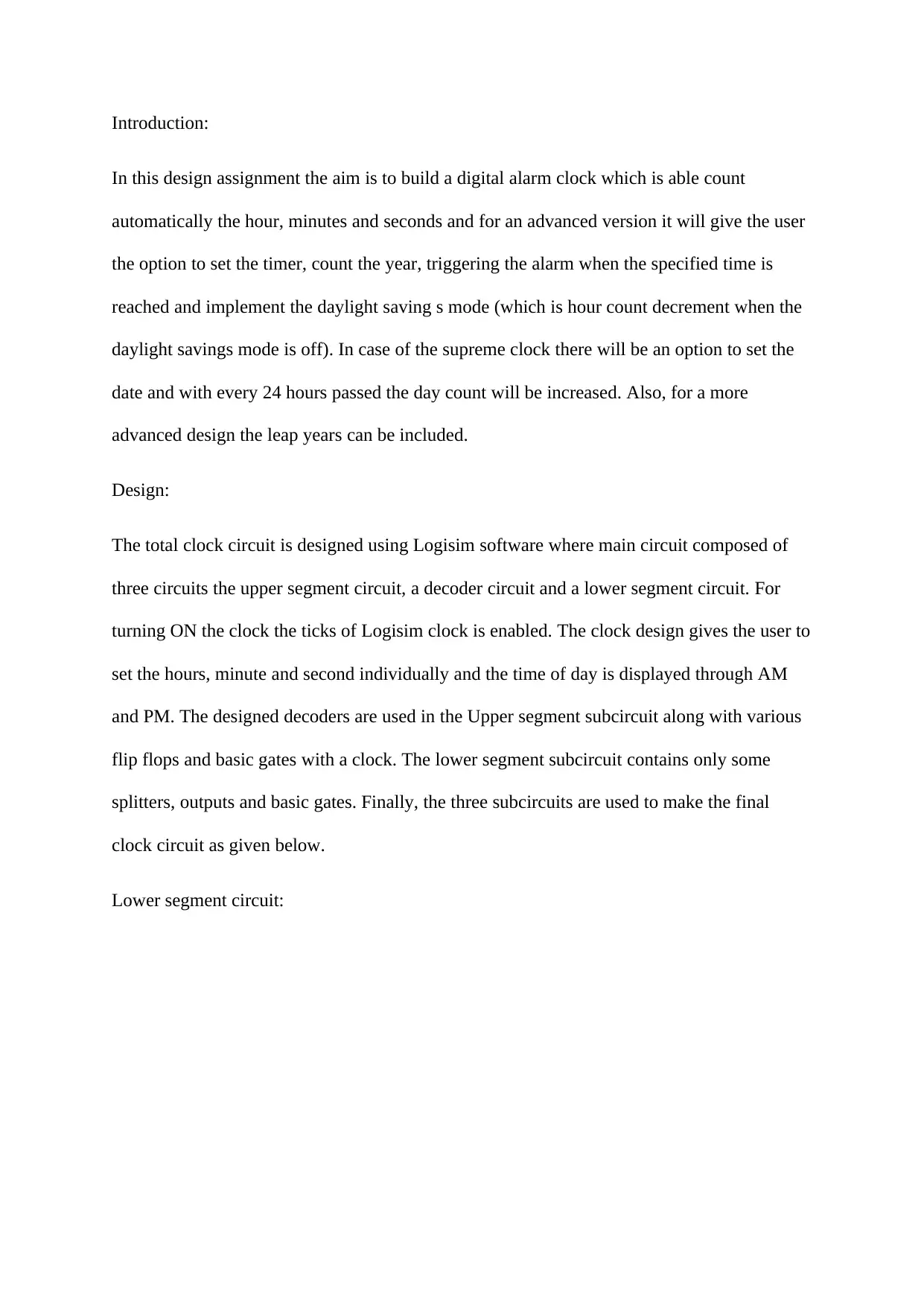

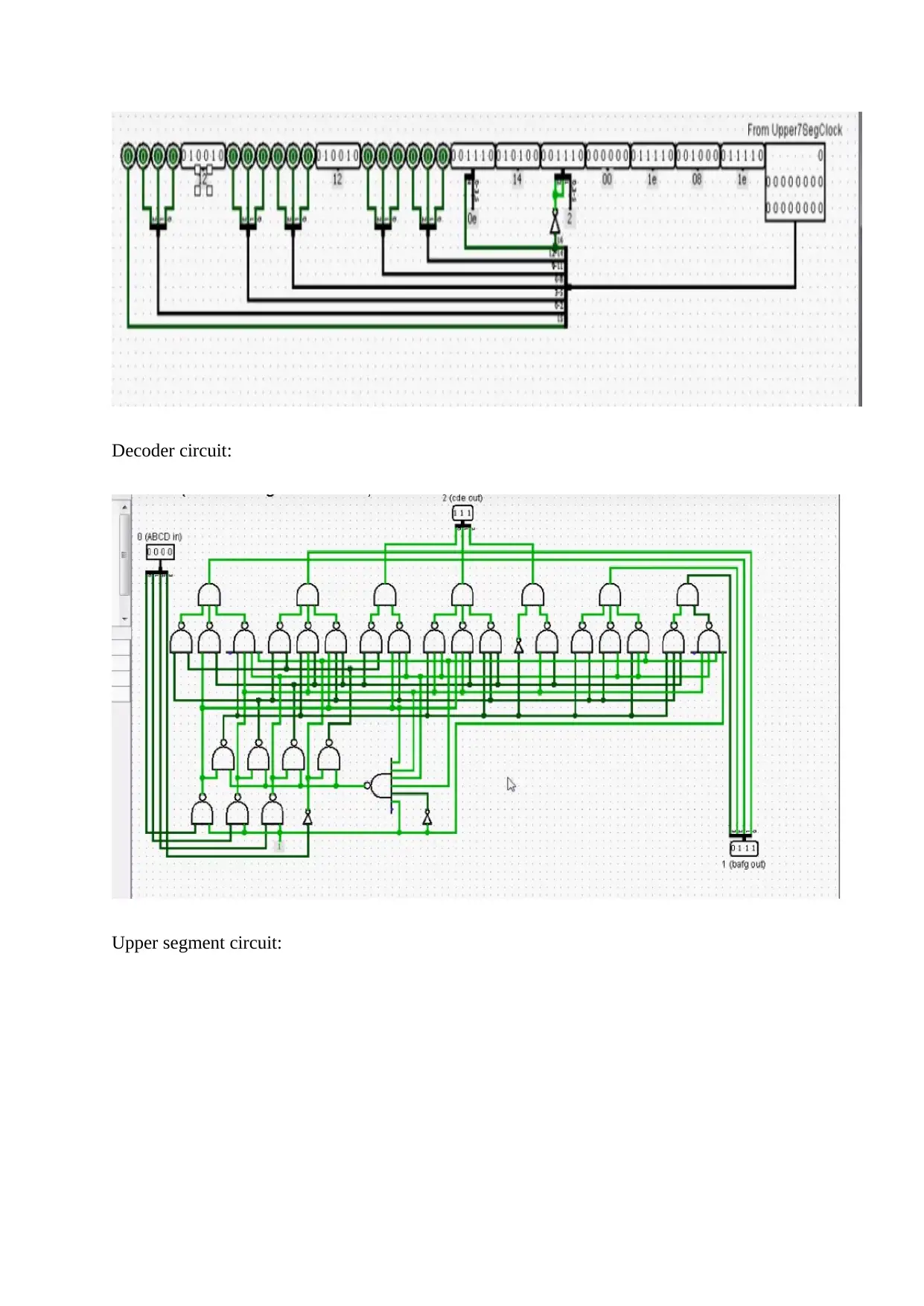

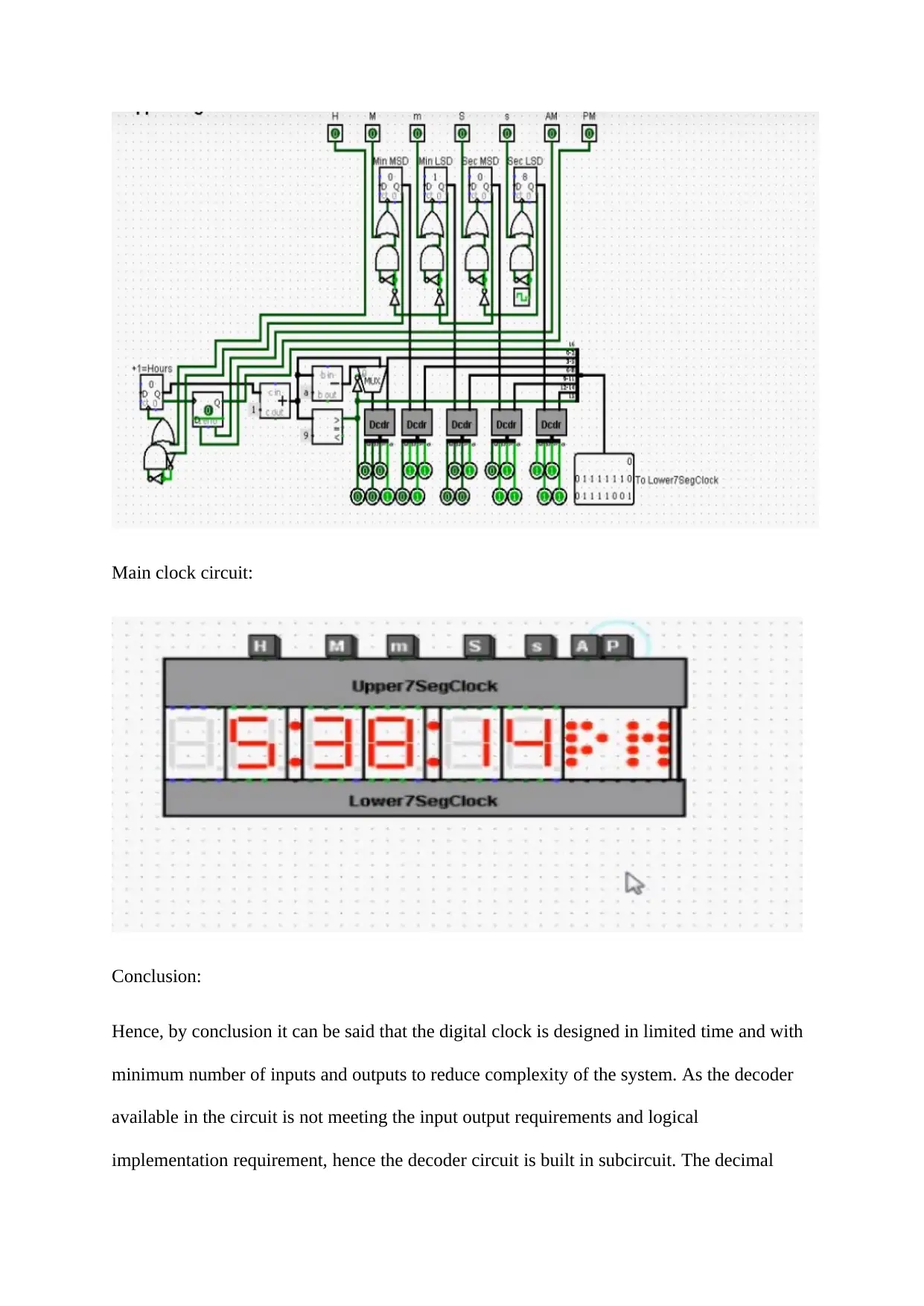

This project outlines the design of a digital alarm clock using Logisim software. The clock is designed to automatically count hours, minutes, and seconds, with advanced features including a settable timer, year count, alarm triggering, and daylight saving mode implementation. The design incorporates three main sub-circuits: an upper segment circuit, a decoder circuit, and a lower segment circuit. The clock allows users to set the hours, minutes, and seconds individually, with AM/PM display. The decoder circuit is custom-built due to the limitations of available decoders in Logisim. The decimal display of time is achieved using 7-segment displays and LED arrays. The design aims for simplicity and reduced complexity by minimizing the number of inputs and outputs. The design can be further enhanced to include calendar year, alarm display, and other advanced features.

1 out of 4

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)