CEN 211: Digital Logic Design I - Digital Clock Design Project

VerifiedAdded on 2022/09/07

|3

|398

|42

Project

AI Summary

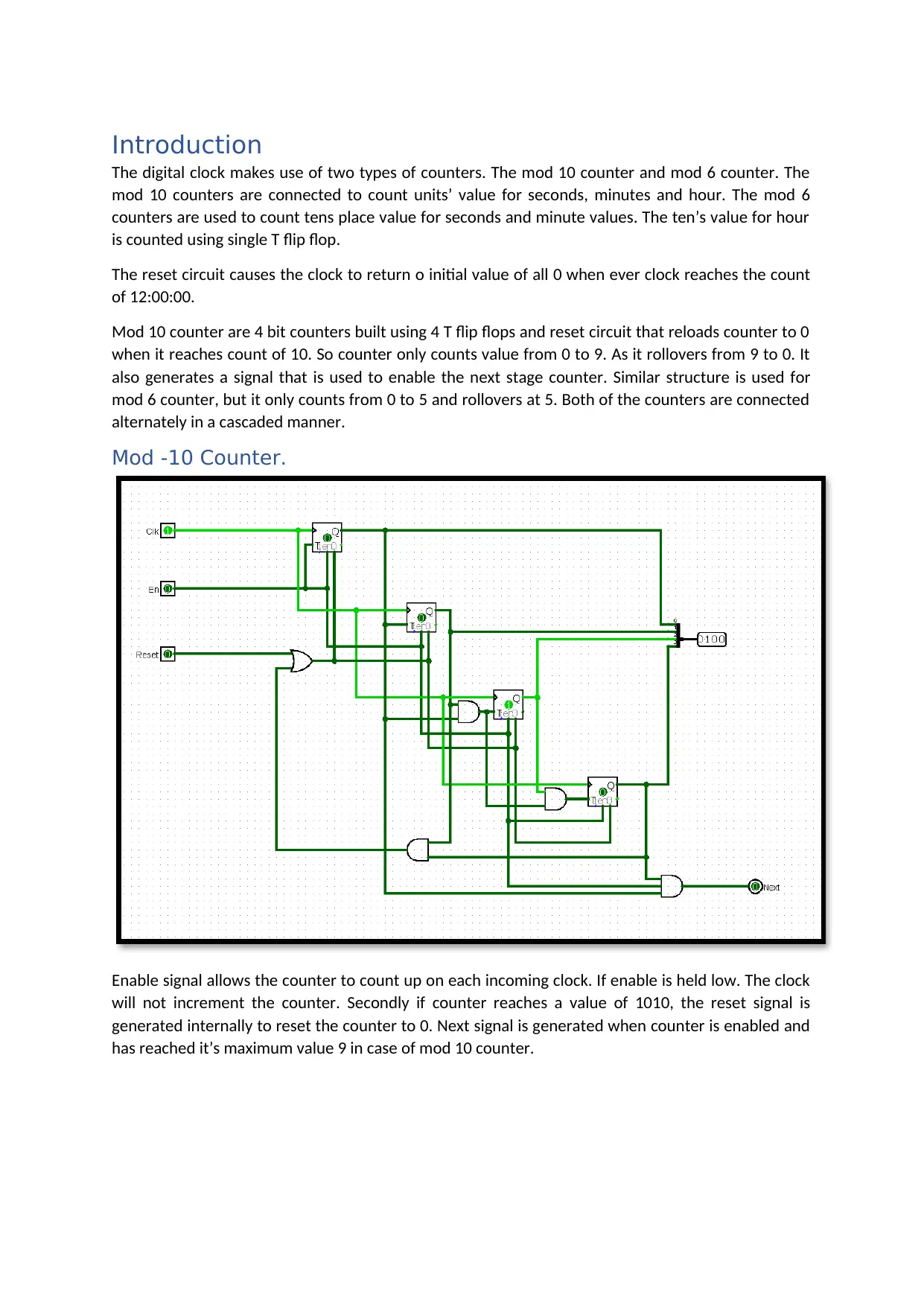

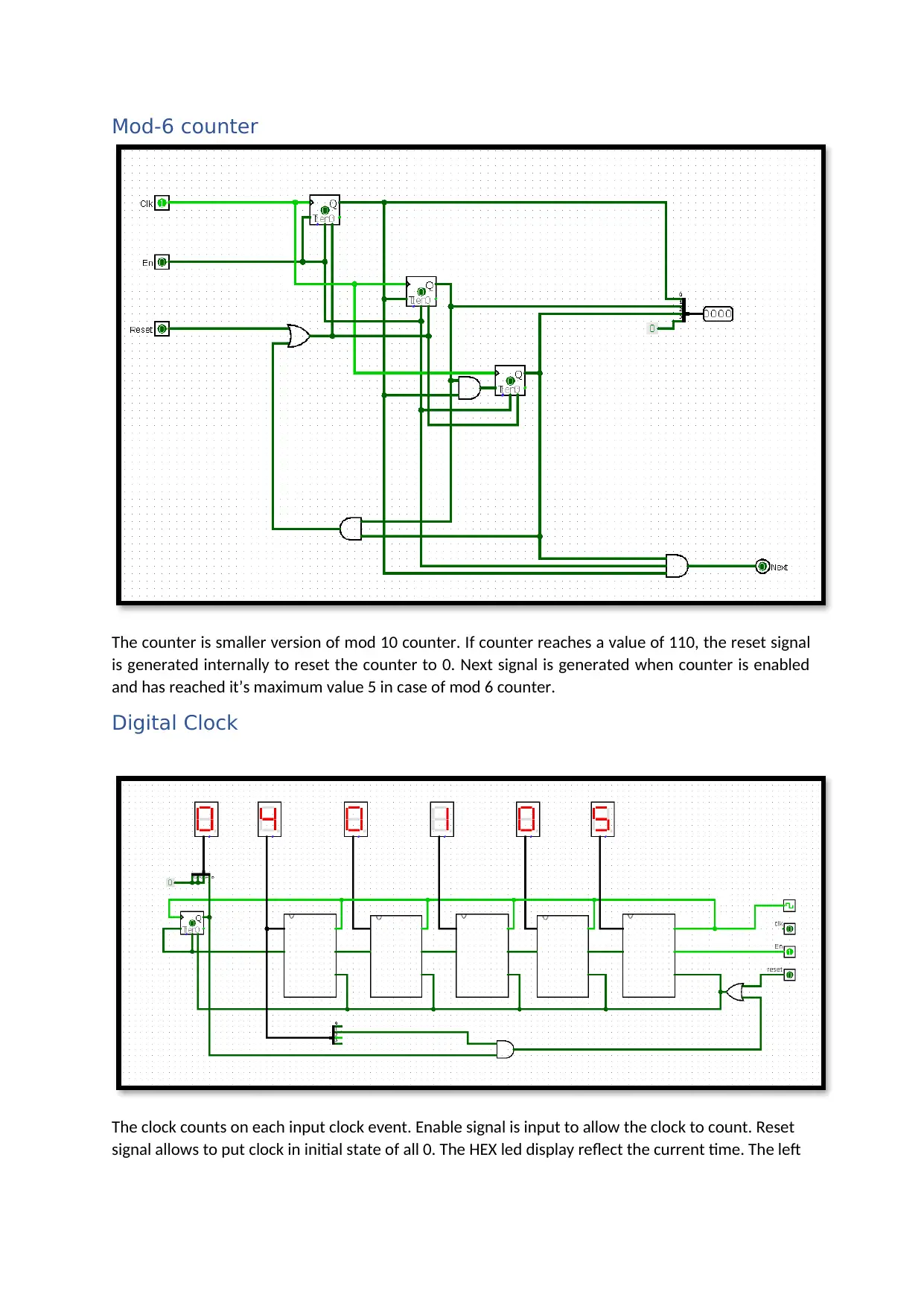

This assignment presents a comprehensive solution for a digital clock design project, addressing the requirements of CEN 211 at King Saud University. The project involves designing a 12-hour digital clock using Logisim software. The solution details the implementation of mod-10 and mod-6 counters, explaining their functionality and integration with 7-segment displays. The design optimizes the circuit for gate input cost and includes the use of T flip-flops. The document also describes the reset mechanism, which ensures the clock resets to 12:00:00. The solution includes a detailed explanation of the clock's operation, including the role of enable signals and the display of hours, minutes, and seconds on the HEX LED display. The document provides a complete, step-by-step guide to designing a digital clock, making it a valuable resource for students studying digital logic design.

1 out of 3

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)