ECE Lab: Identifying Properties of Synchronous Counter Circuit

VerifiedAdded on 2023/04/24

|5

|747

|249

Practical Assignment

AI Summary

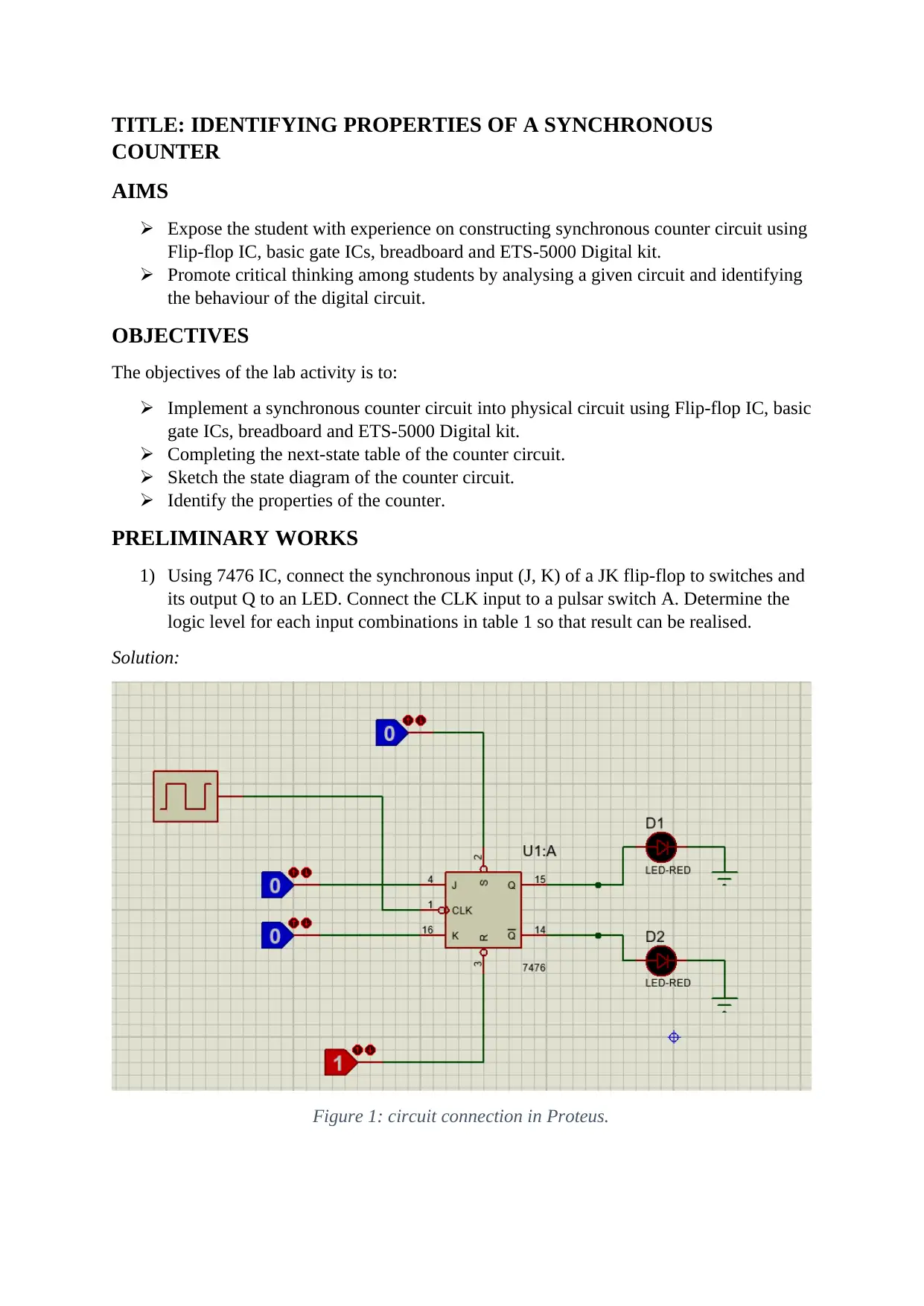

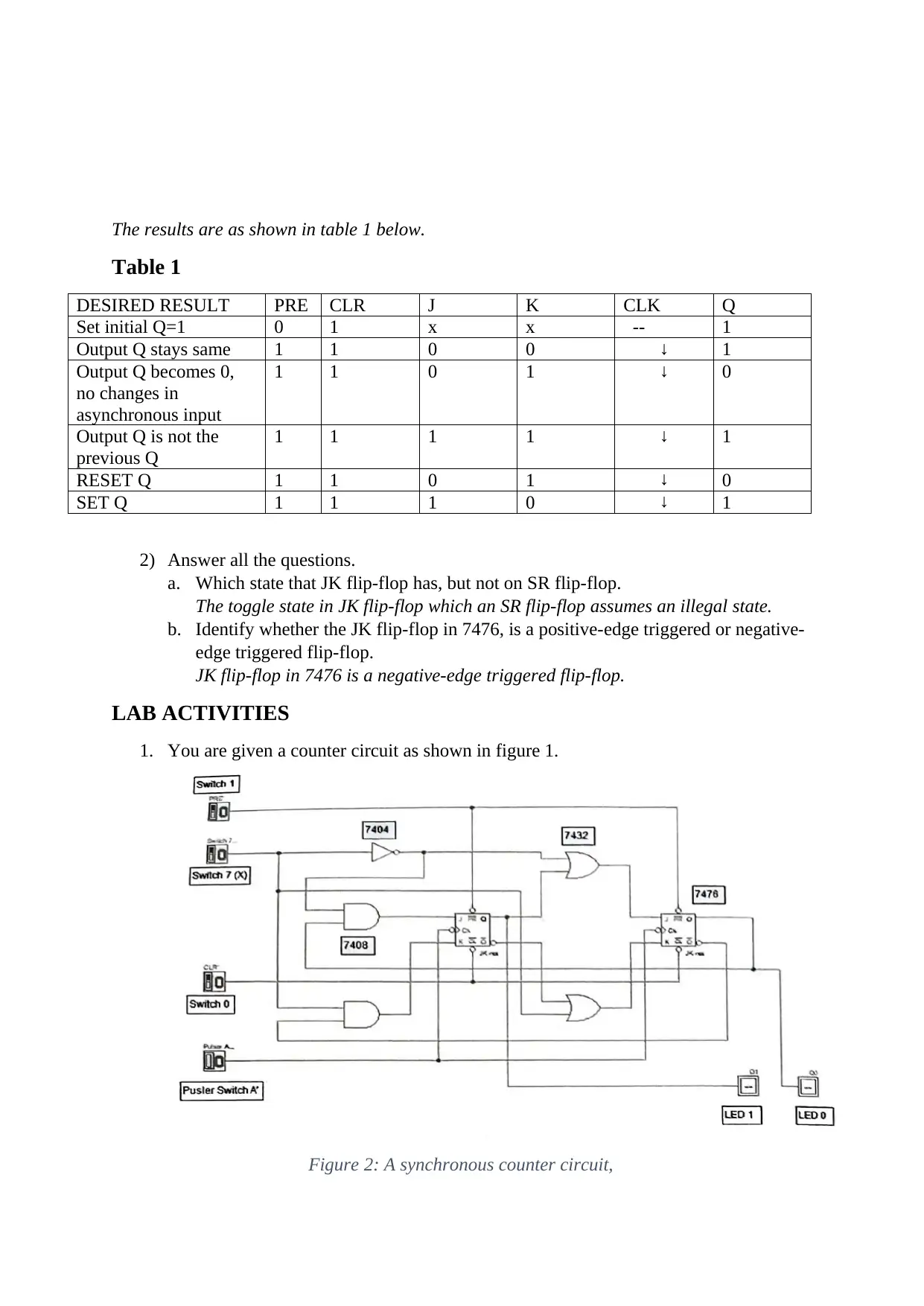

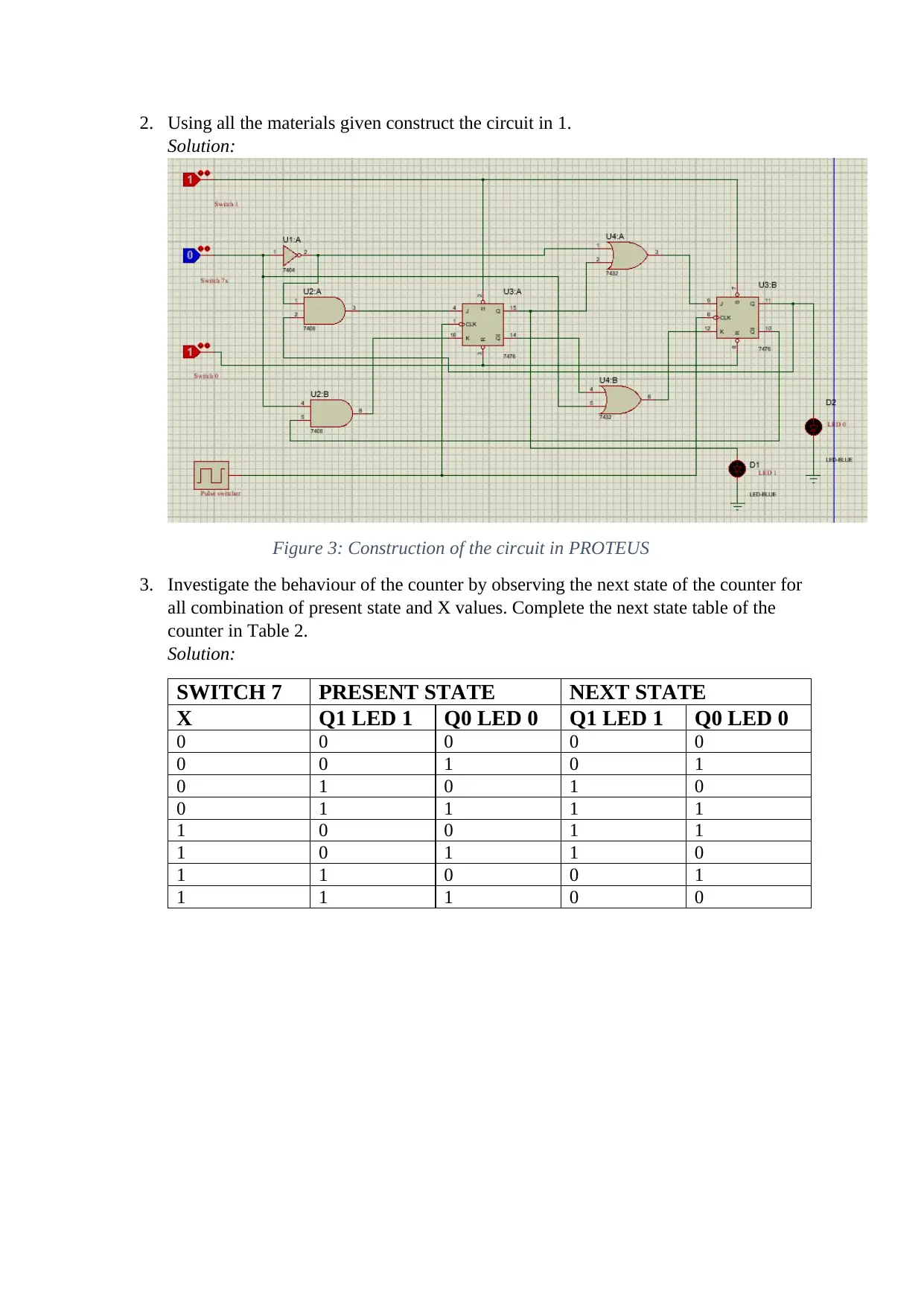

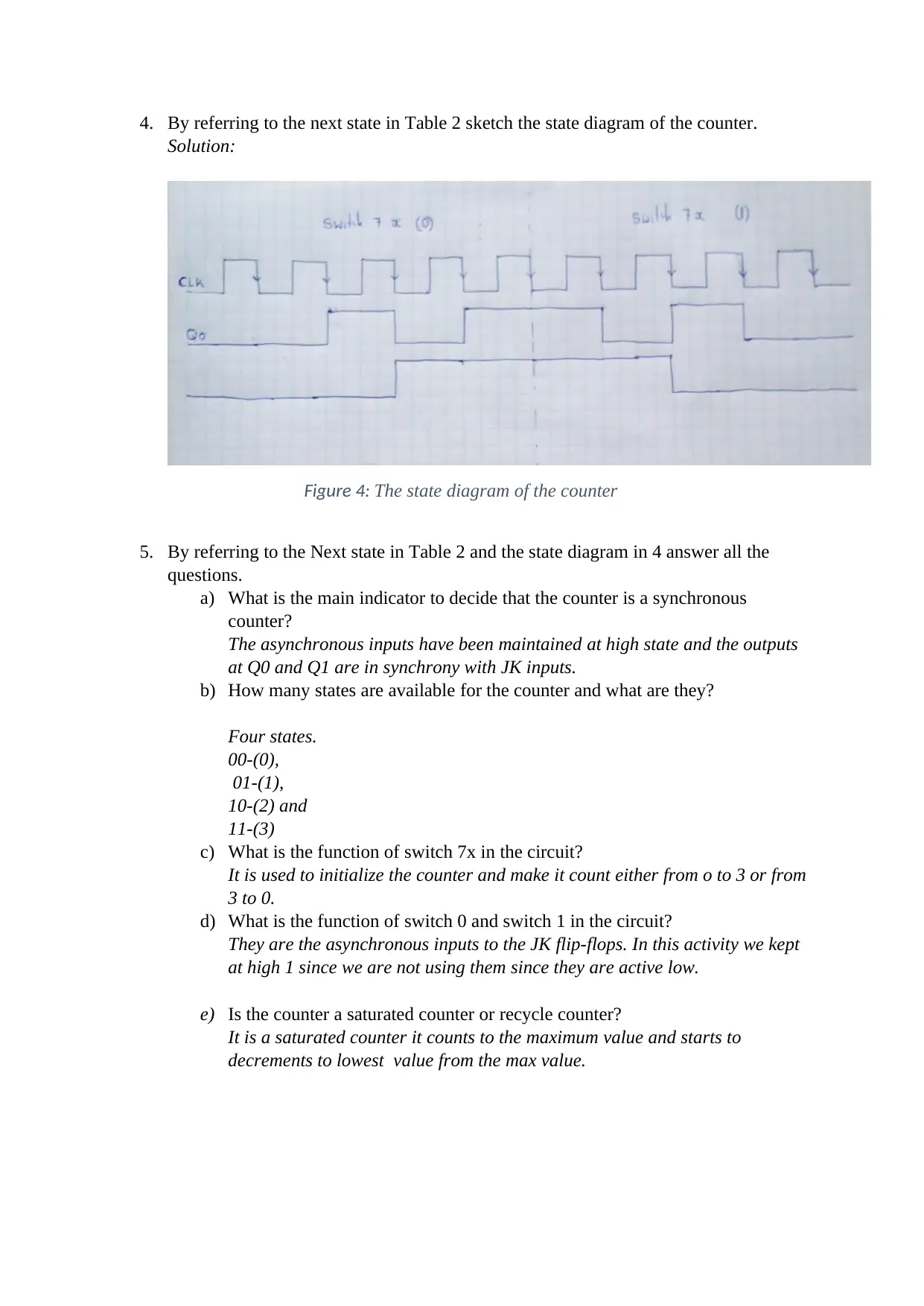

This practical assignment focuses on identifying the properties of a synchronous counter through a hands-on lab experiment. The experiment involves constructing a synchronous counter circuit using JK flip-flop ICs, basic gate ICs, a breadboard, and an ETS-5000 Digital kit. The objectives include implementing the circuit, completing the next-state table, sketching the state diagram, and identifying the counter's properties. The preliminary works involve understanding the behavior of a JK flip-flop and its differences from an SR flip-flop. The lab activities include constructing the counter circuit, investigating its behavior by observing the next state for all combinations of present state and input values, completing the next state table, sketching the state diagram, and answering questions about the counter's characteristics, such as whether it's synchronous, the number of available states, and the function of different switches in the circuit. The report concludes by identifying the counter as a saturated counter.

1 out of 5

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)