Electrical Engineering: Data Representation and Digital Logic Homework

VerifiedAdded on 2020/05/16

|8

|695

|87

Homework Assignment

AI Summary

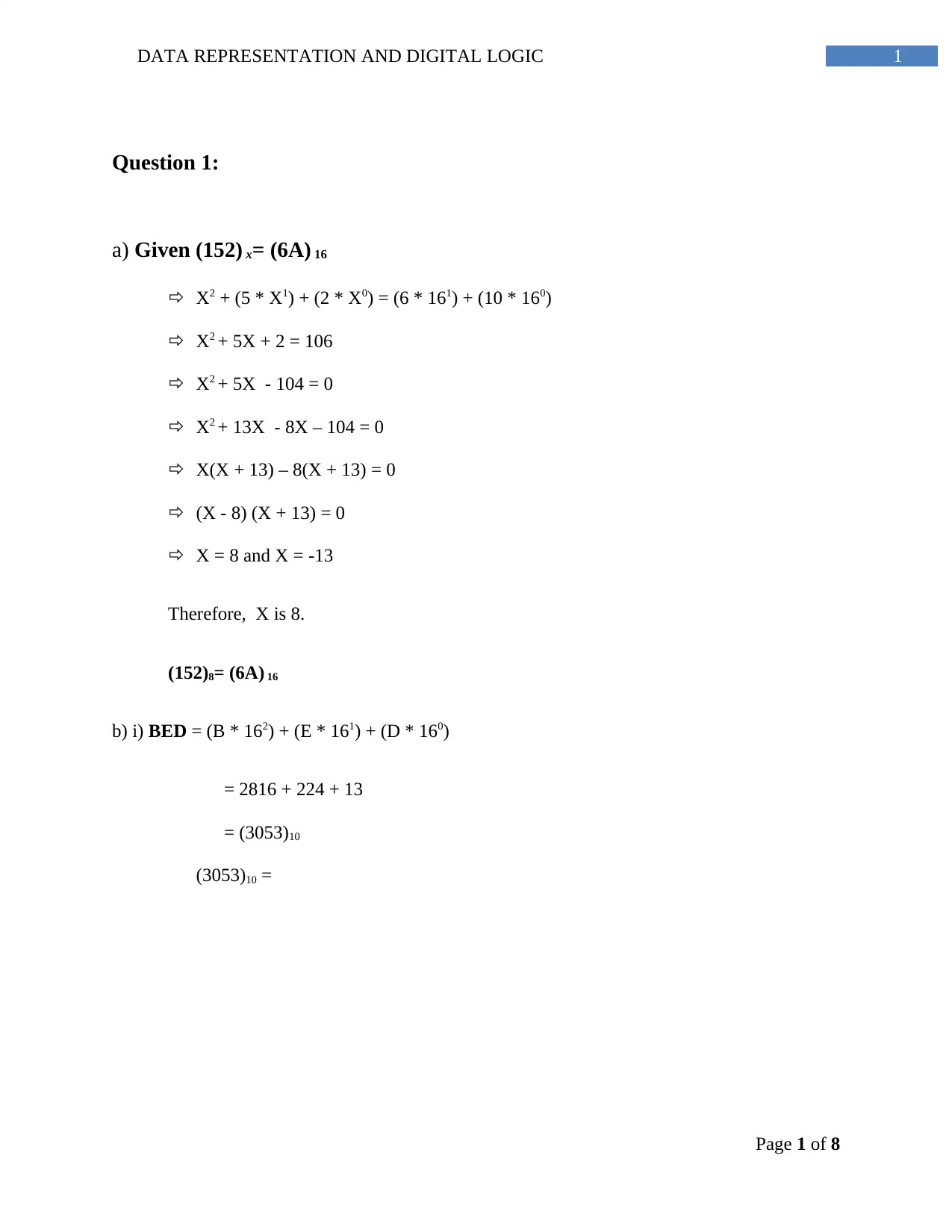

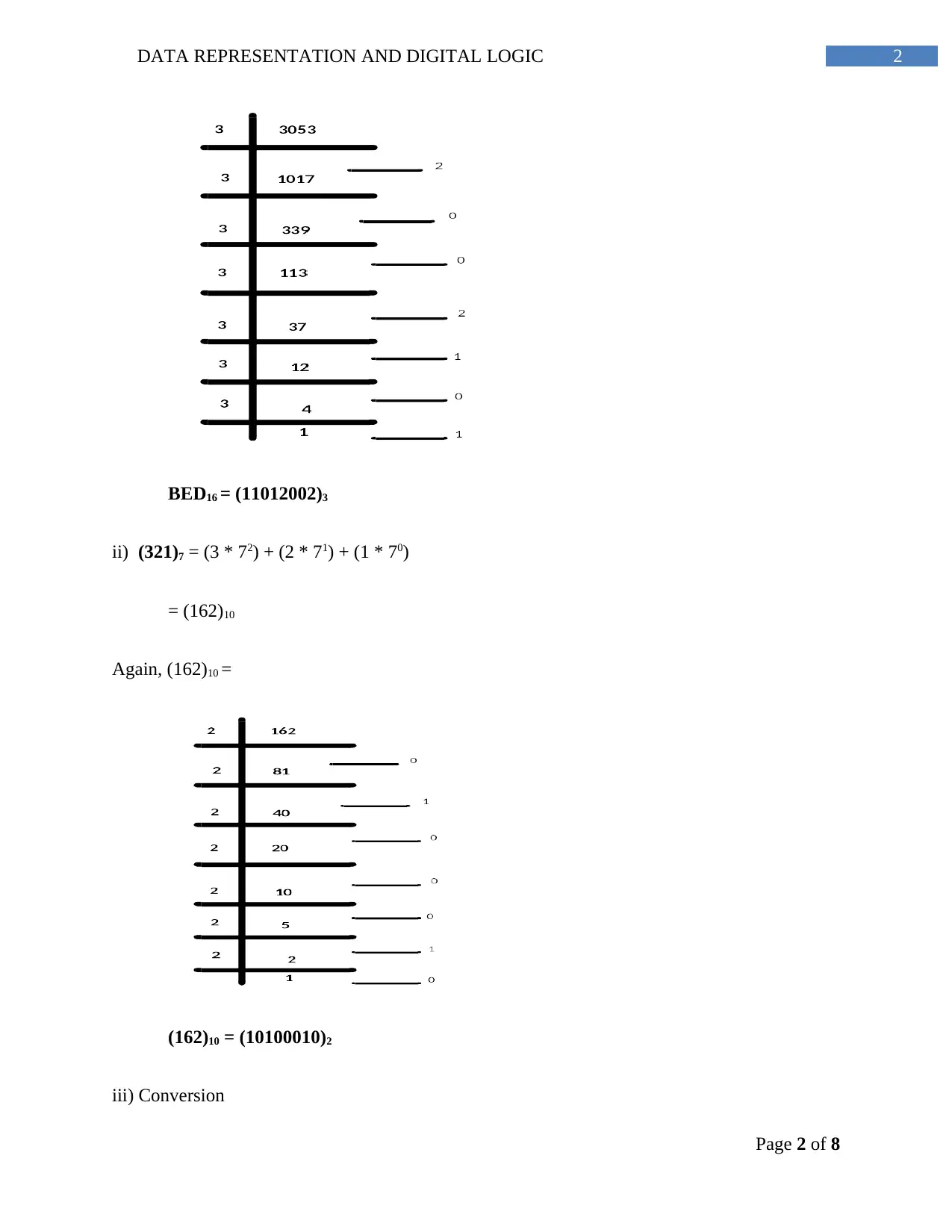

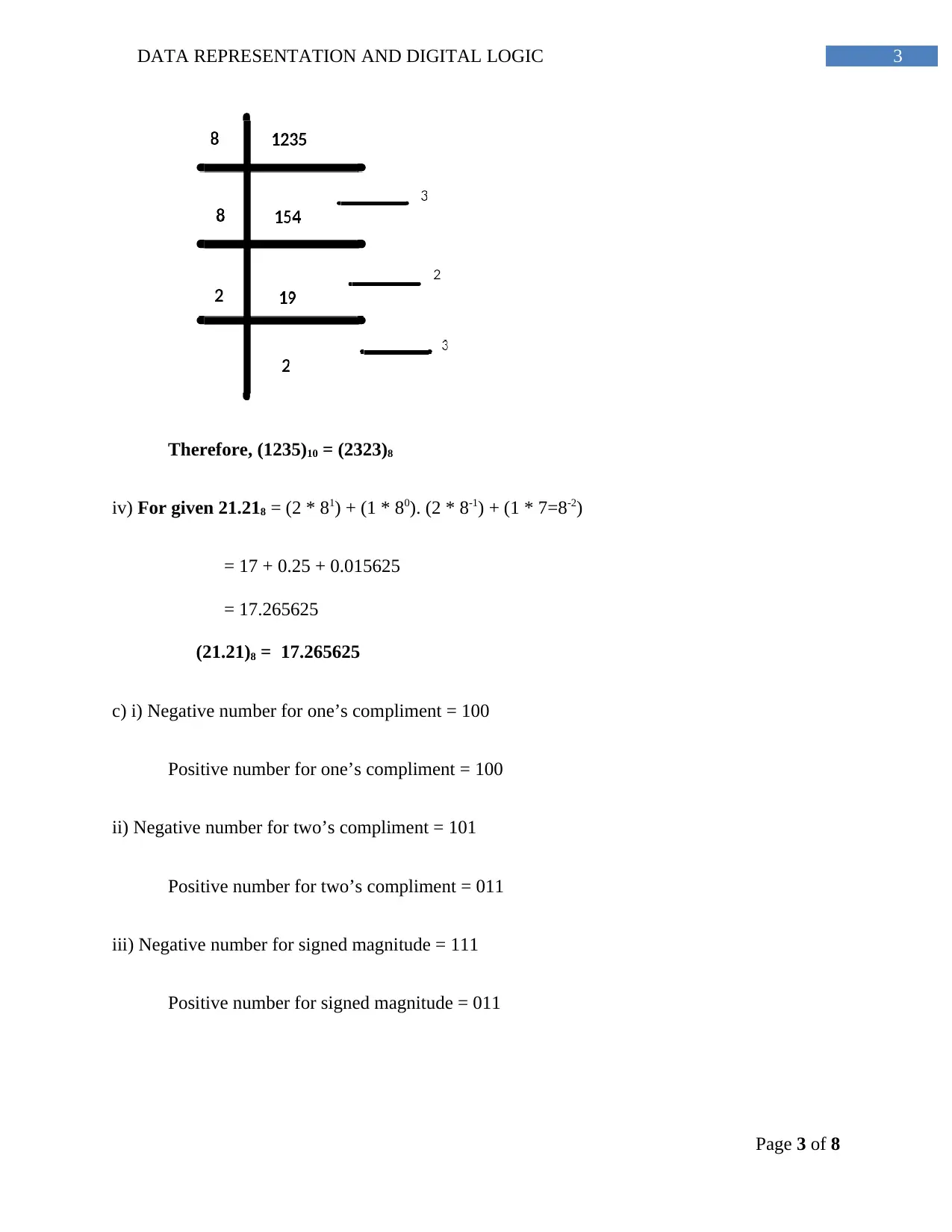

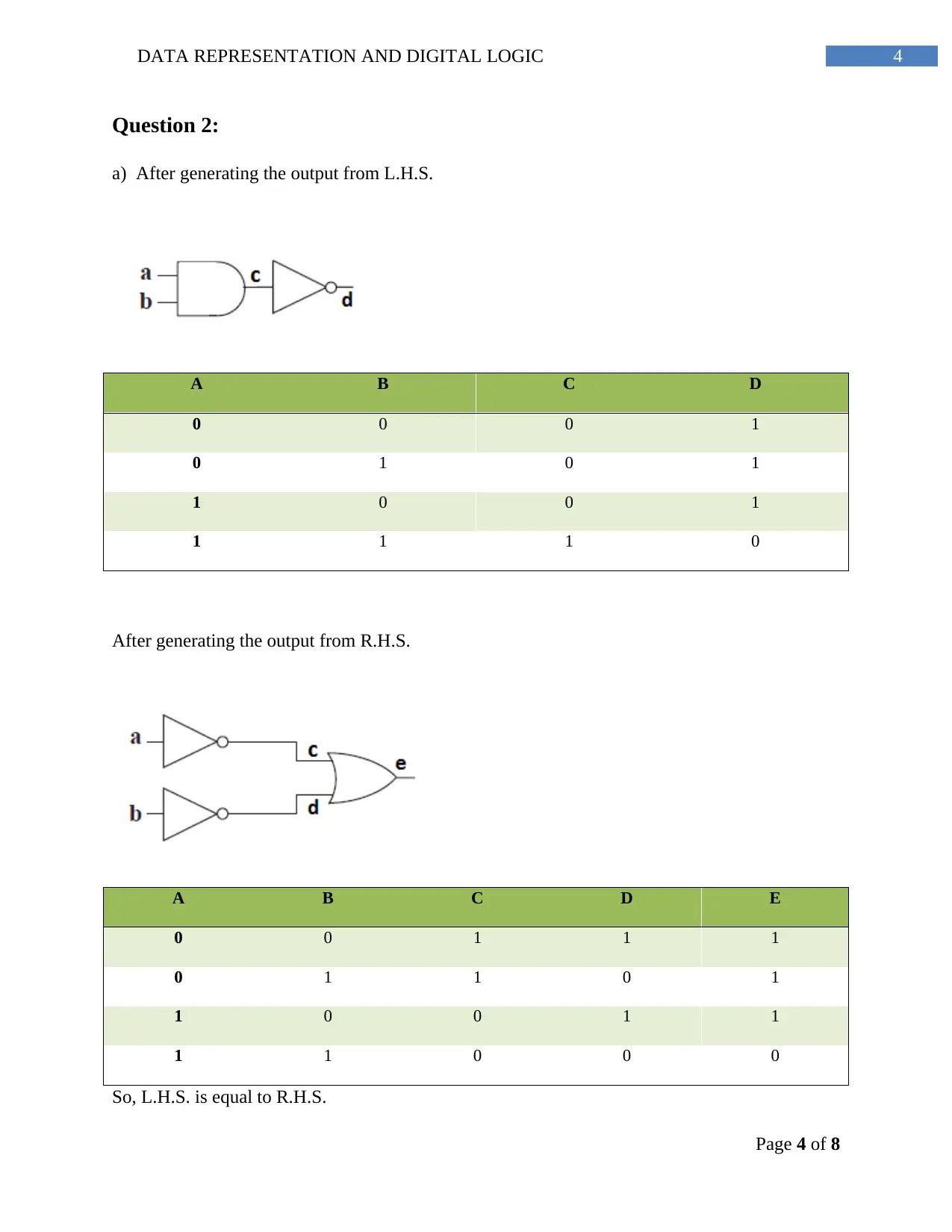

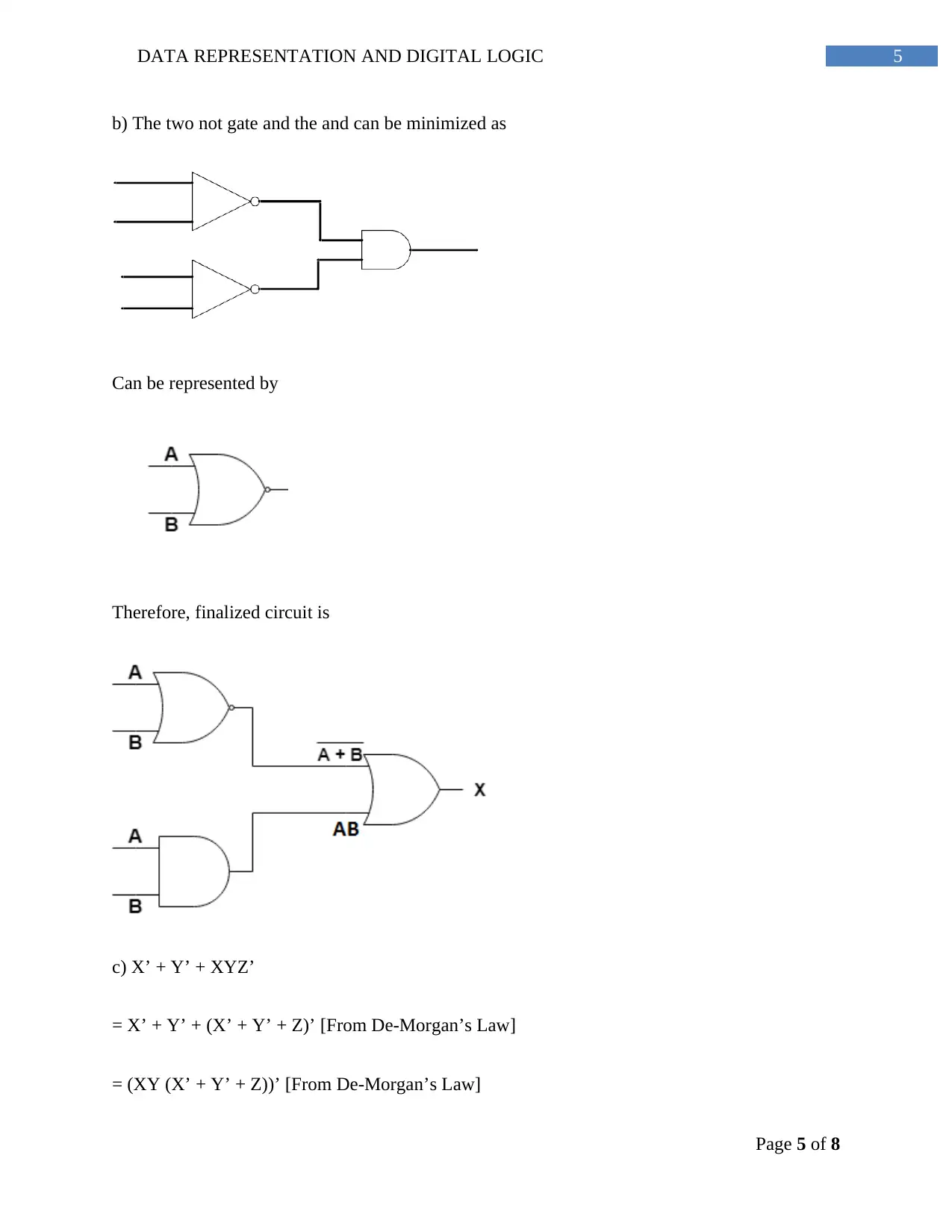

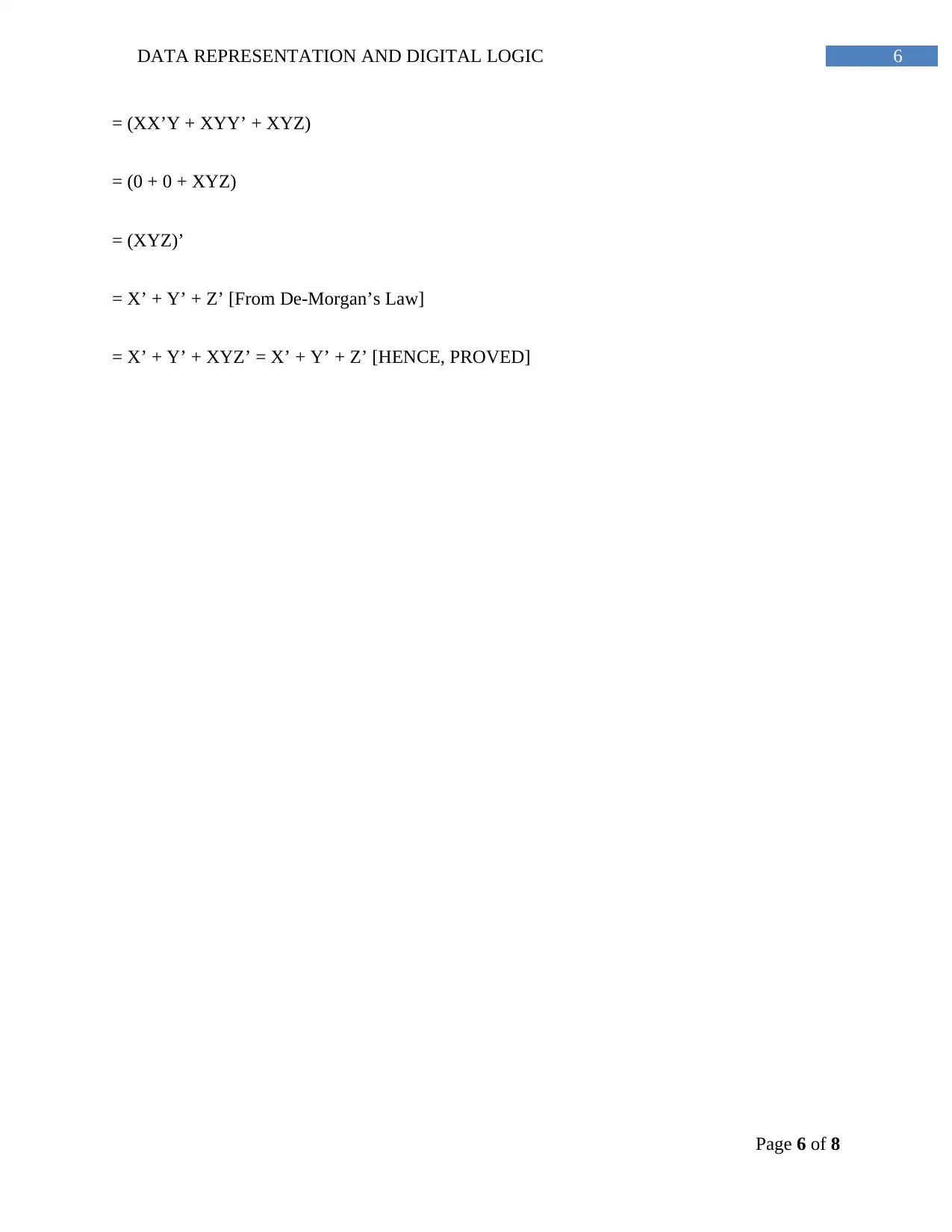

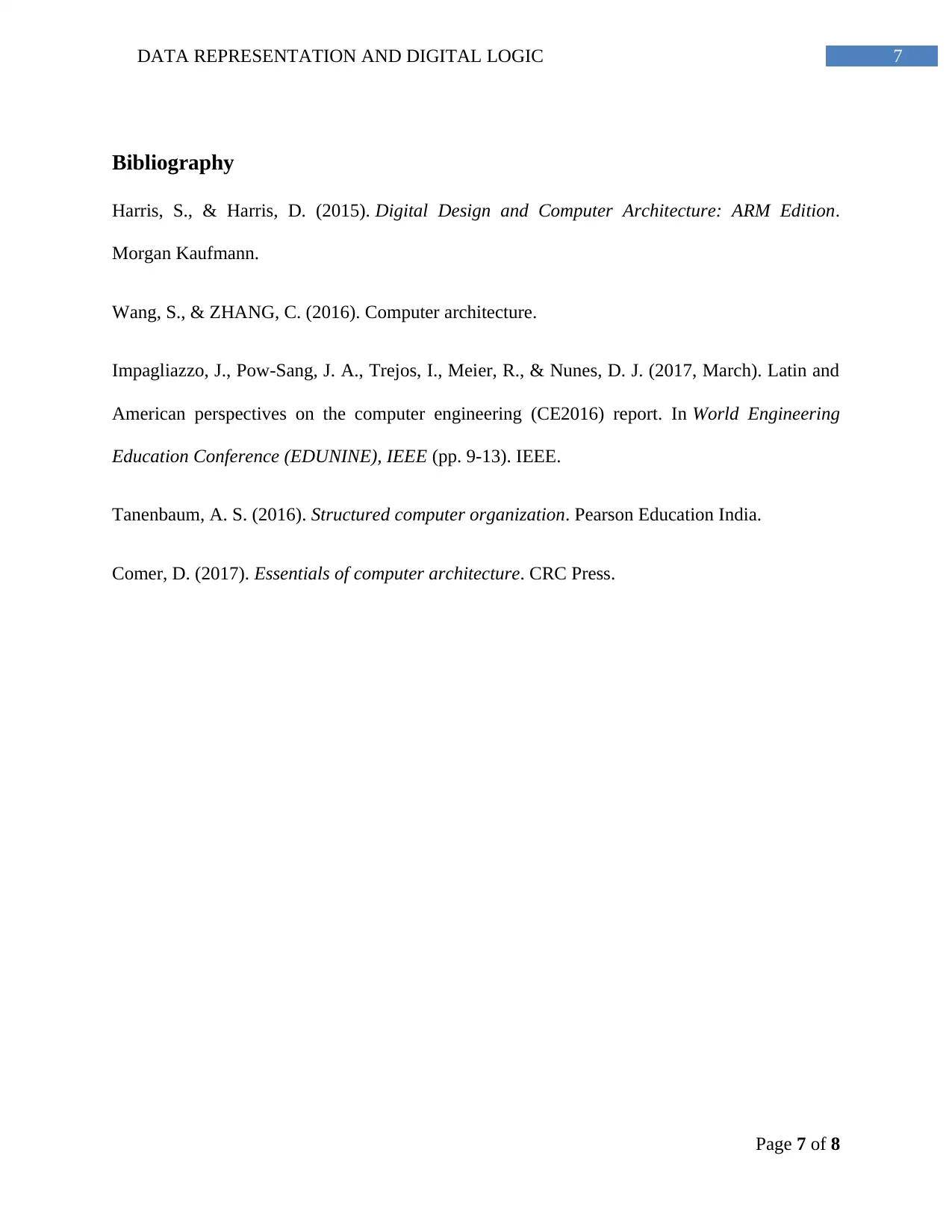

This assignment solution delves into the core concepts of data representation and digital logic. It begins with number system conversions, including converting between hexadecimal, base-8, and binary formats, and converting fractional numbers. The solution then explores complement representations, including one's complement, two's complement, and signed magnitude, analyzing the representation of positive and negative numbers. Furthermore, the assignment covers Boolean algebra, demonstrating the equivalence of logical expressions using truth tables and De Morgan's Law. The solution includes circuit simplification using logic gates, and the final part of the assignment provides a concise bibliography of relevant resources such as books on computer architecture and digital design.

1 out of 8

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)