1007ICT/7611ICT Computer Systems: Elevator Logic Circuit Design

VerifiedAdded on 2023/01/23

|6

|1194

|63

Practical Assignment

AI Summary

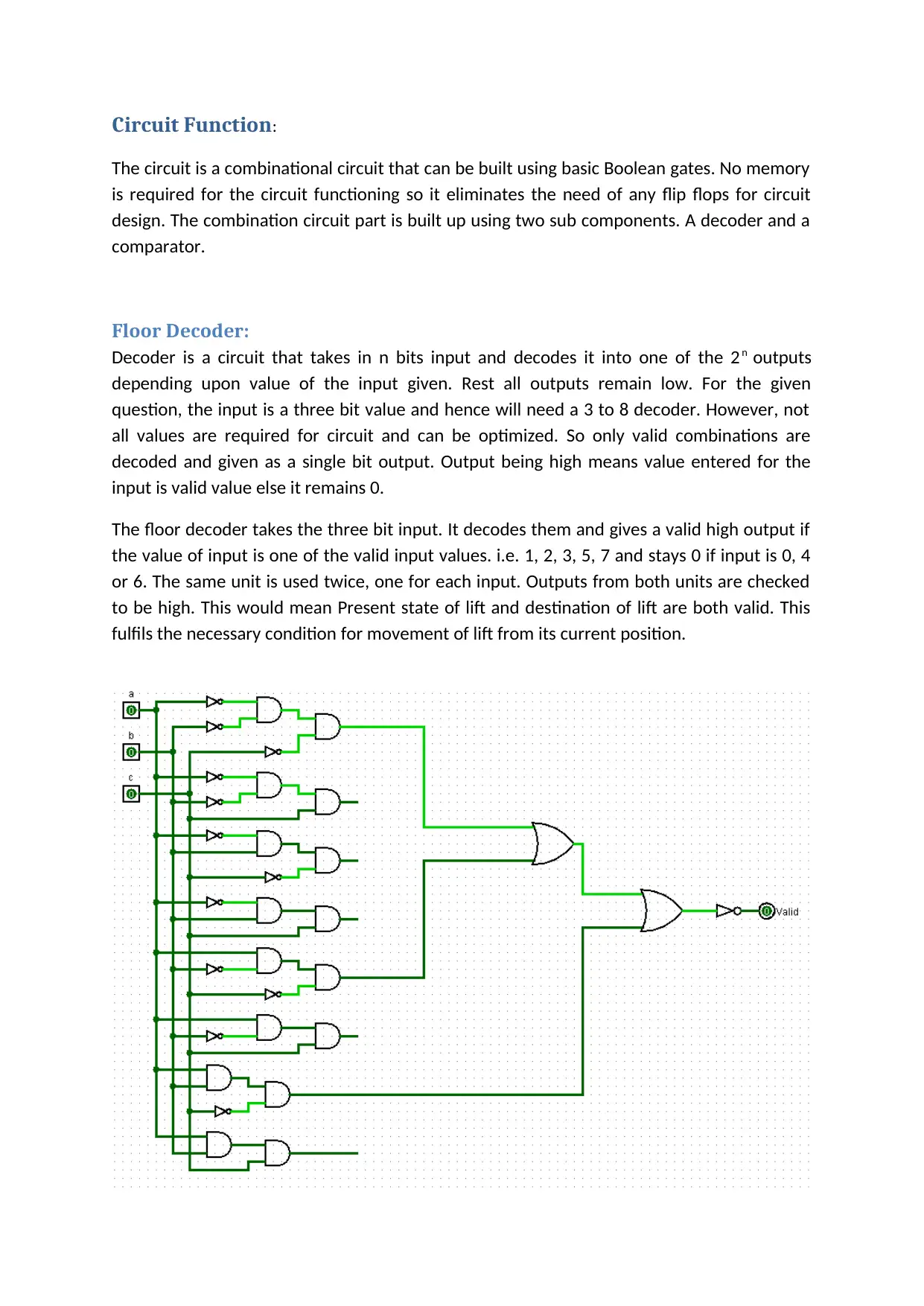

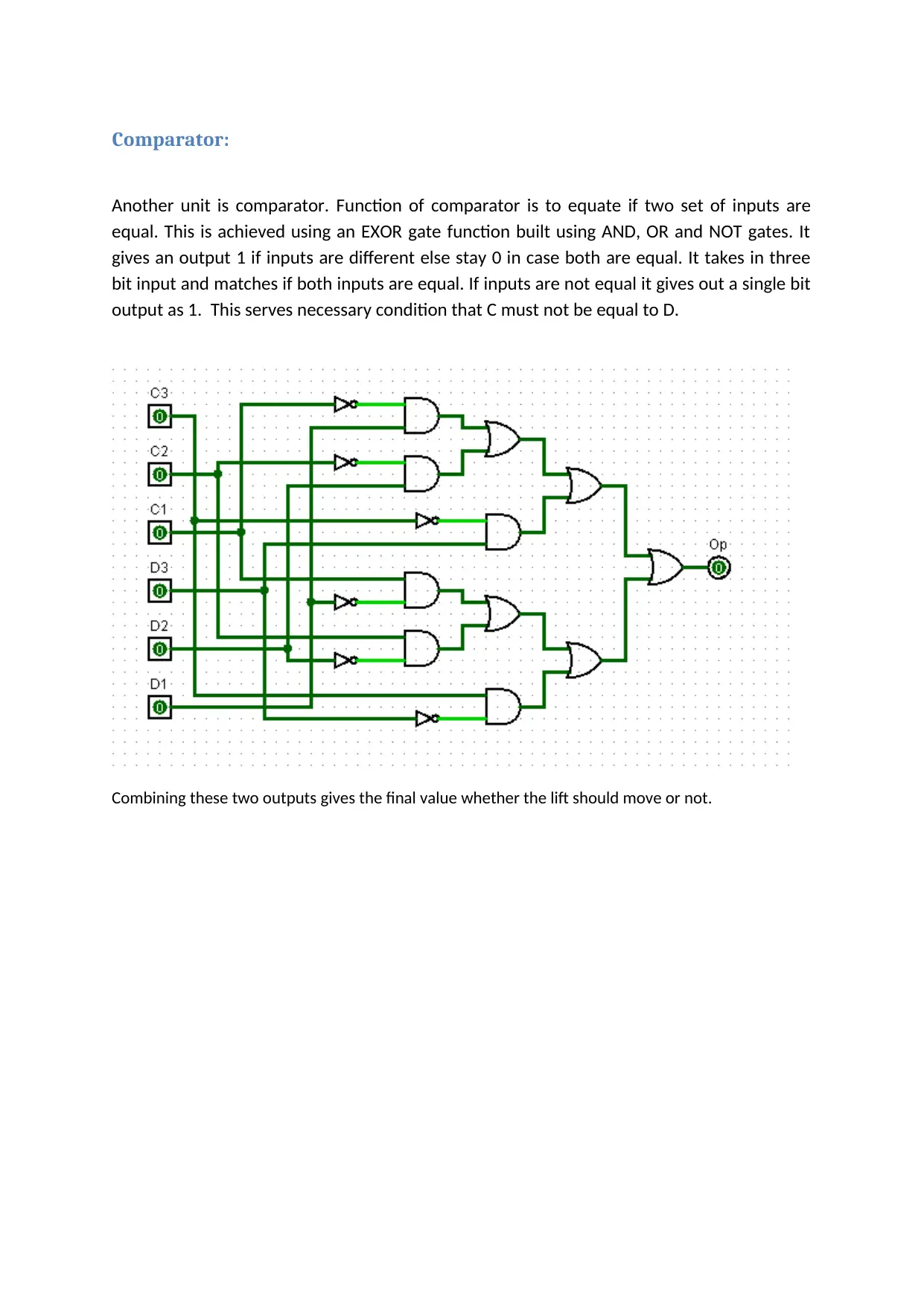

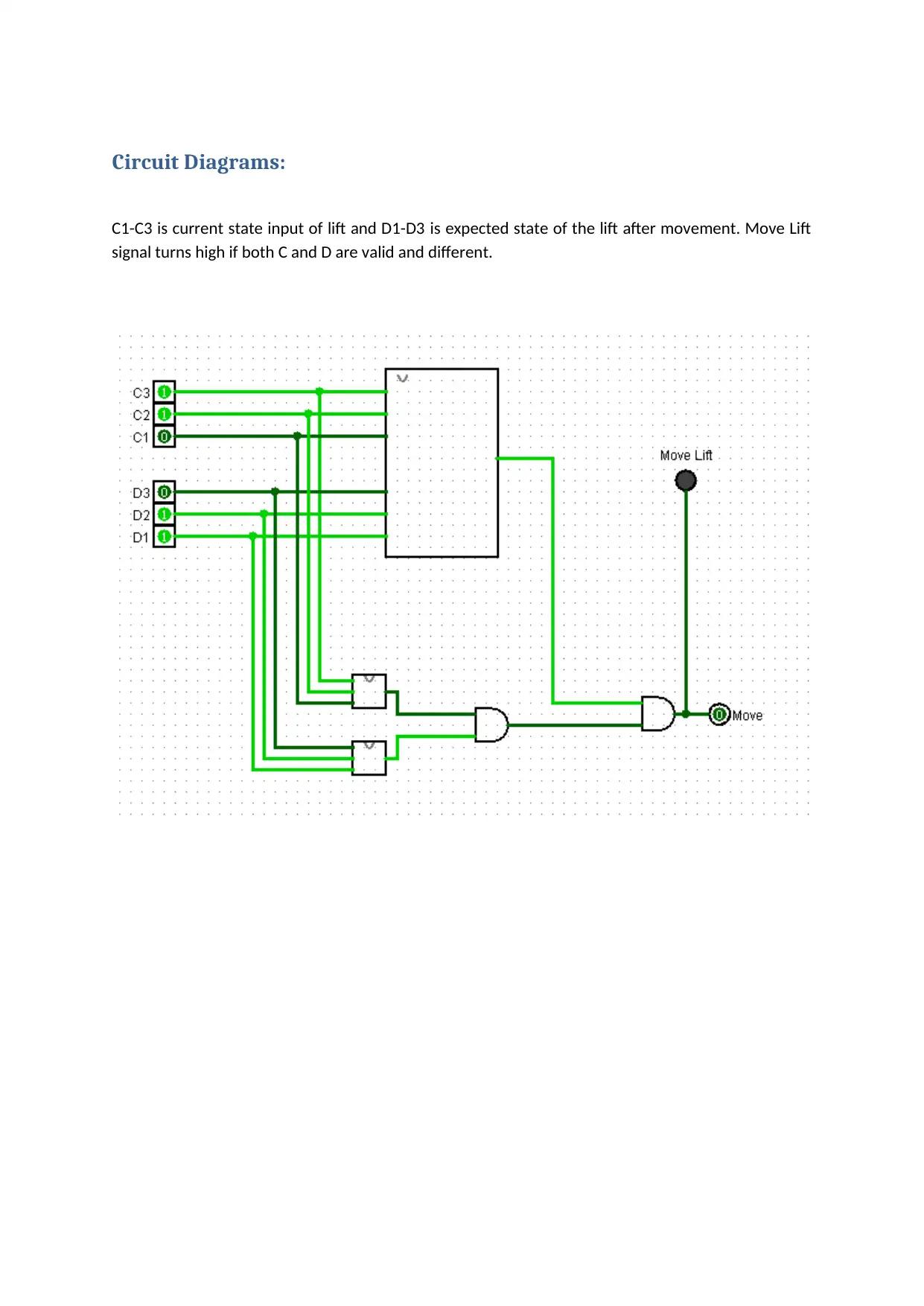

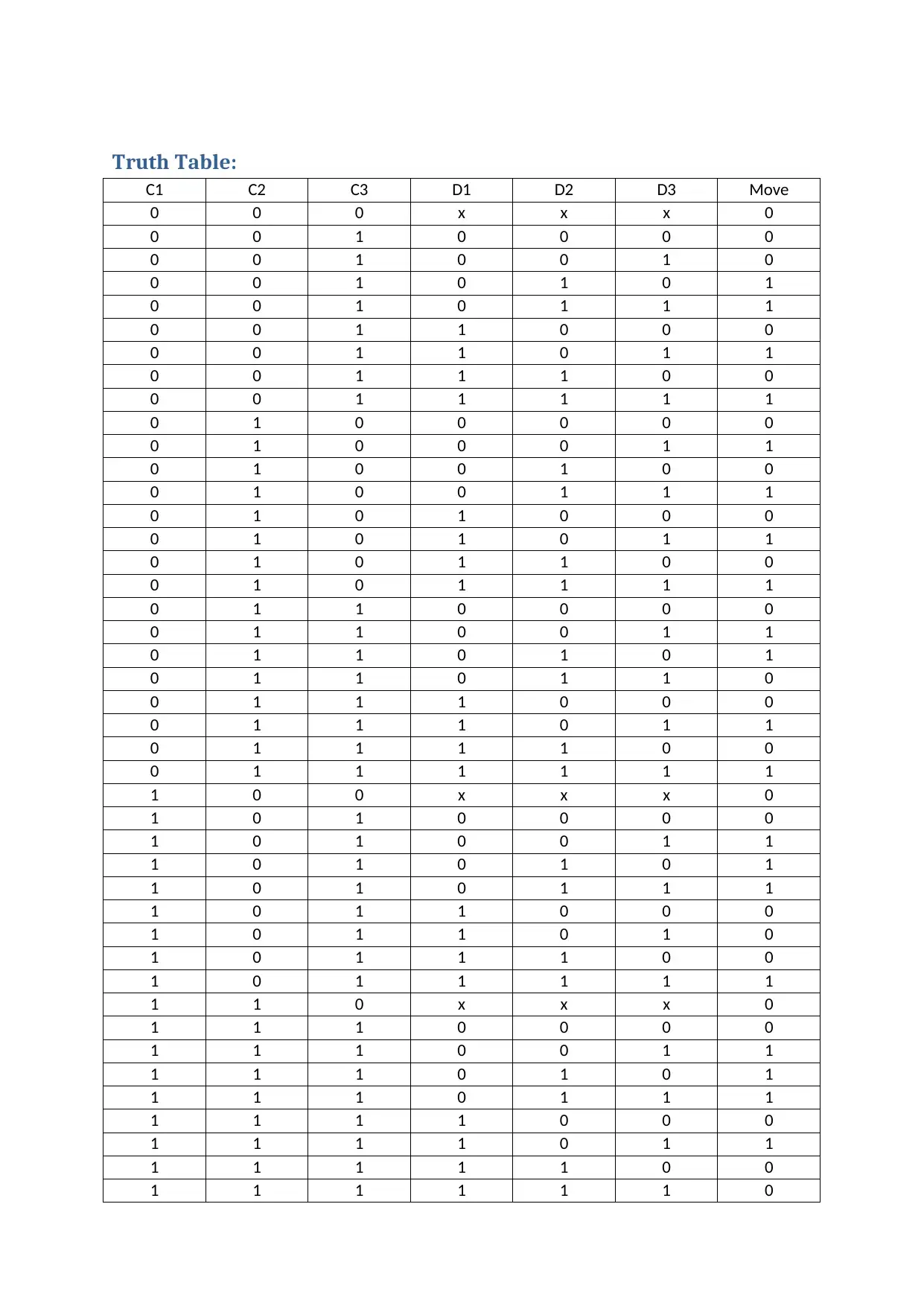

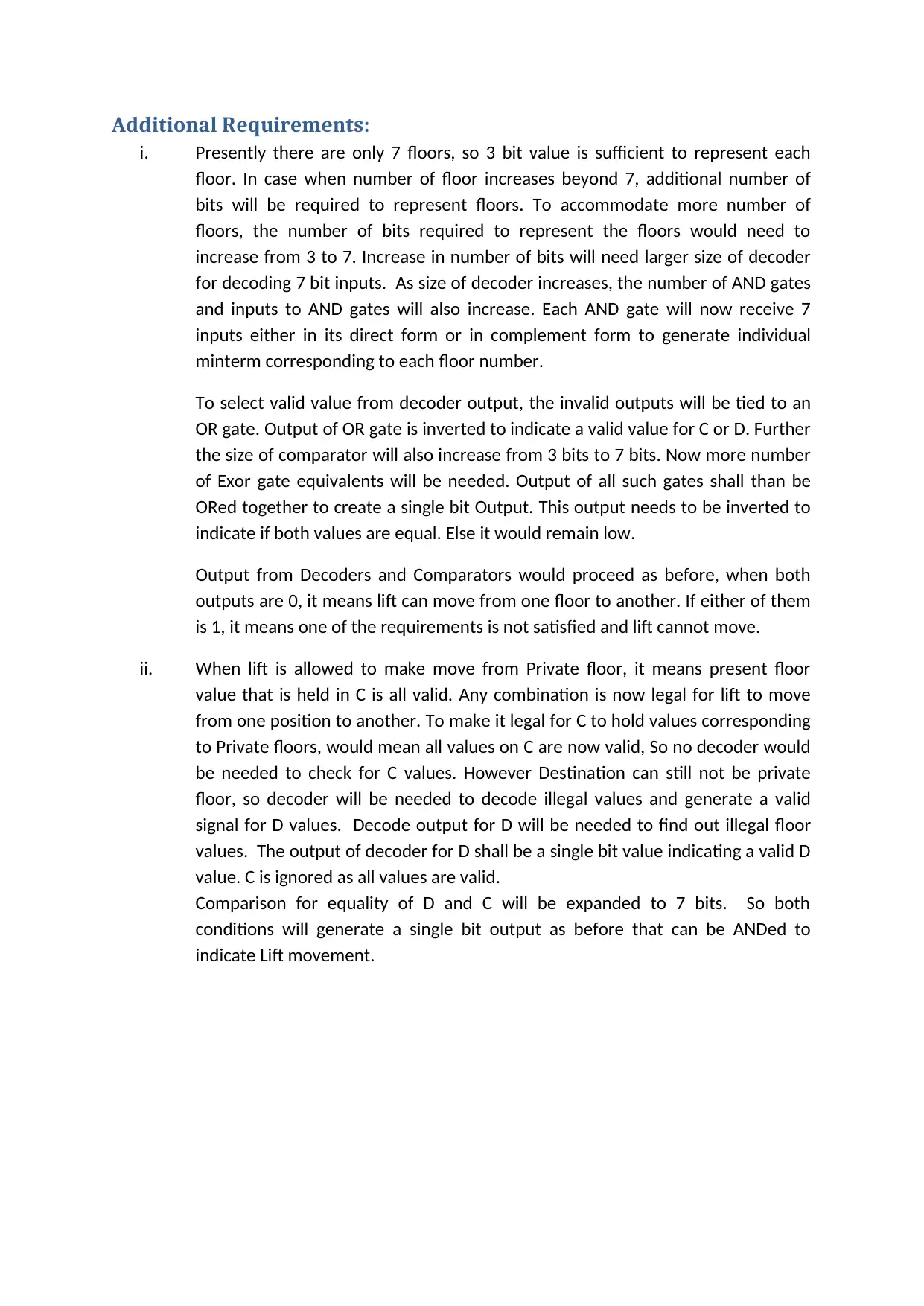

This document details the design and functionality of a combinational elevator logic circuit, implemented using basic Boolean gates and avoiding the use of flip-flops. The circuit utilizes a decoder and a comparator as its core components. The decoder, specifically a 3-to-8 decoder, is employed to validate input values representing the current and destination floors. The comparator, built with EXOR gates, checks for equality between the current and destination floors. The document includes a truth table, circuit diagrams, and explanations of the circuit's behavior. It also addresses the adaptation of the circuit to accommodate more floors, increasing the number of bits and expanding the decoder and comparator sizes. Furthermore, it explores the scenario where the lift is allowed to move from private floors, modifying the decoder's role and the comparator's function. This assignment demonstrates a practical application of digital logic principles for elevator control systems.

1 out of 6

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)