ITC544 Assignment 1: Data Representation, Digital Logic Analysis

VerifiedAdded on 2019/10/31

|4

|909

|180

Homework Assignment

AI Summary

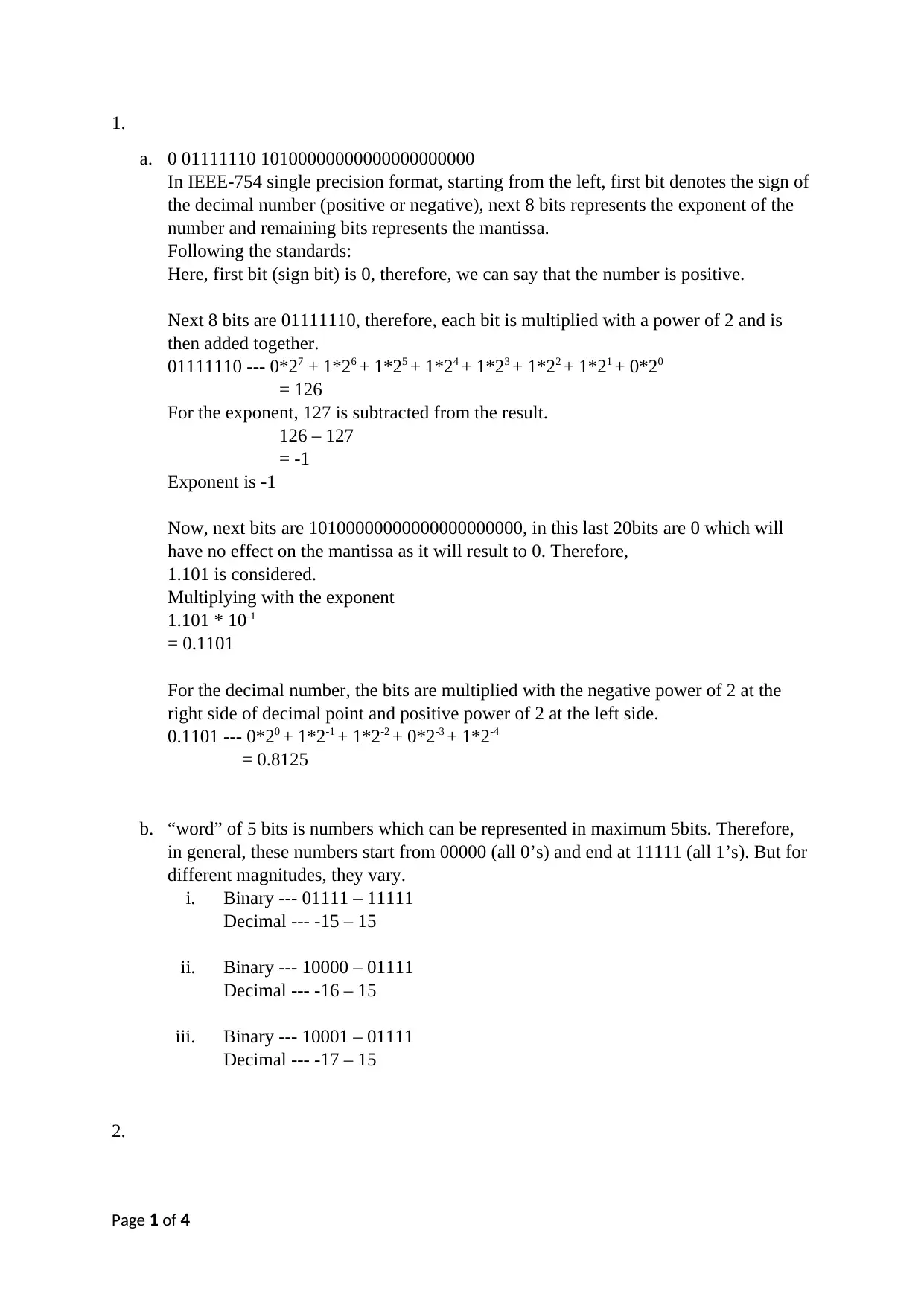

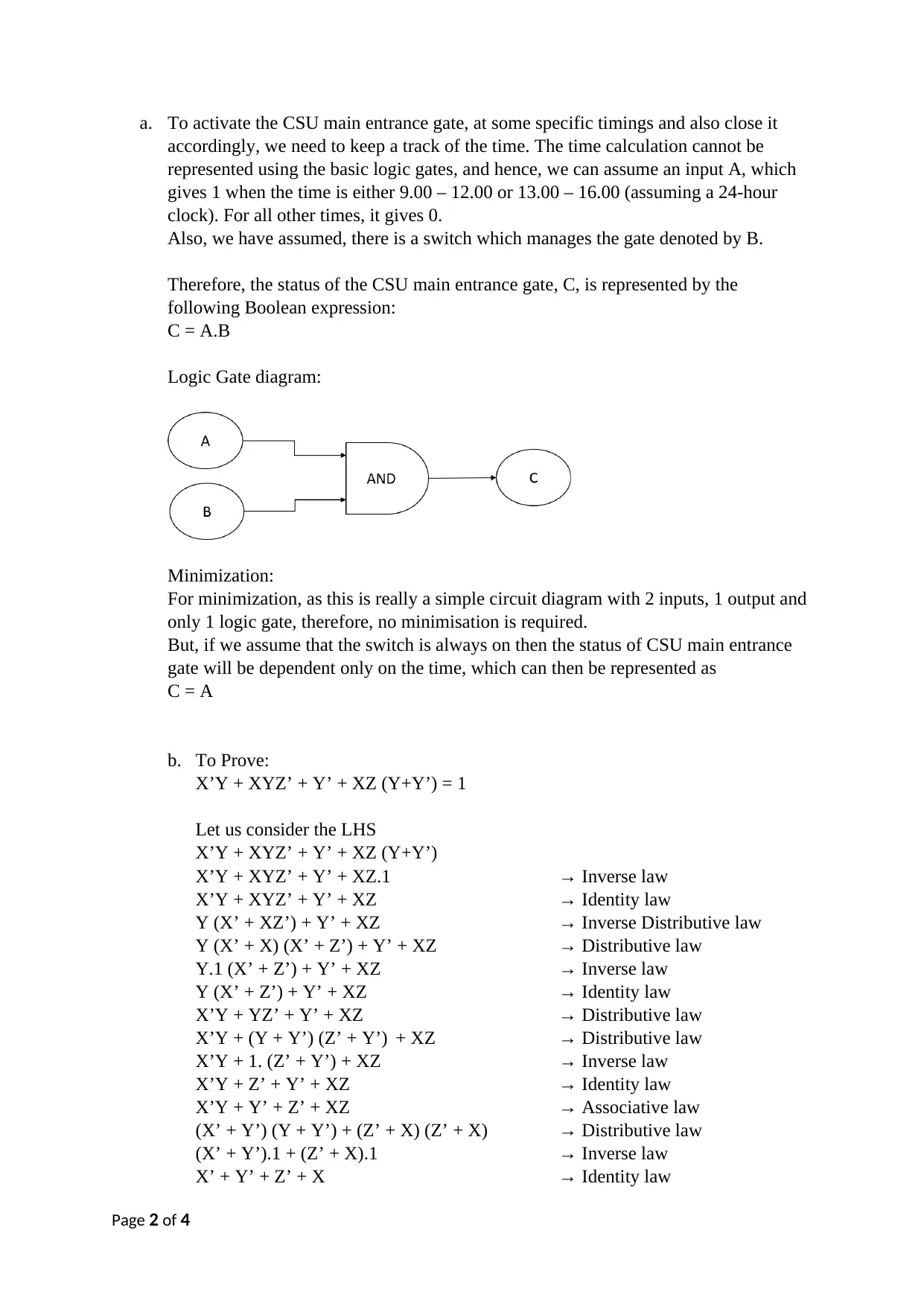

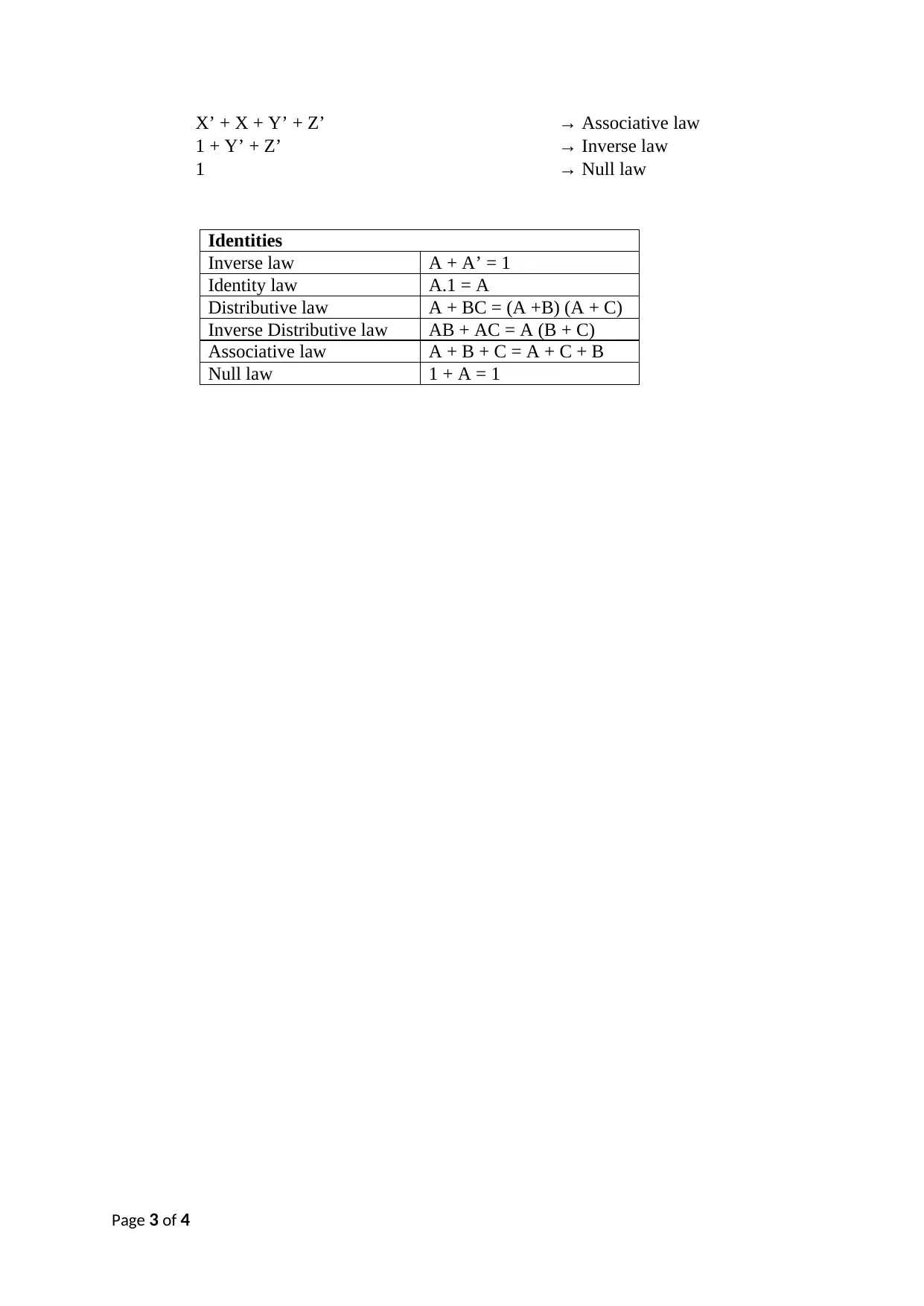

This document provides a detailed solution for Assignment 1 of the ITC544 course, focusing on data representation and digital logic. The assignment covers the IEEE-754 single-precision format, explaining how to interpret and convert binary numbers into decimal values. It also includes an analysis of a 5-bit "word" representation and its corresponding decimal ranges. Furthermore, the document presents a solution to a problem involving logic gates, Boolean expressions, and the activation of a CSU main entrance gate based on time and switch input. The solution includes a Boolean expression, a logic gate diagram, and a simplification analysis. Finally, it includes a proof of a Boolean expression using laws of Boolean algebra.

1 out of 4

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)