ITC544 Assignment Solution: Computer Architecture and Interrupts

VerifiedAdded on 2020/04/01

|3

|325

|54

Homework Assignment

AI Summary

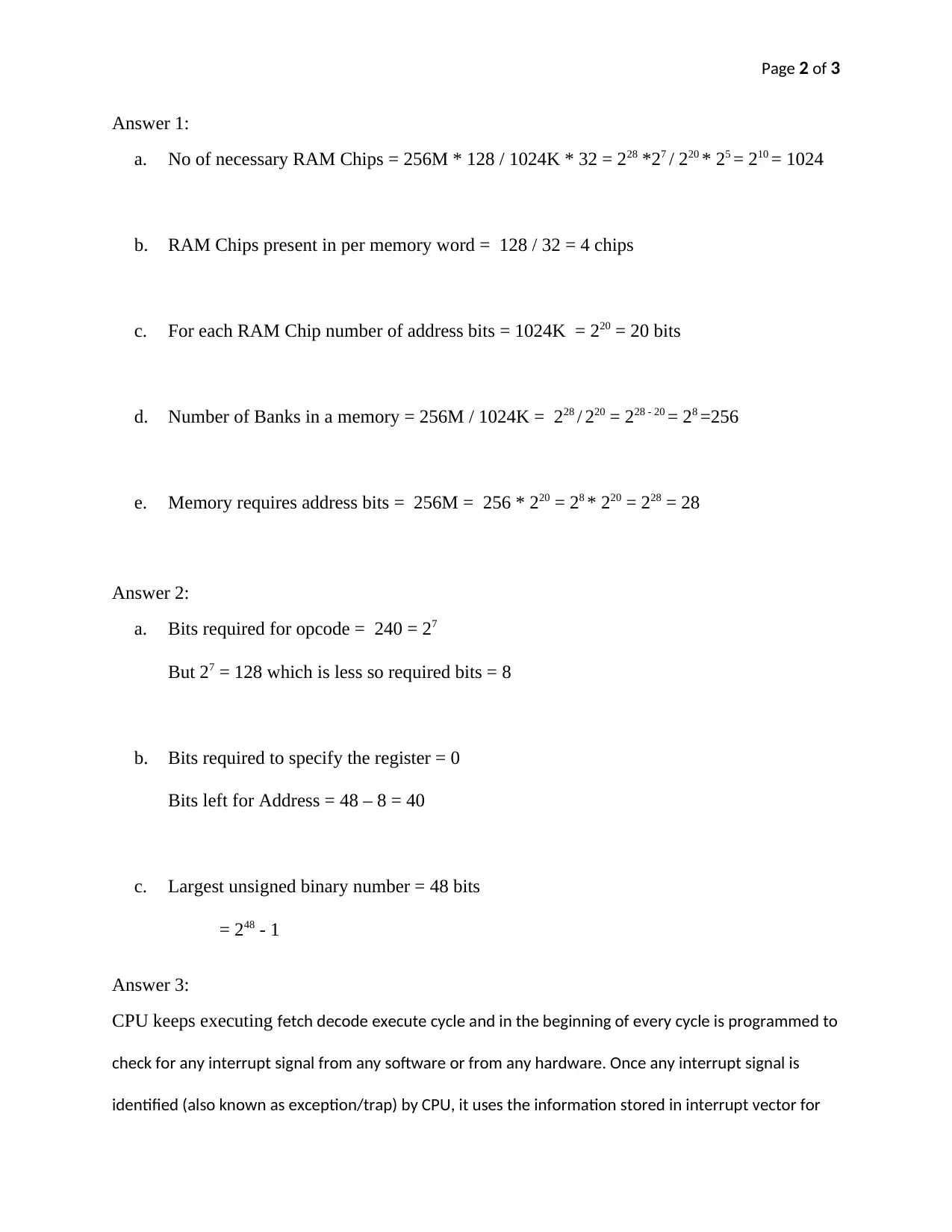

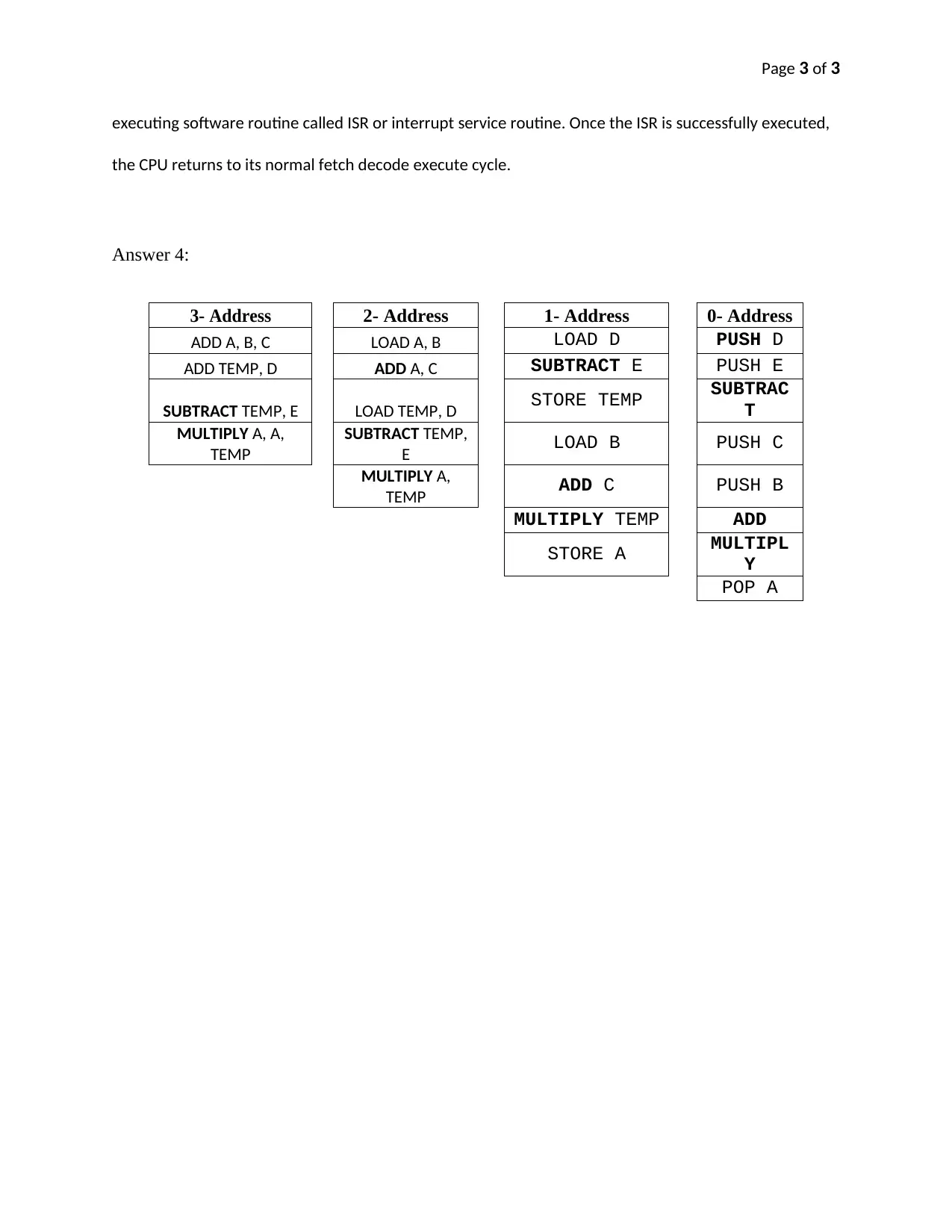

This assignment solution for ITC544 addresses key concepts in computer architecture. The solution calculates the number of RAM chips, address bits, and the number of banks required for a given memory configuration. It also determines the bits required for opcode and registers, and the largest unsigned binary number. The solution further explains the CPU's fetch-decode-execute cycle, including the handling of interrupt signals and the execution of interrupt service routines (ISRs). Finally, the solution provides examples of assembly language code for different addressing modes, including 3-address, 2-address, 1-address, and 0-address formats, illustrating how various operations are performed at the assembly level. This assignment covers crucial aspects of computer organization and assembly language programming.

1 out of 3

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)