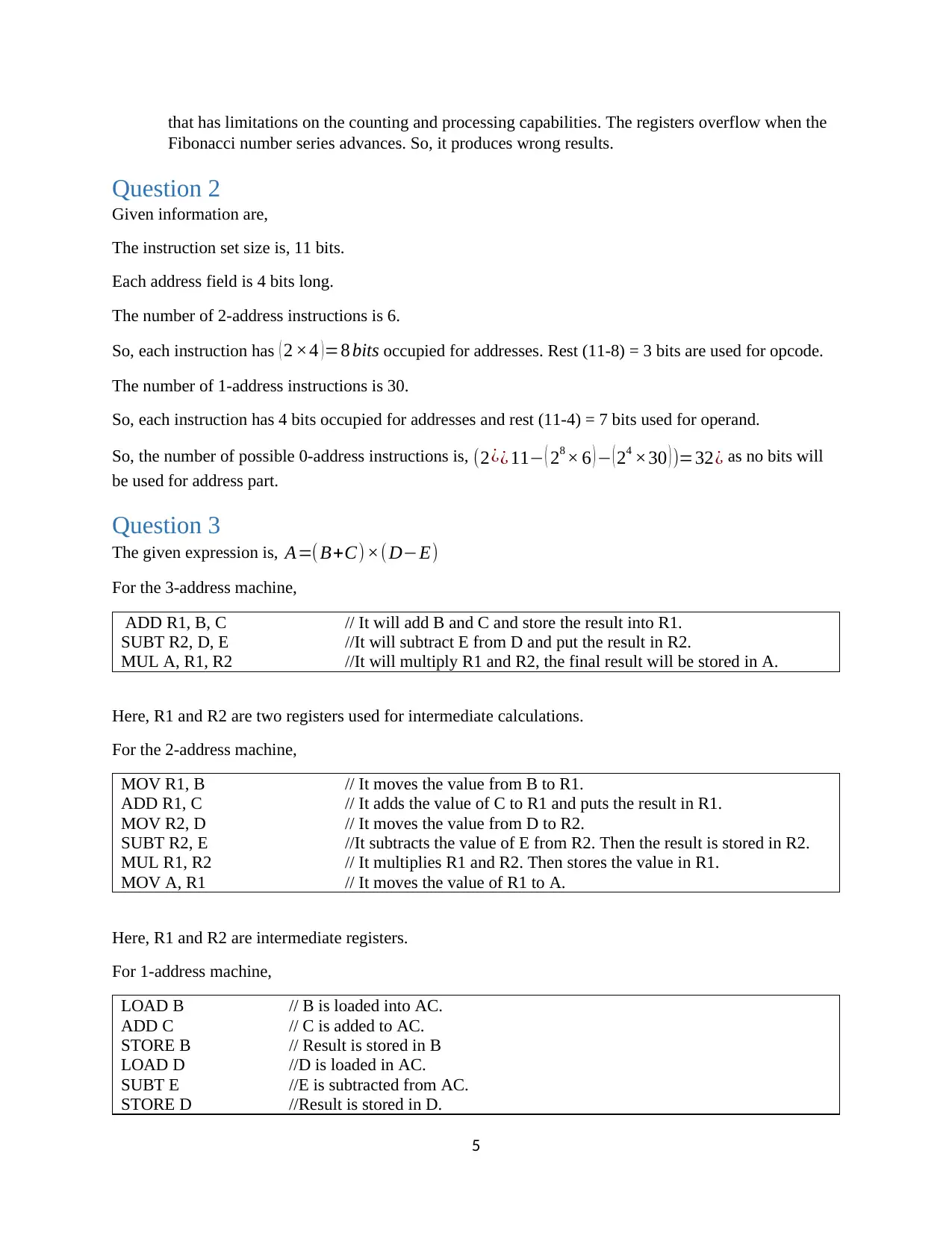

Analyzing MARIE Assembly Code, Instruction Sets, and Addressing

VerifiedAdded on 2021/05/31

|7

|769

|65

Homework Assignment

AI Summary

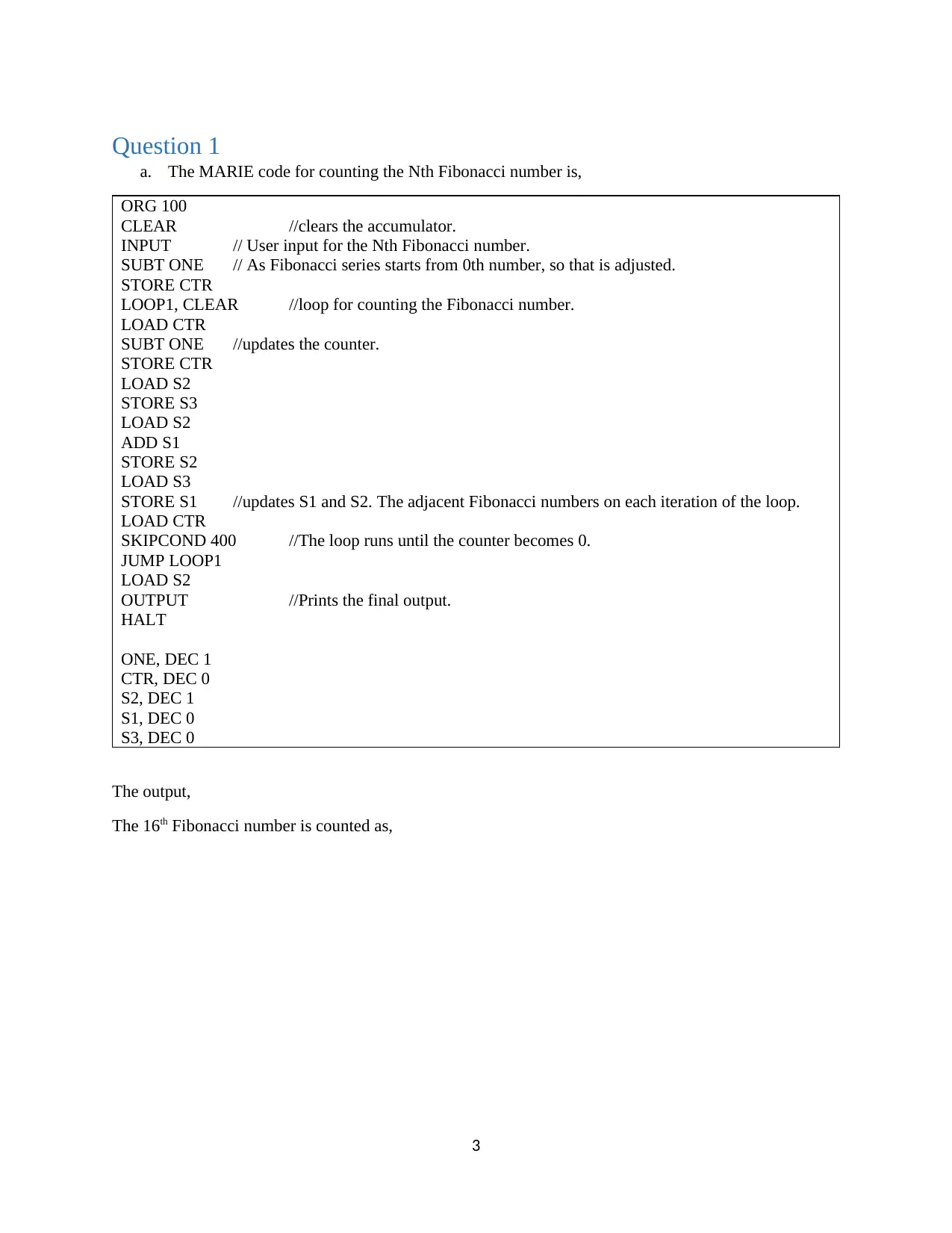

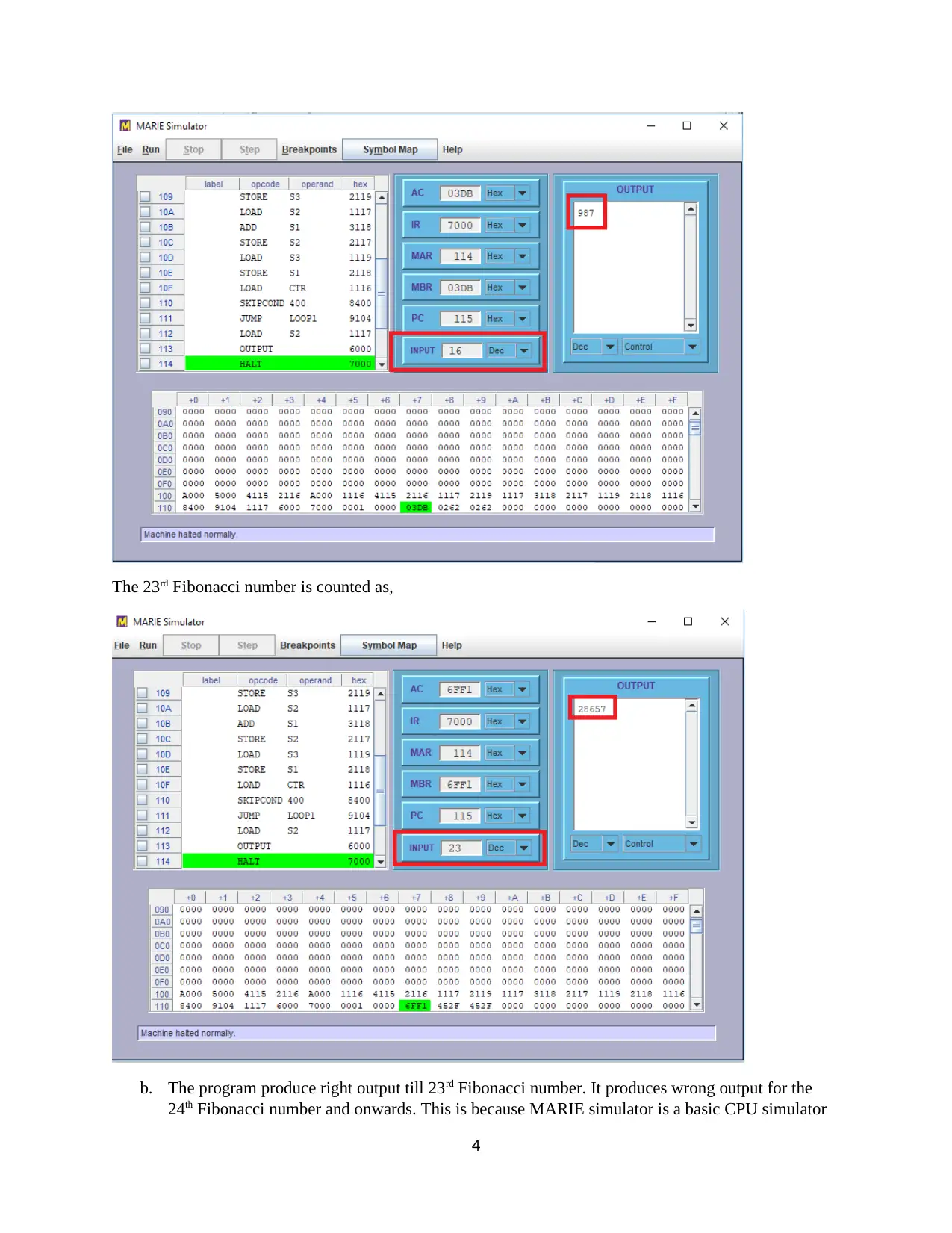

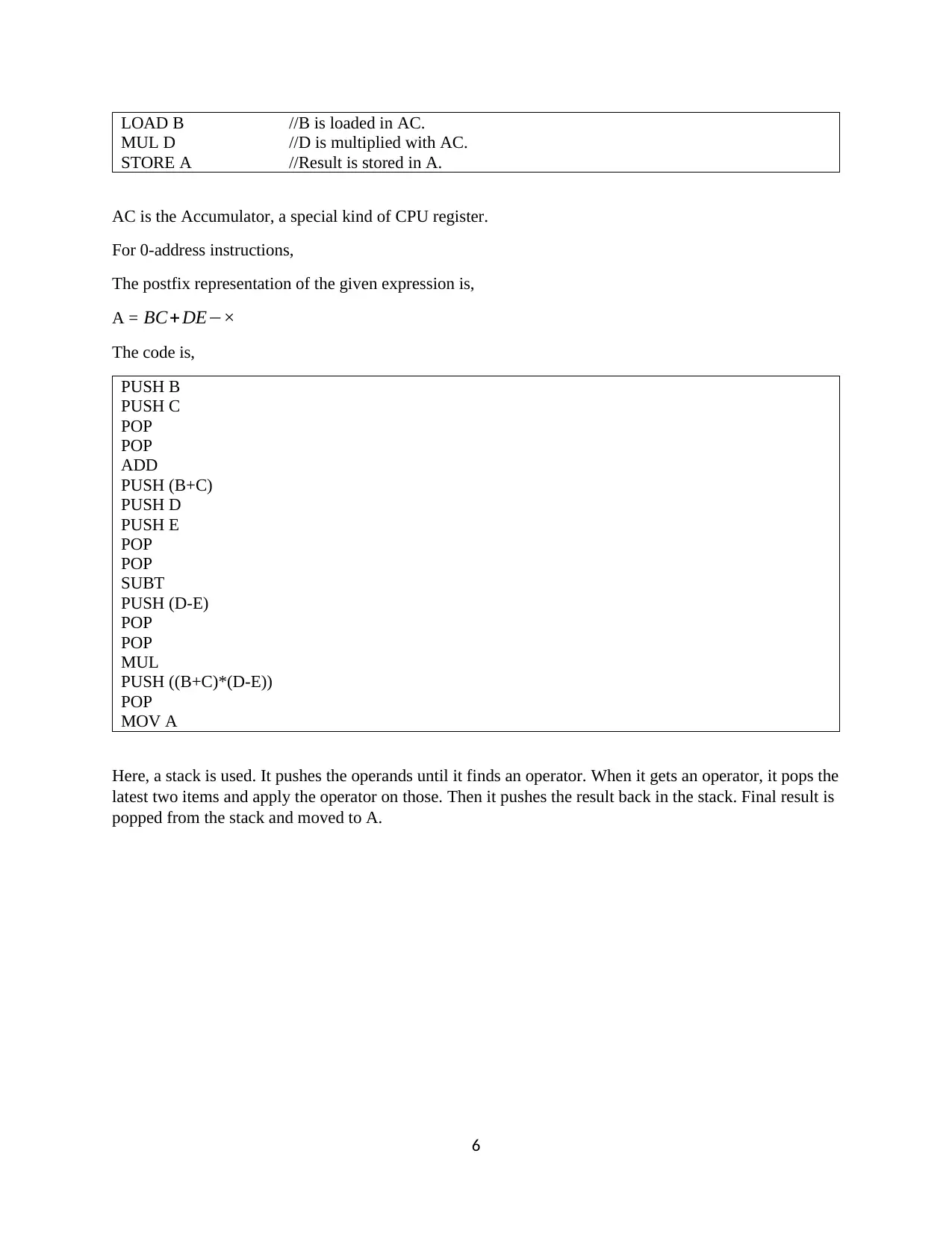

This document presents a comprehensive solution to a computer organization assignment, focusing on MARIE assembly language. The solution begins with the MARIE code for calculating the Nth Fibonacci number, analyzing its functionality and limitations, particularly addressing overflow issues. It then delves into instruction set architectures, detailing the calculation of instruction counts for 2-address, 1-address, and 0-address instructions based on the given bit size and address field lengths. The assignment further explores the conversion of an arithmetic expression into assembly code for 3-address, 2-address, 1-address, and 0-address machines, including the use of registers, accumulators, and stack-based operations with postfix notation. Finally, the solution references the textbook 'The Essentials of Computer Organization and Architecture' by Null and Lobur, providing a solid foundation in computer architecture concepts. This document is available on Desklib, a platform providing students with AI-based study tools, offering valuable insights into computer organization principles and practical assembly language programming.

1 out of 7

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)