Advanced Memory Management and Process Scheduling Analysis: Algorithms

VerifiedAdded on 2020/05/28

|8

|1340

|377

Homework Assignment

AI Summary

This assignment solution comprehensively addresses key concepts in memory management and process scheduling. It begins with an analysis of paging, including calculations for logical and physical addresses, and explains the paging system's functionality. The solution then delves into fragmentation and memory mapping, discussing compaction and relocation. Finally, it explores process management and scheduling algorithms such as First Come First Serve (FCFS), Shortest Job Next (SJF), Shortest Remaining Time (SRT), and Round Robin, calculating waiting time and turnaround time for each. The assignment also provides a list of references for further reading. This solution, available on Desklib, offers valuable insights for students studying operating systems and computer architecture.

Running head: MEMORY MANAGEMENT

Memory Management

Name of Student-

Name of University-

Author’s Note-

Memory Management

Name of Student-

Name of University-

Author’s Note-

Paraphrase This Document

Need a fresh take? Get an instant paraphrase of this document with our AI Paraphraser

1MEMORY MANAGEMENT

BQ1 Memory Management Paging

a. The starting address of frame 1 is 1025 and the end address of frame 1 is 2048.

b.

1. Yes

2. No, because Frame 3 is kept free.

c. Page 3, 6, and 7 are not loaded in memory.

d. The paging system works by bringing the page from the secondary memory to main memory.

CPU generates logical address for the secondary memory. These address are changed to physical

address for finding the data in the main memory [4]. When process A reference an address in

page 3, the page is mapped to a frame which has the data that the CPU wants. Then, the data is

bought to the CPU for its execution. In this example, as page 3 is not mapped with the frame, so

there cannot be any data in page 3. So, the paging will get a miss after searching the address in

page 3.

1. Logical Address- 1023

Memory Size of page and frame table- 1024 bytes

1024 bytes of logical address with 8 pages. Then, each page is of size 1024/8 = 128 bytes

Offset of logical address 1023 % 1024 = 1023

1023/1024 = 0

So, it can be assumed that 1023 is in page 0

Page 0 is mapped to frame number 6

So, the physical address is calculated as

Frame number x Page size + offset

6 * 1024 + 1023 = 7167

So, the physical address in binary is 0001101111111111

2. Logical Address = 3000

Memory Size of page and frame table= 1024 bytes

1024 bytes of logical address with 8 pages. Then, each page is of size 1024/8 = 128 bytes

Offset = 3000 % 1024 = 952

3000/1024 = 2.929

So, it can be assumed that 1023 is in page 2

BQ1 Memory Management Paging

a. The starting address of frame 1 is 1025 and the end address of frame 1 is 2048.

b.

1. Yes

2. No, because Frame 3 is kept free.

c. Page 3, 6, and 7 are not loaded in memory.

d. The paging system works by bringing the page from the secondary memory to main memory.

CPU generates logical address for the secondary memory. These address are changed to physical

address for finding the data in the main memory [4]. When process A reference an address in

page 3, the page is mapped to a frame which has the data that the CPU wants. Then, the data is

bought to the CPU for its execution. In this example, as page 3 is not mapped with the frame, so

there cannot be any data in page 3. So, the paging will get a miss after searching the address in

page 3.

1. Logical Address- 1023

Memory Size of page and frame table- 1024 bytes

1024 bytes of logical address with 8 pages. Then, each page is of size 1024/8 = 128 bytes

Offset of logical address 1023 % 1024 = 1023

1023/1024 = 0

So, it can be assumed that 1023 is in page 0

Page 0 is mapped to frame number 6

So, the physical address is calculated as

Frame number x Page size + offset

6 * 1024 + 1023 = 7167

So, the physical address in binary is 0001101111111111

2. Logical Address = 3000

Memory Size of page and frame table= 1024 bytes

1024 bytes of logical address with 8 pages. Then, each page is of size 1024/8 = 128 bytes

Offset = 3000 % 1024 = 952

3000/1024 = 2.929

So, it can be assumed that 1023 is in page 2

2MEMORY MANAGEMENT

Page 2 is mapped to frame number 2

So, the physical address is calculated as

Frame number x Page size + offset

2 * 1024 + 952 = 3000

So, the physical address in binary is 0000101110111000

3. Logical Address- 4120

Memory Size of page and frame table- 1024 bytes

1024 bytes of logical address with 8 pages. Then, each page is of size 1024/8 = 128 bytes

Offset of logical address 4120 % 1024 = 24

1023/1024 = 4.023

So, it can be assumed that 1023 is in page 4

Page 4 is mapped to frame number 1

So, the physical address is calculated as

Frame number x Page size + offset

1 * 1024 + 24 = 1048

So, the physical address in binary is 0000010000011000

4. Logical Address- 5000

Memory Size of page and frame table- 1024 bytes

1024 bytes of logical address with 8 pages. Then, each page is of size 1024/8 = 128 bytes

Offset of logical address = 5000 % 1024 = 904

5000/1024 = 4.882

So, it can be assumed that 1023 is in page 4

Page 4 is mapped to frame number 1

So, the physical address is calculated as

Frame number x Page size + offset

1 * 1024 + 904 = 1028

So, the physical address in binary is 0000011110001000

BQ2 Fragmentation and Memory Mapping

Compaction or relocation can be performed when there is internal fragmentation in the system

[3]. Compaction is done to rearrange all the data together taking all the empty space together. This

Page 2 is mapped to frame number 2

So, the physical address is calculated as

Frame number x Page size + offset

2 * 1024 + 952 = 3000

So, the physical address in binary is 0000101110111000

3. Logical Address- 4120

Memory Size of page and frame table- 1024 bytes

1024 bytes of logical address with 8 pages. Then, each page is of size 1024/8 = 128 bytes

Offset of logical address 4120 % 1024 = 24

1023/1024 = 4.023

So, it can be assumed that 1023 is in page 4

Page 4 is mapped to frame number 1

So, the physical address is calculated as

Frame number x Page size + offset

1 * 1024 + 24 = 1048

So, the physical address in binary is 0000010000011000

4. Logical Address- 5000

Memory Size of page and frame table- 1024 bytes

1024 bytes of logical address with 8 pages. Then, each page is of size 1024/8 = 128 bytes

Offset of logical address = 5000 % 1024 = 904

5000/1024 = 4.882

So, it can be assumed that 1023 is in page 4

Page 4 is mapped to frame number 1

So, the physical address is calculated as

Frame number x Page size + offset

1 * 1024 + 904 = 1028

So, the physical address in binary is 0000011110001000

BQ2 Fragmentation and Memory Mapping

Compaction or relocation can be performed when there is internal fragmentation in the system

[3]. Compaction is done to rearrange all the data together taking all the empty space together. This

⊘ This is a preview!⊘

Do you want full access?

Subscribe today to unlock all pages.

Trusted by 1+ million students worldwide

3MEMORY MANAGEMENT

compaction or the relocation memory is generally performed before executing some programs in a

system. The compilers and the assemblers which creates the allocation of memory executes zero as its

starting address.

Advantage of compaction or relocation is that allocation that takes place in the memory can be

available in much more amount. This is because the memory blocks are relocated to maximize the space

of the memory. Disadvantage is that this process is considered to be as the overhead process because it

keeps all the processes in the queue.

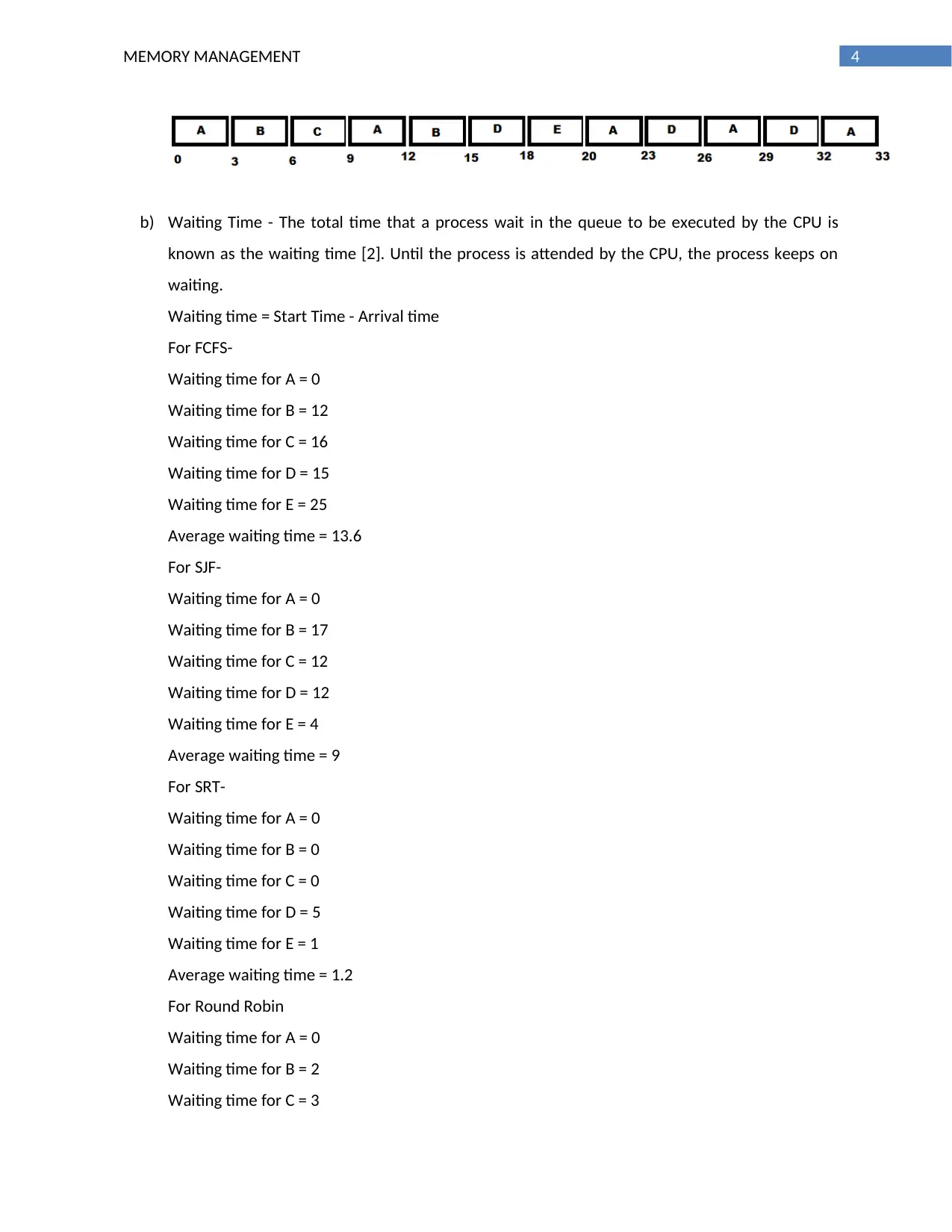

BQ3 Process Management and Scheduling

a)

Job Arrival Time CPU Cycles required

A 0 13

B 1 6

C 3 3

D 7 12

E 9 2

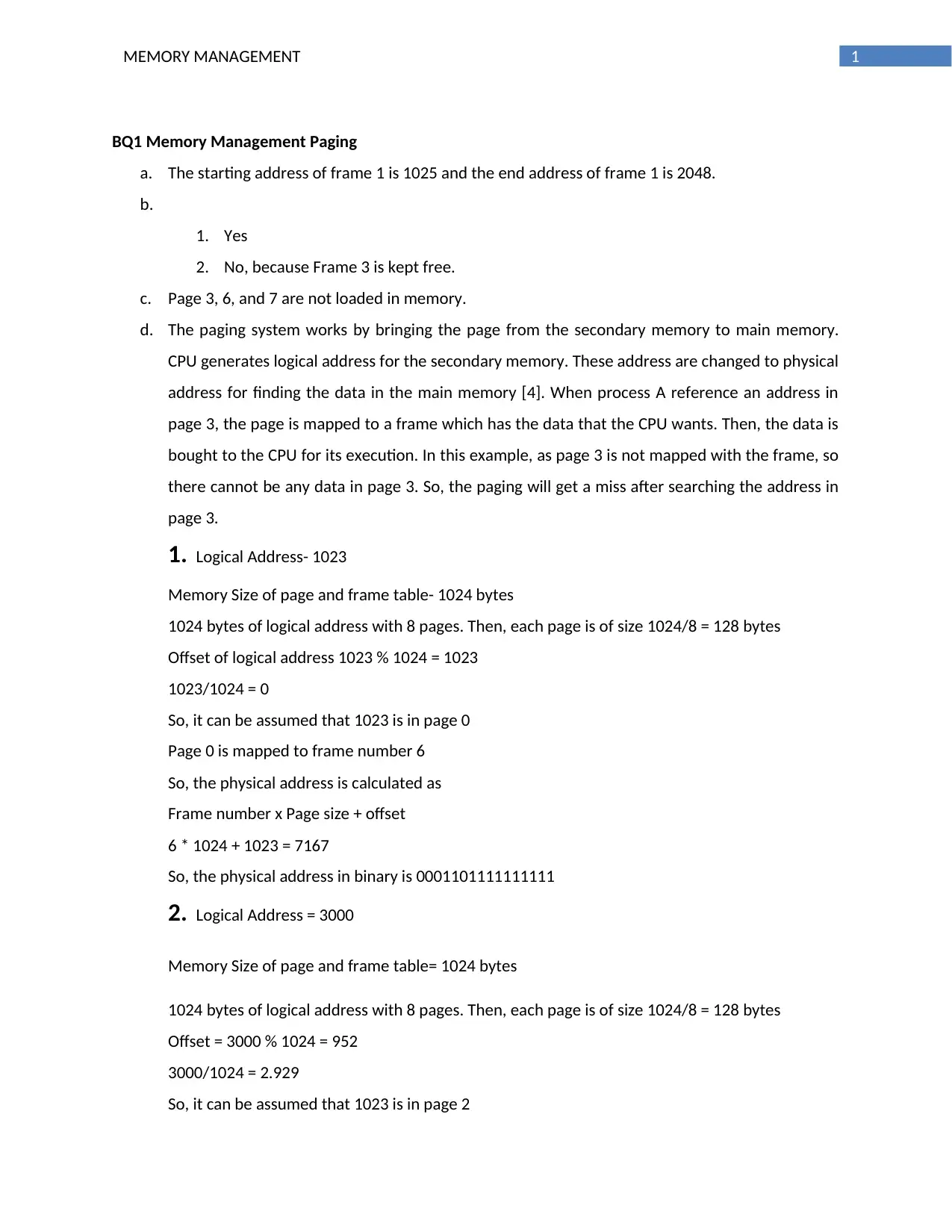

I) First Come First Serve scheduling

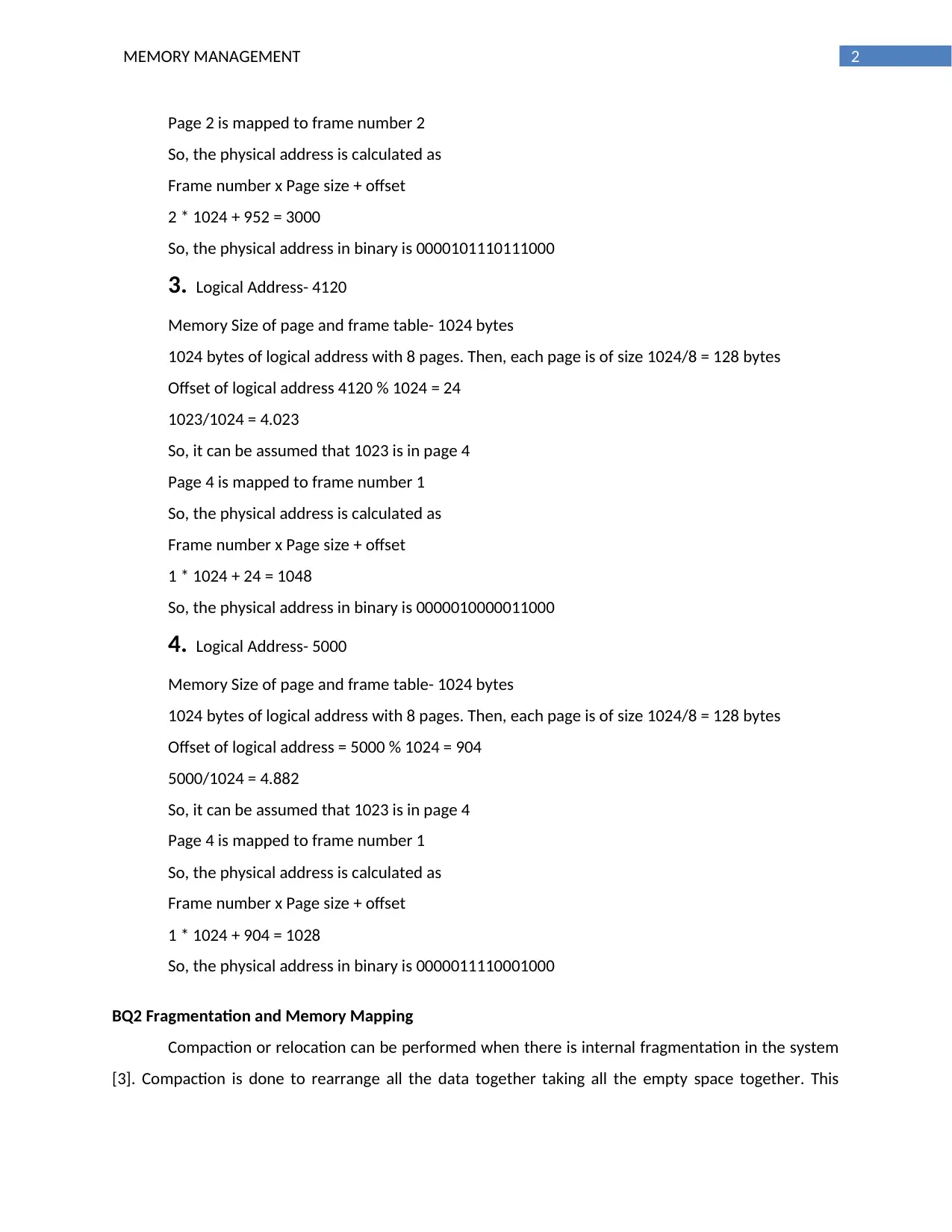

II) Shortest Job Next scheduling

III) Shortest Remaining Time scheduling

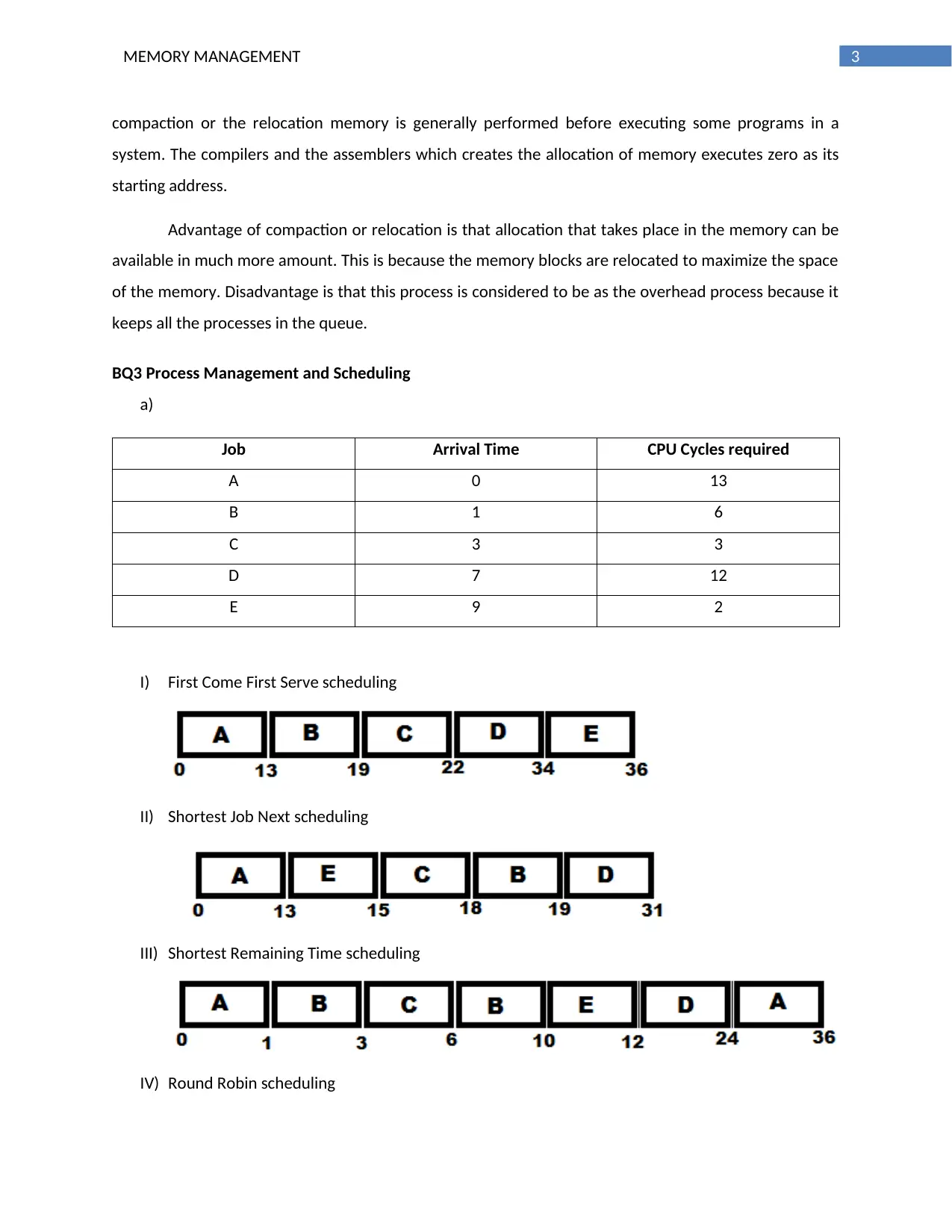

IV) Round Robin scheduling

compaction or the relocation memory is generally performed before executing some programs in a

system. The compilers and the assemblers which creates the allocation of memory executes zero as its

starting address.

Advantage of compaction or relocation is that allocation that takes place in the memory can be

available in much more amount. This is because the memory blocks are relocated to maximize the space

of the memory. Disadvantage is that this process is considered to be as the overhead process because it

keeps all the processes in the queue.

BQ3 Process Management and Scheduling

a)

Job Arrival Time CPU Cycles required

A 0 13

B 1 6

C 3 3

D 7 12

E 9 2

I) First Come First Serve scheduling

II) Shortest Job Next scheduling

III) Shortest Remaining Time scheduling

IV) Round Robin scheduling

Paraphrase This Document

Need a fresh take? Get an instant paraphrase of this document with our AI Paraphraser

4MEMORY MANAGEMENT

b) Waiting Time - The total time that a process wait in the queue to be executed by the CPU is

known as the waiting time [2]. Until the process is attended by the CPU, the process keeps on

waiting.

Waiting time = Start Time - Arrival time

For FCFS-

Waiting time for A = 0

Waiting time for B = 12

Waiting time for C = 16

Waiting time for D = 15

Waiting time for E = 25

Average waiting time = 13.6

For SJF-

Waiting time for A = 0

Waiting time for B = 17

Waiting time for C = 12

Waiting time for D = 12

Waiting time for E = 4

Average waiting time = 9

For SRT-

Waiting time for A = 0

Waiting time for B = 0

Waiting time for C = 0

Waiting time for D = 5

Waiting time for E = 1

Average waiting time = 1.2

For Round Robin

Waiting time for A = 0

Waiting time for B = 2

Waiting time for C = 3

b) Waiting Time - The total time that a process wait in the queue to be executed by the CPU is

known as the waiting time [2]. Until the process is attended by the CPU, the process keeps on

waiting.

Waiting time = Start Time - Arrival time

For FCFS-

Waiting time for A = 0

Waiting time for B = 12

Waiting time for C = 16

Waiting time for D = 15

Waiting time for E = 25

Average waiting time = 13.6

For SJF-

Waiting time for A = 0

Waiting time for B = 17

Waiting time for C = 12

Waiting time for D = 12

Waiting time for E = 4

Average waiting time = 9

For SRT-

Waiting time for A = 0

Waiting time for B = 0

Waiting time for C = 0

Waiting time for D = 5

Waiting time for E = 1

Average waiting time = 1.2

For Round Robin

Waiting time for A = 0

Waiting time for B = 2

Waiting time for C = 3

5MEMORY MANAGEMENT

Waiting time for D = 8

Waiting time for E = 9

Average waiting time = 4.4

Turn Around Time- When the CPU completes executing the process, the time at which the

process is being executed is known as the turn around time [1]. The turn around time is the total

time taken for the CPU to complete the process.

Turn Around Time = Burst Time + Waiting Time

For FCFS-

Turn Around Time for A = 13

Turn Around Time for B = 18

Turn Around Time for C = 19

Turn Around Time for D = 27

Turn Around Time for E = 27

Average Turn Around Time = 20.8

For SJF-

Turn Around Time for A = 13

Turn Around Time for B = 23

Turn Around Time for C = 15

Turn Around Time for D = 24

Turn Around Time for E = 6

Average Turn Around Time = 16.2

For SRT-

Turn Around Time for A = 13

Turn Around Time for B = 6

Turn Around Time for C = 3

Turn Around Time for D = 17

Turn Around Time for E = 3

Average Turn Around Time = 7.8

For Round Robin

Turn Around Time for A = 13

Turn Around Time for B = 8

Turn Around Time for C = 6

Waiting time for D = 8

Waiting time for E = 9

Average waiting time = 4.4

Turn Around Time- When the CPU completes executing the process, the time at which the

process is being executed is known as the turn around time [1]. The turn around time is the total

time taken for the CPU to complete the process.

Turn Around Time = Burst Time + Waiting Time

For FCFS-

Turn Around Time for A = 13

Turn Around Time for B = 18

Turn Around Time for C = 19

Turn Around Time for D = 27

Turn Around Time for E = 27

Average Turn Around Time = 20.8

For SJF-

Turn Around Time for A = 13

Turn Around Time for B = 23

Turn Around Time for C = 15

Turn Around Time for D = 24

Turn Around Time for E = 6

Average Turn Around Time = 16.2

For SRT-

Turn Around Time for A = 13

Turn Around Time for B = 6

Turn Around Time for C = 3

Turn Around Time for D = 17

Turn Around Time for E = 3

Average Turn Around Time = 7.8

For Round Robin

Turn Around Time for A = 13

Turn Around Time for B = 8

Turn Around Time for C = 6

⊘ This is a preview!⊘

Do you want full access?

Subscribe today to unlock all pages.

Trusted by 1+ million students worldwide

6MEMORY MANAGEMENT

Turn Around Time for D = 20

Turn Around Time for E = 11

Average Turn Around Time = 11.6

Turn Around Time for D = 20

Turn Around Time for E = 11

Average Turn Around Time = 11.6

Paraphrase This Document

Need a fresh take? Get an instant paraphrase of this document with our AI Paraphraser

7MEMORY MANAGEMENT

References

[1] Parashar, Mayank, and Amit Chugh. "Time Quantum based CPU Scheduling

Algorithm." International Journal of Computer Applications 98, no. 3 (2014).

[2] Stanford, David A., Peter Taylor, and Ilze Ziedins. "Waiting time distributions in the accumulating

priority queue." Queueing Systems 77, no. 3 (2014): 297-330.

[3] Rafter, M. F. M., Sufizar Ahmad, R. Ibrahim, and R. Hussin. "Development of stainless steel

(SS316L) foam with different composition using compaction method." (2014).

[4] Li, Chu, Dan Feng, Yu Hua, Wen Xia, and Fang Wang. "GASA: A New Page Replacement Algorithm

for NAND Flash Memory." In Networking, Architecture and Storage (NAS), 2016 IEEE

International Conference on, pp. 1-9. IEEE, 2016.

References

[1] Parashar, Mayank, and Amit Chugh. "Time Quantum based CPU Scheduling

Algorithm." International Journal of Computer Applications 98, no. 3 (2014).

[2] Stanford, David A., Peter Taylor, and Ilze Ziedins. "Waiting time distributions in the accumulating

priority queue." Queueing Systems 77, no. 3 (2014): 297-330.

[3] Rafter, M. F. M., Sufizar Ahmad, R. Ibrahim, and R. Hussin. "Development of stainless steel

(SS316L) foam with different composition using compaction method." (2014).

[4] Li, Chu, Dan Feng, Yu Hua, Wen Xia, and Fang Wang. "GASA: A New Page Replacement Algorithm

for NAND Flash Memory." In Networking, Architecture and Storage (NAS), 2016 IEEE

International Conference on, pp. 1-9. IEEE, 2016.

1 out of 8

Related Documents

Your All-in-One AI-Powered Toolkit for Academic Success.

+13062052269

info@desklib.com

Available 24*7 on WhatsApp / Email

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)

Unlock your academic potential

Copyright © 2020–2026 A2Z Services. All Rights Reserved. Developed and managed by ZUCOL.