Analogue and Digital Electronics 2: Sequential Logic Design Project

VerifiedAdded on 2019/09/30

|5

|1281

|238

Practical Assignment

AI Summary

This document presents a solution for a practical assignment in the Analogue and Digital Electronics 2 module (NG2S902) at the University of South Wales. The assignment focuses on sequential logic design, requiring the design of both synchronous and asynchronous circuits. The first task involves designing a synchronous sequential machine to detect prime numbers within 4-bit binary words, including drawing a state diagram (Mealy), assigning binary state identifiers, creating a next-state truth table, selecting a bistable type, and determining expressions for bistable inputs and outputs. The second task involves designing an asynchronous system for a monitoring system that checks the response of a device to pulses, including the design up to the point where internal conditions are designated to the lines in the merged table. The assignment also includes a detailed marking scheme and feedback form.

FACULTY OF COMPUTING,

ENGINEERING and SCIENCE

Final mark awarded:_____

Assessment Cover Sheet and Feedback Form 2015/16

Module Code:

NG2S902

Module Title:

Analogue and Digital Electronics

2

Module Lecturer:

Glyn Robins

Assessment Title and Tasks:

Sequential Logic Design. (Referral

Assessment No.

e.g. 2

No. of pages submitted in total including this page:

Completed by student

Word Count of submission

(if applicable): Completed by student

Date Set:

2nd June 2016

Submission Date:

3rd August 2016

Return Date:

Part A: Record of Submission (to be completed by Student)

Extenuating Circumstances

If there are any exceptional circumstances that may have affected your ability to

undertake or submit this assignment, make sure you contact the Advice Centre on your

campus prior to your submission deadline.

Fit to sit policy:

The University operates a fit to sit policy whereby you, in submitting or presenting

yourself for an assessment, are declaring that you are fit to sit the assessment. You

cannot subsequently claim that your performance in this assessment was affected by

extenuating factors.

Plagiarism and Unfair Practice Declaration:

By submitting this assessment, you declare that it is your own work and that the sources

of information and material you have used (including the internet) have been fully

identified and properly acknowledged as required1. Additionally, the work presented has

not been submitted for any other assessment. You also understand that the Faculty

reserves the right to investigate allegations of plagiarism or unfair practice which, if

proven, could result in a fail in this assessment and may affect your progress.

Details of Submission:

Note that all work handed in after the submission date and within 5 working days will be

capped at 40%2. No marks will be awarded if the assessment is submitted after the late

submission date unless extenuating circumstances are applied for and accepted (Advice

Centre to be consulted).

Work should be submitted as detailed in your student handbook. You are responsible for

checking the method of submission.

You are required to acknowledge that

you have read the above statements

by writing your student number (s) in

the box:

Student Number(s):

1 University Academic Integrity Regulations

2 Information on exclusions to this rule is available from Campus Advice Shops

ENGINEERING and SCIENCE

Final mark awarded:_____

Assessment Cover Sheet and Feedback Form 2015/16

Module Code:

NG2S902

Module Title:

Analogue and Digital Electronics

2

Module Lecturer:

Glyn Robins

Assessment Title and Tasks:

Sequential Logic Design. (Referral

Assessment No.

e.g. 2

No. of pages submitted in total including this page:

Completed by student

Word Count of submission

(if applicable): Completed by student

Date Set:

2nd June 2016

Submission Date:

3rd August 2016

Return Date:

Part A: Record of Submission (to be completed by Student)

Extenuating Circumstances

If there are any exceptional circumstances that may have affected your ability to

undertake or submit this assignment, make sure you contact the Advice Centre on your

campus prior to your submission deadline.

Fit to sit policy:

The University operates a fit to sit policy whereby you, in submitting or presenting

yourself for an assessment, are declaring that you are fit to sit the assessment. You

cannot subsequently claim that your performance in this assessment was affected by

extenuating factors.

Plagiarism and Unfair Practice Declaration:

By submitting this assessment, you declare that it is your own work and that the sources

of information and material you have used (including the internet) have been fully

identified and properly acknowledged as required1. Additionally, the work presented has

not been submitted for any other assessment. You also understand that the Faculty

reserves the right to investigate allegations of plagiarism or unfair practice which, if

proven, could result in a fail in this assessment and may affect your progress.

Details of Submission:

Note that all work handed in after the submission date and within 5 working days will be

capped at 40%2. No marks will be awarded if the assessment is submitted after the late

submission date unless extenuating circumstances are applied for and accepted (Advice

Centre to be consulted).

Work should be submitted as detailed in your student handbook. You are responsible for

checking the method of submission.

You are required to acknowledge that

you have read the above statements

by writing your student number (s) in

the box:

Student Number(s):

1 University Academic Integrity Regulations

2 Information on exclusions to this rule is available from Campus Advice Shops

Paraphrase This Document

Need a fresh take? Get an instant paraphrase of this document with our AI Paraphraser

IT IS YOUR RESPONSIBILITY TO KEEP A RECORD OF ALL WORK

SUBMITTED

Part B: Marking and Assessment

(to be completed by Module Lecturer)

This assignment will be marked out of 100%

This assignment contributes to 15% of the total module marks.

This assignment is bonded.

Assessment Task:

Scenario: You are to design synchronous and asynchronous circuits

that will allow the following requirements to be met.

Tasks:

1. Packet number checking

A synchronous sequential machine is to have a single input line and a single

output line. The circuit is to receive messages of 4-bit words coded in binary

(least significant bit first). The purpose of the circuit is to detect whether the

number coming in is a prime number (divisible by only itself and 1). Thus, the

output is to become 1 whenever a 4-bit word does represent a valid prime

number. At the end of each word the machine is to return to the reset starting

state.

Steps:

1) Draw a State Diagram (Mealy) and check for redundancies

2) Then assign binary State Identifiers.

3) Make a Next State Truth Table (NSTT)

4) Select a bistable type

5) Determine expressions for the bistable inputs

6) Determine expressions for the outputs

2. Monitoring System

A monitoring system sends a fixed duration positive going pulses to a

device to ensure that it is operating correctly. The device will respond

by lowering its normally high line as soon as it receives the pulse then

raising the line again within the 1s if working correctly. If the device

line doesn’t respond correctly by not raising the line or raising it then

lowering it within the pulse period an alarm must occur. No response is

not an alarm condition.

1) Carry out a design for the asynchronous system that will realise the

requirements up to the point where internal conditions are designated

to the lines in the merged table.

2) Explain what the designer would have to do to ensure the system was

hazard free and the output was as short as possible.

Learning Outcomes to be assessed (as specified in the validated module

descriptor http://icis.glam.ac.uk):

1. Critically evaluate the technologies and design techniques used in

electronic circuit and system design.

2. Design electronic circuits and systems using appropriate modern

technologies and techniques to meet technical and commercial specifications

Grading Criteria

49% - 40% A Pass grade is recommended for the achievement of the

learning outcomes

SUBMITTED

Part B: Marking and Assessment

(to be completed by Module Lecturer)

This assignment will be marked out of 100%

This assignment contributes to 15% of the total module marks.

This assignment is bonded.

Assessment Task:

Scenario: You are to design synchronous and asynchronous circuits

that will allow the following requirements to be met.

Tasks:

1. Packet number checking

A synchronous sequential machine is to have a single input line and a single

output line. The circuit is to receive messages of 4-bit words coded in binary

(least significant bit first). The purpose of the circuit is to detect whether the

number coming in is a prime number (divisible by only itself and 1). Thus, the

output is to become 1 whenever a 4-bit word does represent a valid prime

number. At the end of each word the machine is to return to the reset starting

state.

Steps:

1) Draw a State Diagram (Mealy) and check for redundancies

2) Then assign binary State Identifiers.

3) Make a Next State Truth Table (NSTT)

4) Select a bistable type

5) Determine expressions for the bistable inputs

6) Determine expressions for the outputs

2. Monitoring System

A monitoring system sends a fixed duration positive going pulses to a

device to ensure that it is operating correctly. The device will respond

by lowering its normally high line as soon as it receives the pulse then

raising the line again within the 1s if working correctly. If the device

line doesn’t respond correctly by not raising the line or raising it then

lowering it within the pulse period an alarm must occur. No response is

not an alarm condition.

1) Carry out a design for the asynchronous system that will realise the

requirements up to the point where internal conditions are designated

to the lines in the merged table.

2) Explain what the designer would have to do to ensure the system was

hazard free and the output was as short as possible.

Learning Outcomes to be assessed (as specified in the validated module

descriptor http://icis.glam.ac.uk):

1. Critically evaluate the technologies and design techniques used in

electronic circuit and system design.

2. Design electronic circuits and systems using appropriate modern

technologies and techniques to meet technical and commercial specifications

Grading Criteria

49% - 40% A Pass grade is recommended for the achievement of the

learning outcomes

59% - 50% In order to achieve a percentage in this range the student

must:

use correct methods and techniques to analyse and

process information/data;

generate solutions which are fundamentally correct but

contain numerous errors and/or failures to produce the

simplest solutions to problems;

present and communicate work coherently.

69% - 60% In order to achieve a percentage in this range the student

must:

use a range of methods and techniques to analyse and

process information/data;

generate solutions which are fundamentally correct but

contain minor errors and/or failures to produce the

simplest solutions to problems;

present and communicate work coherently using

technical language correctly.

70% + In order to achieve a percentage in this range the student

must:

check validity when analysing and processing complex

information/data;

generate solutions which are correct and contain very

minor or no errors or failures to produce the simplest

solutions to problems;

show an individual approach in presenting and

communicating work coherently, using technical

language fluently.

Fail

less than 40%

This will be given if there is a failure to achieve all outcomes

defined in the assessment criteria for the module. The

examination board may refer students who are likely to

succeed after further assessment.

Feedback/feed-forward (linked to assessment criteria):

Areas where you have done well:

Feedback from this assessment to help you to improve future assessments:

Other comments

must:

use correct methods and techniques to analyse and

process information/data;

generate solutions which are fundamentally correct but

contain numerous errors and/or failures to produce the

simplest solutions to problems;

present and communicate work coherently.

69% - 60% In order to achieve a percentage in this range the student

must:

use a range of methods and techniques to analyse and

process information/data;

generate solutions which are fundamentally correct but

contain minor errors and/or failures to produce the

simplest solutions to problems;

present and communicate work coherently using

technical language correctly.

70% + In order to achieve a percentage in this range the student

must:

check validity when analysing and processing complex

information/data;

generate solutions which are correct and contain very

minor or no errors or failures to produce the simplest

solutions to problems;

show an individual approach in presenting and

communicating work coherently, using technical

language fluently.

Fail

less than 40%

This will be given if there is a failure to achieve all outcomes

defined in the assessment criteria for the module. The

examination board may refer students who are likely to

succeed after further assessment.

Feedback/feed-forward (linked to assessment criteria):

Areas where you have done well:

Feedback from this assessment to help you to improve future assessments:

Other comments

⊘ This is a preview!⊘

Do you want full access?

Subscribe today to unlock all pages.

Trusted by 1+ million students worldwide

Mark: Marker’s Signature: Date:

Work on this module has been marked, double marked/moderated in

line with USW procedures.

Provisional mark only: subject to change and/or confirmation by the Assessment

Board

Work on this module has been marked, double marked/moderated in

line with USW procedures.

Provisional mark only: subject to change and/or confirmation by the Assessment

Board

Paraphrase This Document

Need a fresh take? Get an instant paraphrase of this document with our AI Paraphraser

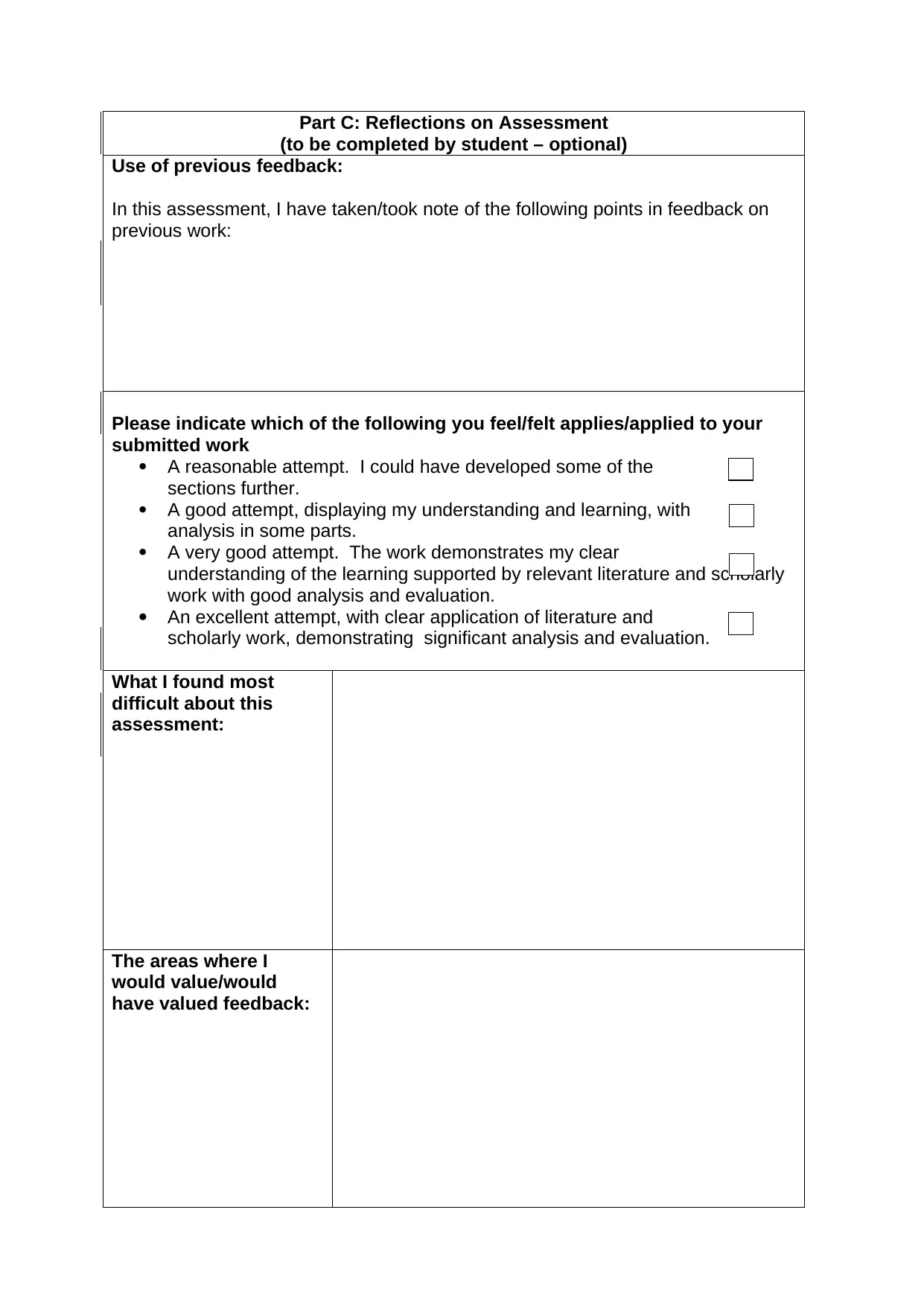

Part C: Reflections on Assessment

(to be completed by student – optional)

Use of previous feedback:

In this assessment, I have taken/took note of the following points in feedback on

previous work:

Please indicate which of the following you feel/felt applies/applied to your

submitted work

A reasonable attempt. I could have developed some of the

sections further.

A good attempt, displaying my understanding and learning, with

analysis in some parts.

A very good attempt. The work demonstrates my clear

understanding of the learning supported by relevant literature and scholarly

work with good analysis and evaluation.

An excellent attempt, with clear application of literature and

scholarly work, demonstrating significant analysis and evaluation.

What I found most

difficult about this

assessment:

The areas where I

would value/would

have valued feedback:

(to be completed by student – optional)

Use of previous feedback:

In this assessment, I have taken/took note of the following points in feedback on

previous work:

Please indicate which of the following you feel/felt applies/applied to your

submitted work

A reasonable attempt. I could have developed some of the

sections further.

A good attempt, displaying my understanding and learning, with

analysis in some parts.

A very good attempt. The work demonstrates my clear

understanding of the learning supported by relevant literature and scholarly

work with good analysis and evaluation.

An excellent attempt, with clear application of literature and

scholarly work, demonstrating significant analysis and evaluation.

What I found most

difficult about this

assessment:

The areas where I

would value/would

have valued feedback:

1 out of 5

Related Documents

Your All-in-One AI-Powered Toolkit for Academic Success.

+13062052269

info@desklib.com

Available 24*7 on WhatsApp / Email

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)

Unlock your academic potential

Copyright © 2020–2026 A2Z Services. All Rights Reserved. Developed and managed by ZUCOL.