VHDL Register File: Structural Design, Implementation & Testing

VerifiedAdded on 2023/04/20

|4

|928

|211

Practical Assignment

AI Summary

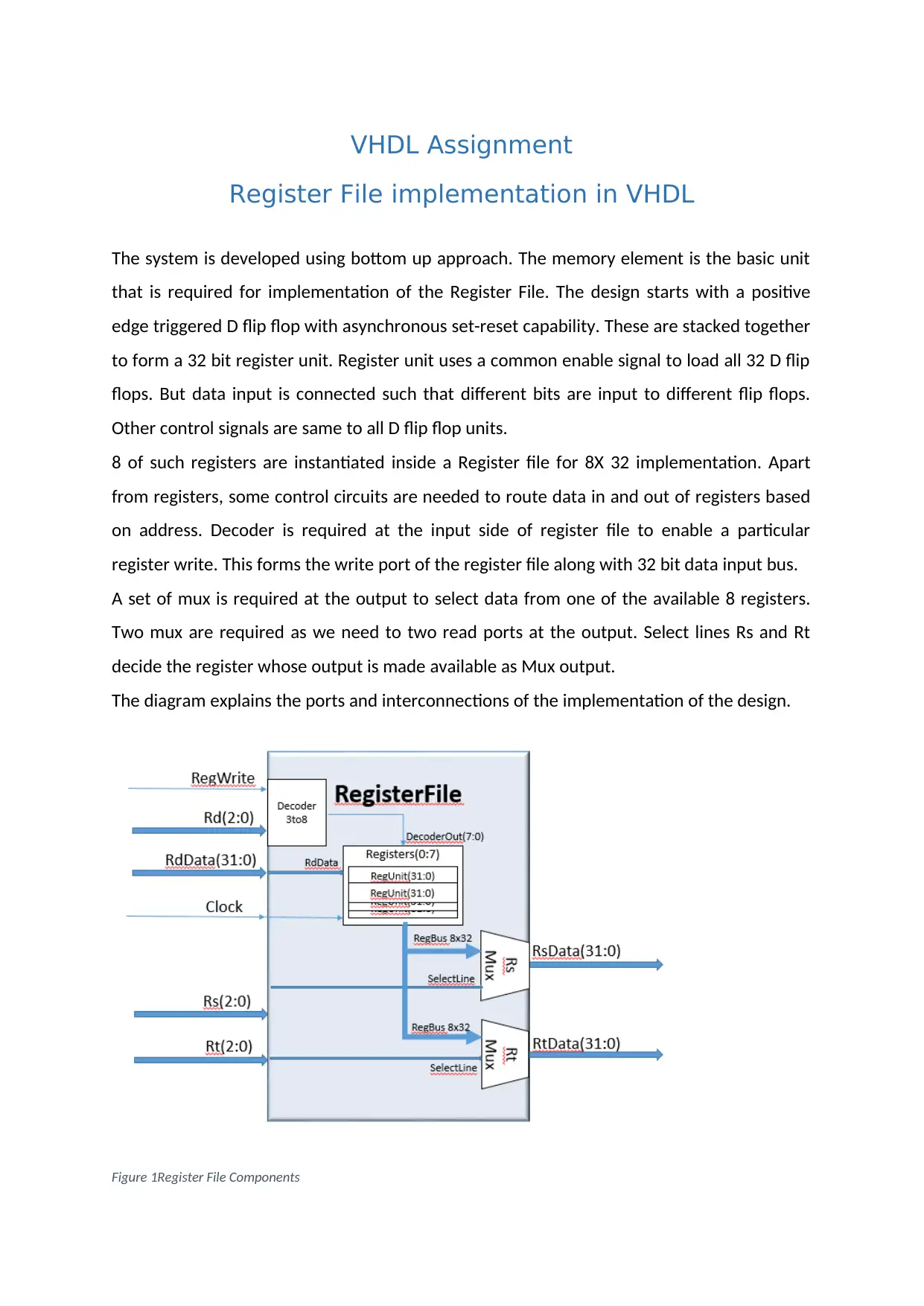

This assignment solution provides a detailed implementation of an 8x32 register file in VHDL using structural modeling. The design utilizes a bottom-up approach, starting with a positive edge-triggered D flip-flop as the basic memory element. These flip-flops are combined to form a 32-bit register unit, which are then instantiated eight times within the register file. The design incorporates a decoder for register write selection and multiplexers for implementing two read ports. The solution includes VHDL code for the D flip-flop, register unit, decoder, multiplexer, and the top-level register file entity. A testbench is also provided to verify the functionality of the register file, ensuring data integrity during simultaneous read and write operations. The testbench performs back-to-back write operations and verifies data retention through simultaneous reads, demonstrating the correct operation of the register file.

1 out of 4

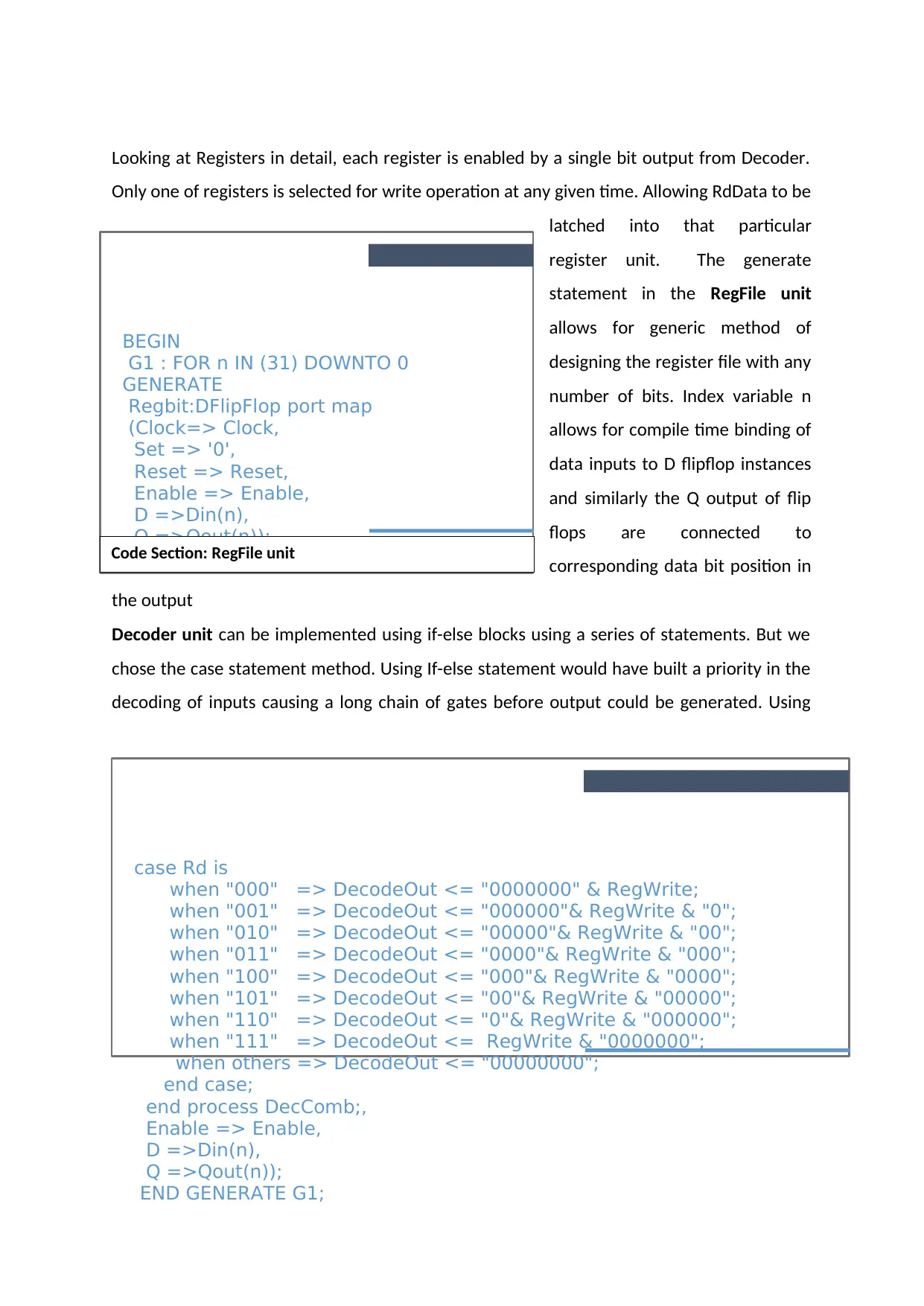

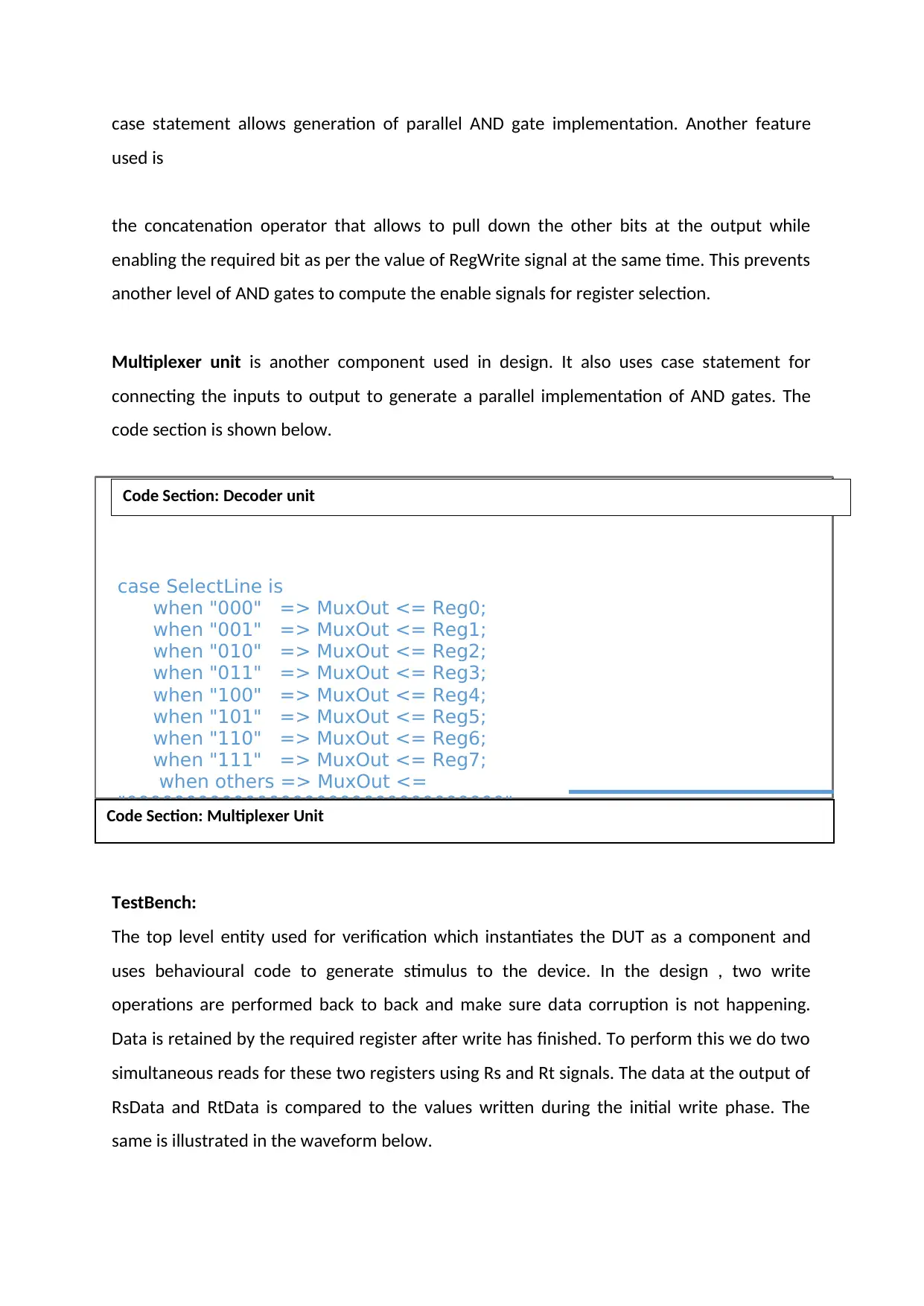

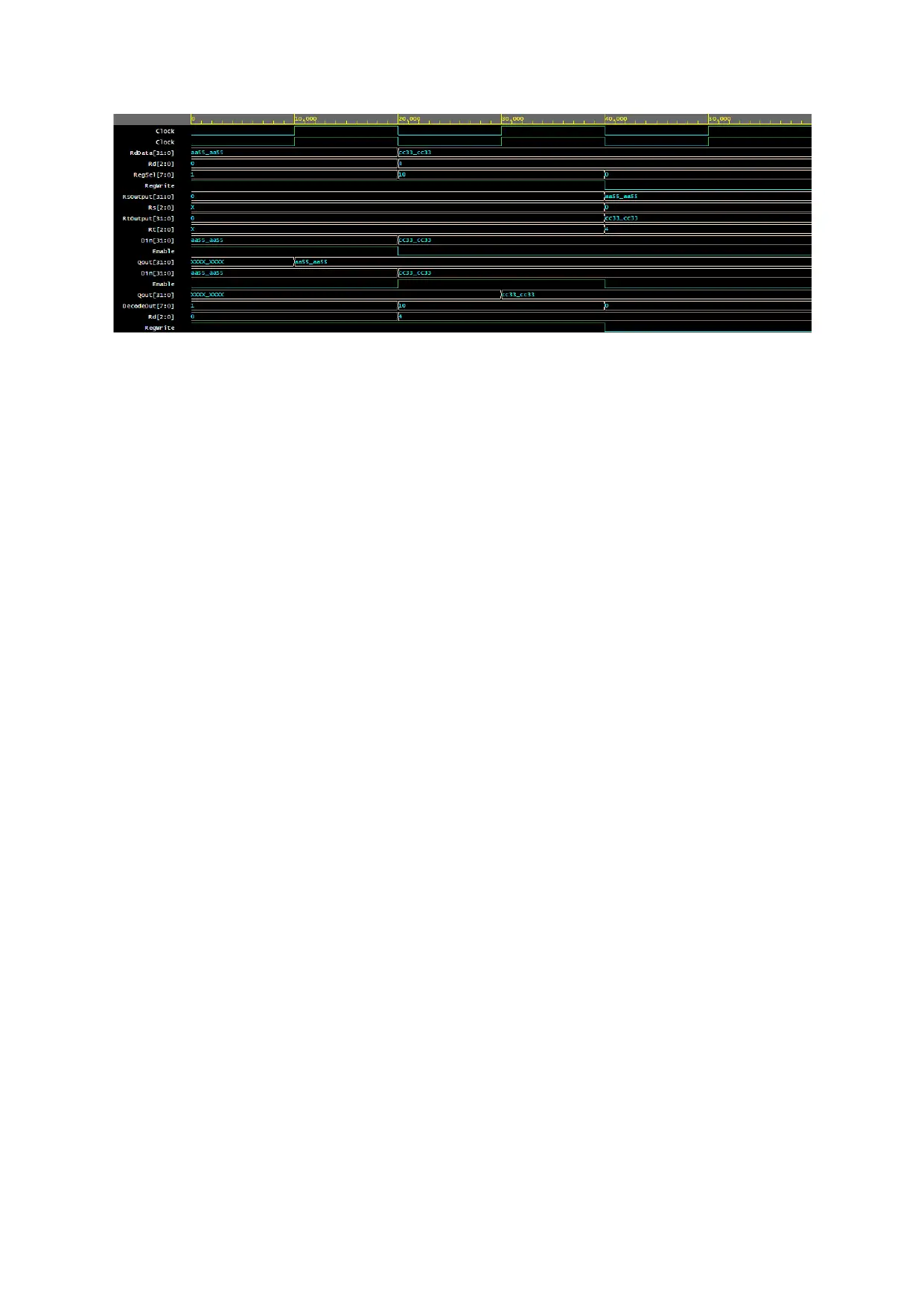

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)