Electrical Engineering Assignment: Data Representation and Logic

VerifiedAdded on 2020/03/28

|4

|561

|390

Homework Assignment

AI Summary

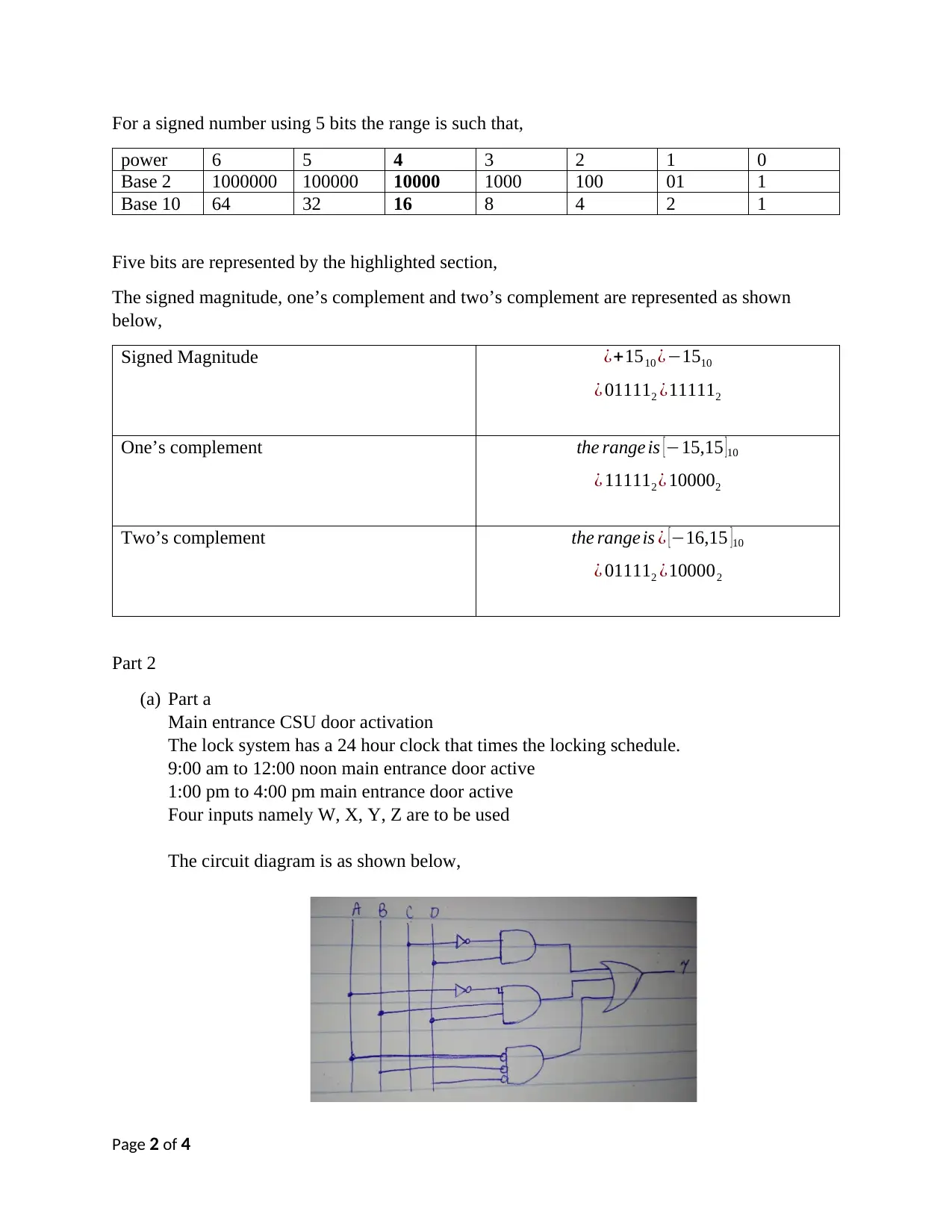

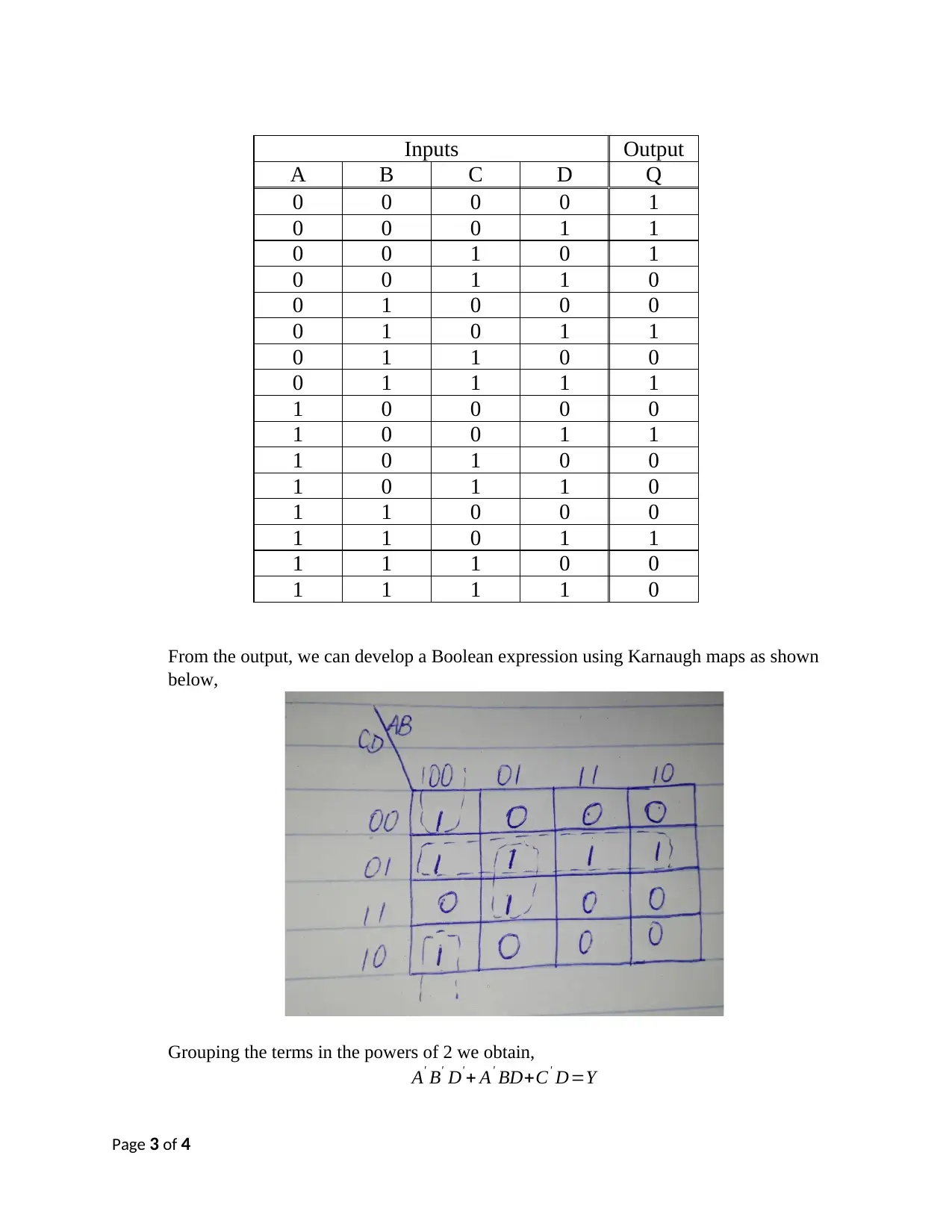

This document presents a comprehensive solution to a data representation and digital logic assignment. The solution includes an explanation of number conversions, specifically focusing on IEEE-754 representation and signed number systems using 5 bits. It covers signed magnitude, one's complement, and two's complement representations. The assignment also addresses a practical circuit design problem involving a main entrance door activation system with a 24-hour clock and four inputs. A truth table and Karnaugh map are used to derive a Boolean expression for the circuit. The solution further demonstrates the simplification of a Boolean expression using Boolean algebra identities, providing detailed steps and justifications for each simplification. The assignment covers several key concepts within digital logic and data representation, making it a valuable resource for students studying electrical engineering or related fields.

1 out of 4

![[object Object]](/_next/static/media/star-bottom.7253800d.svg)