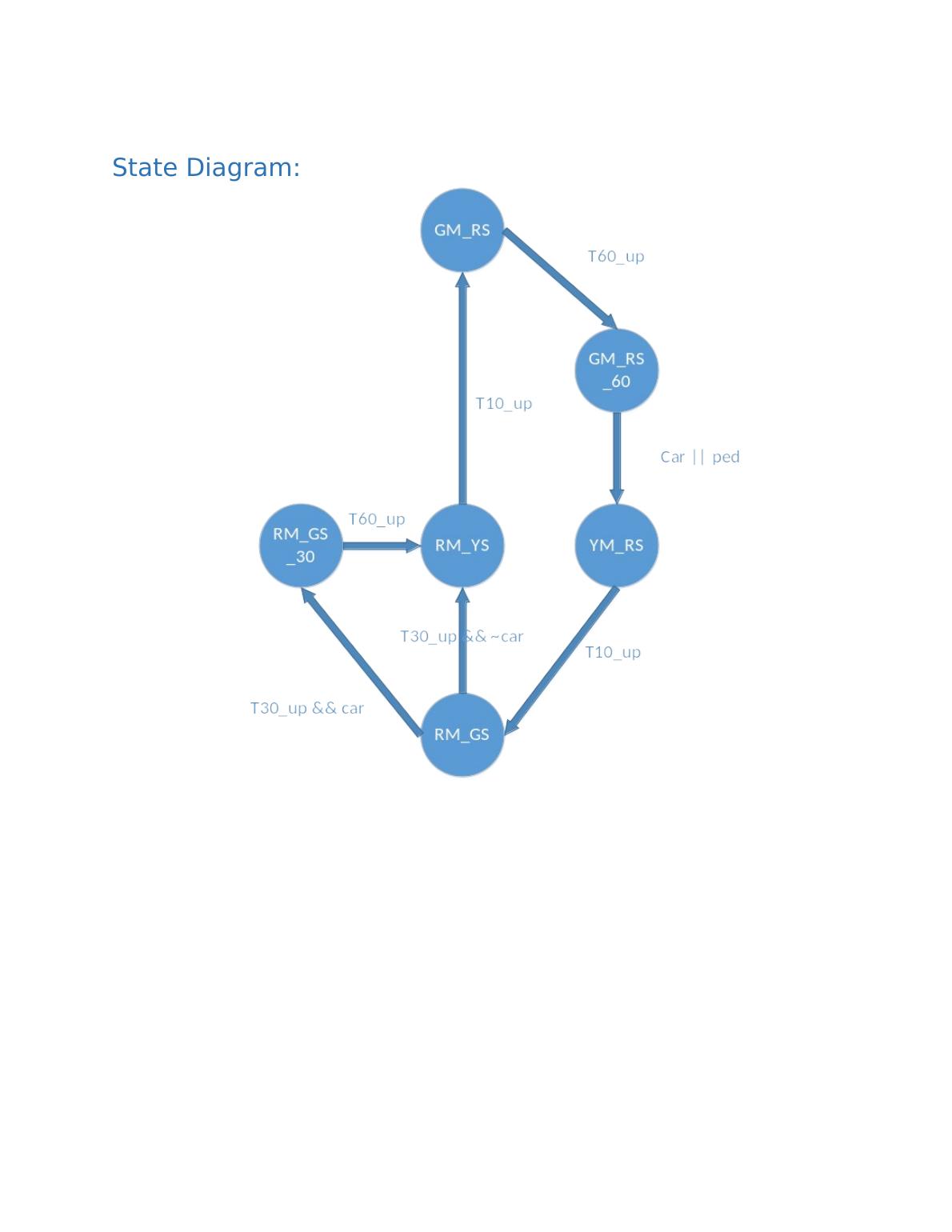

State Diagram:.

Design a traffic light controller for an intersection between a Main Road and a Side Street, including state diagram, implementation, and verification.

13 Pages839 Words100 Views

Added on 2023-04-06

State Diagram:.

Design a traffic light controller for an intersection between a Main Road and a Side Street, including state diagram, implementation, and verification.

Added on 2023-04-06

ShareRelated Documents

End of preview

Want to access all the pages? Upload your documents or become a member.

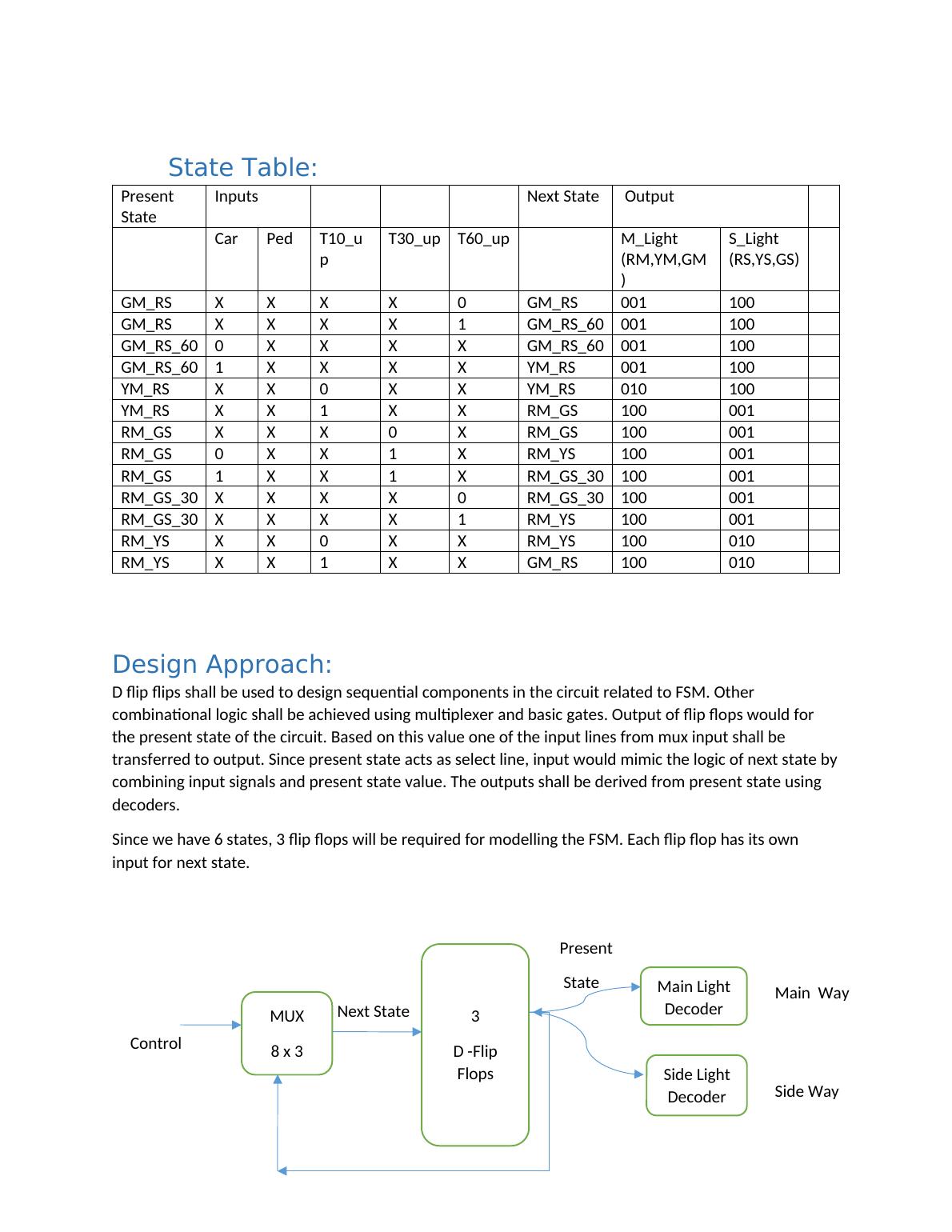

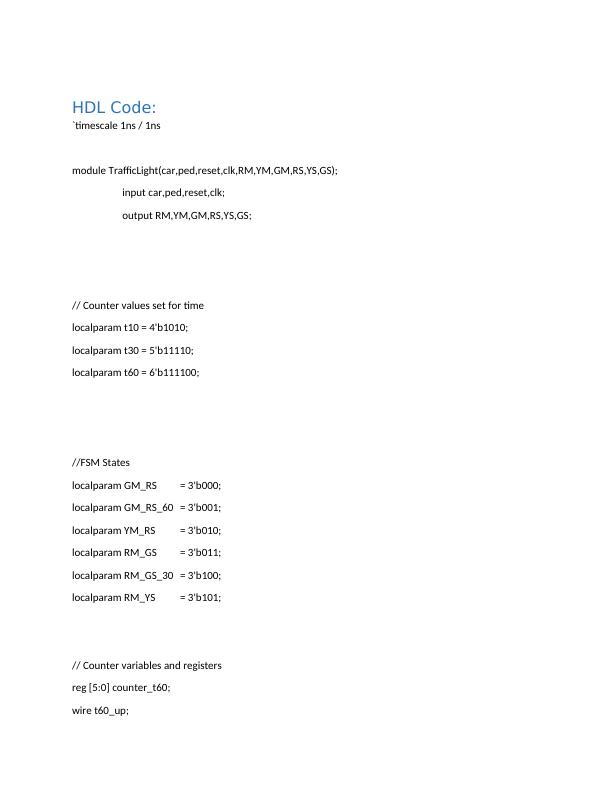

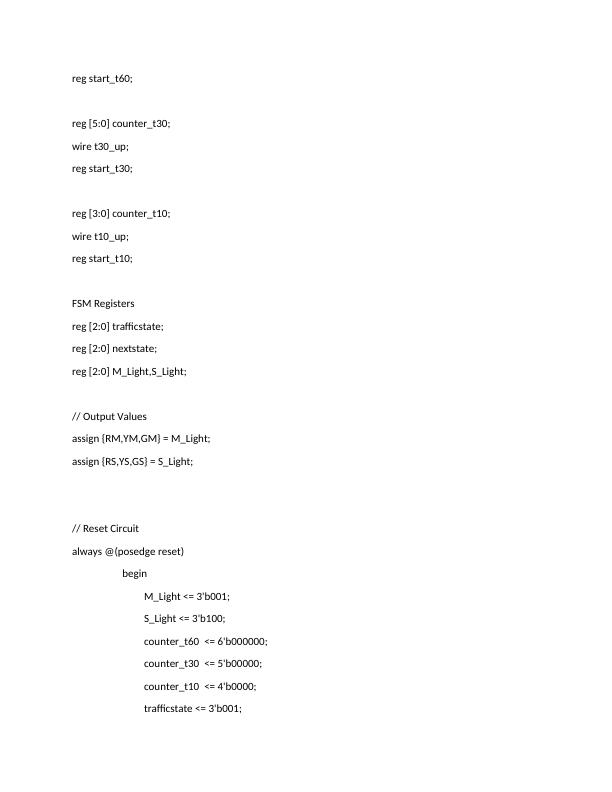

Traffic Light Controller Implementation

|11

|1543

|154

VHDL Assignment: Register File Implementation in VHDL

|4

|928

|211